Einführung in Verilog

Verilog ist eine Art Hardwarebeschreibungssprache (HDL). Verilog ist eine der beiden Sprachen, die von Bildung und Wirtschaft zum Entwerfen von FPGAs und ASICs verwendet werden. Wenn Sie mit der Funktionsweise von FPGAs und ASICs nicht vertraut sind, sollten Sie diese Seite für eine Einführung in FPGAs und ASICs lesen. Verilog und VHDL sind die beiden am häufigsten verwendeten HDLs. Im Vergleich zu traditionellen Softwaresprachen wie Java oder C funktioniert Verilog ganz anders. Beginnen wir mit einem einfachen Beispiel.

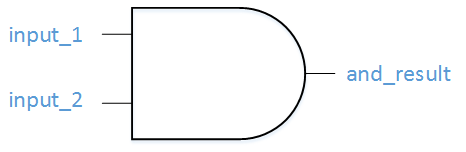

Zuerst erstellen wir eine Verilog-Datei, die beschreibt ein Und-Tor. Zur Auffrischung:Ein einfaches Und-Gatter hat zwei Eingänge und einen Ausgang. Der Ausgang ist nur dann gleich 1, wenn beide Eingänge gleich 1 sind. Unten sehen Sie ein Bild des Und-Gatters, das wir mit Verilog beschreiben werden.

Ein Und-Tor

Ein Und-Tor Lasst uns anfangen! Eine grundlegende Einheit von Verilog wird Draht genannt. Nehmen wir fürs Erste an, dass eine Verbindung nur eine 0 oder eine 1 sein kann. Hier ist einige grundlegende Verbindungslogik:

wire and_temp; assign and_temp = input_1 & input_2;

Wir erstellen eine Verbindung namens and_temp in der ersten Codezeile. In der zweiten Zeile des Codes nehmen wir den Draht, den wir erstellt haben, und weisen ihn zu das Kabel. Um es zuzuweisen, verwenden wir die boolesche UND-Funktion, die in Verilog das kaufmännische Und (&) ist. Wenn Sie den oben gezeigten Code beschreiben würden, könnten Sie sagen:„Das Signal and_temp erhält input_1 UND-verknüpft mit input_2."

Input_1 und Input_2 sind Eingaben für dieses Stück Verilog-Code. Lassen Sie uns die vollständige Liste der Ein- und Ausgänge zeigen. Dies geschieht im Modul Definition. Modul ist ein reserviertes Schlüsselwort in Verilog, das die Erstellung eines Codeblocks mit definierten Ein- und Ausgängen zeigt.

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

Dies ist Ihr Basismodul. Es definiert unser Modul namens example_and_gate und 3 Signale, 2 Eingänge und 1 Ausgang. Lassen Sie uns alles zusammenfügen, um die Datei fertigzustellen. Das einzige, was uns fehlt, ist die Zuweisung der Ausgabe and_result . Ein weiterer Hinweis, // in Verilog wird für einen Kommentar verwendet.

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

Herzliche Glückwünsche! Sie haben Ihre erste Verilog-Datei erstellt.

Scheint es, als müssten Sie viel Code schreiben, nur um ein Dummes und Gate zu erstellen? Erstens, und Tore sind nicht dumm. Zweitens haben Sie Recht, HDLs benötigen viel Code, um relativ einfache Aufgaben zu erledigen. Sie können sich mit der Tatsache trösten, dass Verilog zumindest weniger ausführlich ist als VHDL. Gewöhnen Sie sich an die Tatsache, dass etwas, das in der Software sehr einfach war, in einem HDL wie Verilog oder VHDL erheblich länger dauert. Aber bitten Sie einfach einen Software-Typen, zu versuchen, ein Bild auf einem VGA-Monitor zu erzeugen, das Conways Spiel des Lebens anzeigt, und sehen Sie zu, wie ihnen staunend der Kopf schwirrt! Das Video wird übrigens mit einem FPGA erstellt. Das wirst du schon früh genug können!

Verilog