Lernprogramm - Einführung in VHDL

VHDL ist ein schreckliches Akronym. Es steht für V HSIC H Hardware D Beschreibung L Sprache. Ein Akronym in einem Akronym, genial! VHSIC steht für V ery H hohes S pinkelte ich integriertes C Schaltung. Daher ist VHDL expandiert V ery High Speed Integrated Circuit H Hardware D Beschreibung L Sprache. Puh, das ist ein Schluck. VHDL ist eine der beiden Sprachen, die von Bildung und Wirtschaft zum Entwerfen von FPGAs und ASICs verwendet werden. Sie könnten zunächst von einer Einführung in FPGAs und ASICs profitieren, wenn Sie mit diesen faszinierenden Schaltungsteilen nicht vertraut sind. VHDL und Verilog sind die beiden Sprachen, die Digitaldesigner verwenden, um ihre Schaltungen zu beschreiben, und sie unterscheiden sich vom Design her von Ihren traditionellen Softwaresprachen wie C und Java.

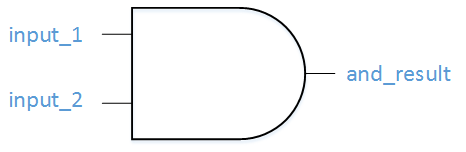

Für das folgende Beispiel erstellen wir eine VHDL-Datei, die beschreibt ein Und-Tor. Zur Auffrischung:Ein einfaches Und-Gatter hat zwei Eingänge und einen Ausgang. Der Ausgang ist nur dann gleich 1, wenn beide Eingänge gleich 1 sind. Unten sehen Sie ein Bild des Und-Gatters, das wir mit VHDL beschreiben werden.

Ein Und-Tor

Ein Und-Tor Lasst uns anfangen! Die grundlegende Einheit von VHDL wird als Signal bezeichnet . Nehmen wir zunächst an, dass ein Signal entweder eine 0 oder eine 1 sein kann (es gibt tatsächlich andere Möglichkeiten, aber dazu kommen wir noch). Hier ist einige grundlegende VHDL-Logik:

signal and_gate : std_logic; and_gate <= input_1 and input_2;

Die erste Codezeile definiert ein Signal vom Typ std_logic und heißt and_gate. Std_logic ist der Typ, der am häufigsten zum Definieren von Signalen verwendet wird, aber es gibt noch andere, die Sie kennenlernen werden. Dieser Code generiert ein UND-Gatter mit einem einzigen Ausgang (and_gate) und 2 Eingängen (input_1 und input_2). Das Schlüsselwort „and“ ist in VHDL reserviert. Der Operator <=ist als Zuweisungsoperator bekannt. Wenn Sie den obigen Code verbal parsen, können Sie laut sagen:„Das Signal and_gate ERHALTEN input_1 und-ed mit input_2.“

Jetzt fragen Sie sich vielleicht, woher input_1 und input_2 kommen. Nun, wie ihr Name schon sagt, sind sie Eingaben für diese Datei, also müssen Sie die Tools darüber informieren. Eingaben und Ausgaben in eine Datei werden in einer Entität definiert . Eine Entität enthält einen Port, der alle Eingaben und Ausgaben in eine Datei definiert. Lassen Sie uns eine einfache Entität erstellen:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

Dies ist Ihre grundlegende Entität. Es definiert eine Entität namens example_and und 3 Signale, 2 Eingänge und 1 Ausgang, die alle vom Typ std_logic sind. Ein weiteres VHDL-Schlüsselwort wird benötigt, um dies zu vervollständigen, und das ist architecture . Eine Architektur wird verwendet, um die Funktionalität einer bestimmten Entität zu beschreiben. Stellen Sie es sich wie ein Thesenpapier vor:Die Entität ist das Inhaltsverzeichnis und die Architektur ist der Inhalt. Lassen Sie uns eine Architektur für diese Entität erstellen:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

Der obige Code definiert eine Architektur namens rtl der Entität example_and. Alle Signale, die von der Architektur verwendet werden, müssen zwischen den Schlüsselwörtern „is“ und „begin“ definiert werden. Die eigentliche Architekturlogik liegt zwischen den Schlüsselwörtern „begin“ und „end“. Sie sind mit dieser Datei fast fertig. Eine letzte Sache, die Sie den Tools mitteilen müssen, ist, welche Bibliothek verwendet werden soll. Eine Bibliothek definiert, wie sich bestimmte Schlüsselwörter in Ihrer Datei verhalten. Gehen Sie für den Moment davon aus, dass Sie diese beiden Zeilen oben in Ihrer Datei haben müssen:

library ieee; use ieee.std_logic_1164.all;

Herzliche Glückwünsche! Sie haben Ihre erste VHDL-Datei erstellt. Sie können die fertige Datei hier sehen:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

Scheint es, als müssten Sie viel Code schreiben, nur um ein Dummes und Gate zu erstellen? Erstens, und Tore sind nicht dumm. Zweitens haben Sie recht; VHDL ist eine sehr ausführliche Sprache. Gewöhnen Sie sich an die Tatsache, dass etwas, das in der Software sehr einfach war, in einem HDL wie Verilog oder VHDL erheblich länger dauert. Aber bitten Sie einfach einen Software-Typen, zu versuchen, ein Bild auf einem VGA-Monitor zu erzeugen, das Conways Spiel des Lebens anzeigt, und sehen Sie zu, wie ihnen staunend der Kopf schwirrt! Das Video wird übrigens mit VHDL und einem FPGA erstellt. Das wirst du schon früh genug können!

VHDL

- Aufzeichnungen - VHDL-Beispiel

- Eine Einführung in die Stereolithographie (SLA)

- Eine Einführung in die Titanlegierung

- Einführung in Gleichstromkreise

- Einführung in Wechselstromkreise

- Einführung in SPICE

- C-Tutorial

- Verilog-Tutorial

- Einführung in Harmonische:Teil 1

- Einführung in SINUMERIK 808D – Video-Tutorial Drehen Teil 1