Embedded Design mit FPGAs:Implementierungssprachen

Anmerkung des Herausgebers:Da immer fortschrittlichere Algorithmen für intelligente Produktdesigns entstehen, haben Entwickler oft Schwierigkeiten, eingebettete Systeme zu implementieren, die die entsprechenden Verarbeitungsanforderungen dieser Algorithmen erfüllen. FPGAs können die erforderliche Leistung liefern, aber das Entwerfen mit FPGAs galt lange Zeit als auf FPGA-Programmierexperten beschränkt. Heute jedoch hat die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Entwicklungsumgebungen die FPGA-Entwicklung allgemein zugänglich gemacht. In diesem Auszug, Kapitel 4 aus dem Buch Architecting High-Performance Embedded Systems, bietet der Autor einen umfassenden Überblick über FPGA-Geräte, Implementierungssprachen und den FPGA-Entwicklungsprozess sowie eine detaillierte Anleitung, wie Sie mit der Implementierung eigener FPGAs beginnen können Entwurf. Der vollständige Auszug wird in der folgenden Reihe von Raten präsentiert:

Anmerkung des Herausgebers:Da immer fortschrittlichere Algorithmen für intelligente Produktdesigns entstehen, haben Entwickler oft Schwierigkeiten, eingebettete Systeme zu implementieren, die die entsprechenden Verarbeitungsanforderungen dieser Algorithmen erfüllen. FPGAs können die erforderliche Leistung liefern, aber das Entwerfen mit FPGAs galt lange Zeit als auf FPGA-Programmierexperten beschränkt. Heute jedoch hat die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Entwicklungsumgebungen die FPGA-Entwicklung allgemein zugänglich gemacht. In diesem Auszug, Kapitel 4 aus dem Buch Architecting High-Performance Embedded Systems, bietet der Autor einen umfassenden Überblick über FPGA-Geräte, Implementierungssprachen und den FPGA-Entwicklungsprozess sowie eine detaillierte Anleitung, wie Sie mit der Implementierung eigener FPGAs beginnen können Entwurf. Der vollständige Auszug wird in der folgenden Reihe von Raten präsentiert:

1:Hardwareressourcen

2:Implementierungssprachen (dieser Artikel)

3:Entwicklungsprozess

4:Ein Projekt erstellen

5:Implementierung

Übernommen aus Architecting High-Performance Embedded Systems, von Jim Ledin.

FPGA-Implementierungssprachen

Die Implementierung eines Designs für ein FPGA hängt letztendlich davon ab, eine oder mehrere softwareprogrammierungsähnliche Sprachen zu verwenden, um die Funktionalität des Geräts zu definieren.

Die traditionellen Sprachen für die FPGA-Entwicklung sind VHDL und Verilog.

FPGA-Entwicklungstools der aktuellen Generation unterstützen im Allgemeinen beide Sprachen zusammen mit der Möglichkeit, Systemkonfigurationen mithilfe von Blockschaltbildtechniken zu definieren. Einige Tool-Suiten unterstützen auch die Definition von FPGA-Funktionalität unter Verwendung der traditionellen Programmiersprachen C und C++.

VHDL

VHSIC-Hardwarebeschreibungssprache (VHDL ), wobei VHSIC für Sehr . steht Integrierter Hochgeschwindigkeits-Schaltkreis , hat eine Syntax, die an die Programmiersprache Ada erinnert. VHDL wurde ab 1983 unter der Leitung des US-Verteidigungsministeriums entwickelt.

Wie Ada neigt VHDL dazu, ziemlich ausführlich und starr strukturiert zu sein. In Bezug auf Programmiersprachen ist VHDL stark typisiert. Die Sprache enthält einen vordefinierten Satz von Basisdatentypen, hauptsächlich Boolean, Bit, Bit_Vector, Zeichen, String, Integer, Real, Time und Array. Alle anderen Datentypen werden in Bezug auf die Basistypen definiert.

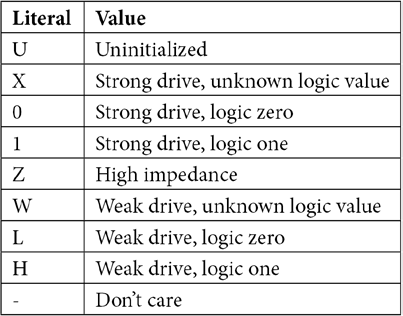

Eine Reihe von VHDL-Bibliotheken wurde vom Institut für Elektro- und Elektronikingenieure . definiert (IEEE ) und formalisiert als IEEE 1164-Standard, Multivalue Logic System für VHDL-Modell-Interoperabilität . Diese Bibliotheken definieren den Satz von Logikwerten, die in der VHDL-Sprache verwendet werden sollen. Diese Bibliothek enthält einen Typ namens std_logic, der ein 1-Bit-Signal darstellt. Die logischen Werte innerhalb des Typs std_logic werden durch die in der folgenden Tabelle aufgeführten Zeichenliterale dargestellt:

Die „starken“ 0- und 1-Werte in der vorherigen Abbildung stellen Signale dar, die in den angegebenen Binärzustand getrieben werden. Die „schwachen“ Signale stellen Signale dar, die auf einem Bus mit mehreren Treibern angesteuert werden, wobei sich jeder Treiber auf dem Bus behaupten kann und die anderen Treiber überschreibt. Der Z-Wert stellt einen CMOS-Ausgang im hochohmigen Zustand dar, bei dem der Ausgang, anstatt den Bus in einen Zustand 0 oder 1 zu treiben, stattdessen effektiv vom Bus getrennt wird und diesen überhaupt nicht ansteuert. Der U-Zustand stellt die Standardwerte für alle Signale dar. Bei der Schaltungssimulation wird jedes Signal im U-Zustand erkannt, was wahrscheinlich darauf hindeutet, dass ein nicht initialisierter Wert unbeabsichtigt verwendet wird. Der X-Zustand ist mit Drähten verknüpft, die keine Ausgänge haben, die sie ansteuern. Der Zustand – stellt unbenutzte Eingänge dar, daher spielt es keine Rolle, in welchem Zustand sie sich befinden.

VHDL-Schaltungsdesigns beginnen im Allgemeinen mit dem Importieren der IEEE 1164-Bibliotheken über die folgenden Anweisungen:

Bibliothek IEEE;

IEEE.std_logic_1164.all verwenden;

Wir werden VHDL in unserem Projektbeispiel später in diesem Kapitel verwenden. Dies soll keine starke Präferenz für VHDL gegenüber Verilog darstellen. Beide Hardware-Definitionssprachen sind vollständig in der Lage, praktisch jedes Design darzustellen, das für ein FPGA synthetisiert werden kann.

Verilog

Die Hardwarebeschreibungssprache von Verilog (HDL ) wurde 1984 eingeführt und 2005 als IEEE 1364 standardisiert. 2009 wurde der Verilog-Standard mit dem SystemVerilog kombiniert Standard, um den IEEE-Standard 1800-2009 zu erstellen. SystemVerilog enthält zusätzlich zu den in Verilog vorhandenen Hardware-Designfunktionen umfangreiche Möglichkeiten zur Durchführung der Systemverifizierung.

Verilog wurde entwickelt, um der Programmiersprache C zu ähneln, einschließlich ähnlicher Operatorrangfolge und der Verwendung einiger derselben Kontrollfluss-Schlüsselwörter, einschließlich if, else, for und while.

Verilog verwendet das Konzept einer Leitung Signalzustände darzustellen. Ein Signalwert kann einen der Werte 0, 1, egal (x) oder hohe Impedanz (z) annehmen und kann ein starkes . haben oder schwach Signalstärke.

Sowohl VHDL als auch Verilog definieren Sprachuntergruppen, die zum Entwerfen von Logikschaltungen verwendet werden können. Diese Teilmengen werden als synthetisierbare bezeichnet Sprachuntergruppen. Über die synthetisierbaren Teilmengen hinaus sind zusätzliche Sprachfunktionen verfügbar, um Aufgaben wie die Schaltungssimulation zu unterstützen. Wir werden später in diesem Kapitel ein Beispiel dafür sehen.

Nicht-synthetierbare Sprachkonstrukte verhalten sich eher wie traditionelle Software-Programmiersprachen. Beispielsweise durchläuft eine nicht synthetierbare for-Schleife einen Codeblock sequentiell so oft wie angegeben, genau wie in einer regulären Programmiersprache. Andererseits wird eine synthetisierbare for-Schleife effektiv entrollt, um eine Sammlung von replizierten Hardware-Konstrukten zu erzeugen, die parallel ausgeführt werden und jede Iteration der Schleife darstellen.

Blockdiagramme

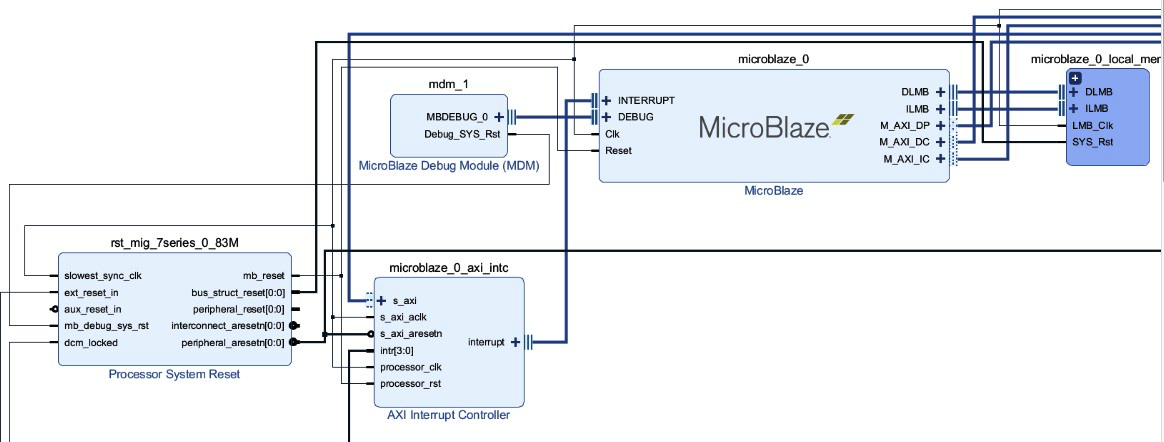

Auf einer Abstraktionsebene oberhalb der textbasierten HDLs unterstützen moderne FPGA-Entwicklungstool-Suiten die schnelle Konfiguration von Systemdesigns, die komplexe Logikkomponenten wie Mikroprozessoren und anspruchsvolle I/O-Geräte in einem Blockstrukturformat enthalten. Abbildung 4.2 ist ein Beispiel für einen Teil eines Blockdiagramms für ein Xilinx-FPGA-Design mit einem MicroBlaze-Softprozessor:

Klicken für Bild in voller Größe

Abbildung 4.2 – Blockschaltbild mit einem MicroBlaze-Soft-Mikroprozessor

Der MicroBlaze-Prozessor ist ein Prozessorkern, der mit der Xilinx Vivado-Toolsuite zur Verwendung in FPGA-Designs in Prozessorfamilien einschließlich Artix-7 bereitgestellt wird.

Während die Verwendung von Blockdiagrammen eine visuell intuitive Möglichkeit bietet, die Instanziierung und Verbindung komplexer Logikelemente in einem FPGA-Design zu organisieren, ist es wichtig, sich daran zu erinnern, dass das Entwicklungstool hinter dem Diagramm VHDL- oder Verilog-Code generiert, um die Komponenten und ihre Verbindungen. Das Blockdiagramm ist einfach eine Benutzeroberfläche zur Verwaltung der Konfiguration dieser Komponenten.

Nachdem Sie ein Blockdiagramm entwickelt haben, können Sie den generierten HDL-Code untersuchen, der in den mit dem Projekt verknüpften Dateien enthalten ist. Im Diagramm von Abbildung 4.2 , wird aus dem Diagramm eine Datei namens design_1_microblaze_0_0_stub.vhdl erzeugt. Diese Datei beginnt mit dem folgenden VHDL-Code:

Bibliothek IEEE;

IEEE.STD_LOGIC_1164.ALL verwenden;

Entity Design_1_microblaze_0_0 ist

Hafen (

Clk:in STD_LOGIC;

Zurücksetzen:in STD_LOGIC;

Interrupt:in STD_LOGIC;

Interrupt_Address:in STD_LOGIC_VECTOR (0 bis 31);

Interrupt_Ack:out STD_LOGIC_VECTOR (0 bis 1);

Instr_Addr:out STD_LOGIC_VECTOR (0 bis 31);

Instr:in STD_LOGIC_VECTOR (0 bis 31);

Dieser Code beginnt mit einem Verweis auf die IEEE 1164-Standardbibliothek und definiert dann eine Schnittstelle zum MicroBlaze-Prozessor, die die Signale bereitstellt, die Sie von einem Mikroprozessor erwarten würden, einschließlich Systemtakt, Reset, Interrupt-Anforderung und Interrupt-Vektor-Eingänge; Unterbrechungsbestätigungs- und Befehlsadressenausgänge; und ein Bus für die aus dem Speicher abgerufenen Anweisungen.

Dieser Code verwendet die IEEE 1164-Bibliotheksdatentypen für Single-Bit-Signale (STD_LOGIC) und für Multi-Bit-Bussignale (STD_LOGIC_VECTOR).

Der Code in der Auflistung definiert die Schnittstelle zum MicroBlaze-Prozessor, enthält jedoch nicht die HDL-Definition des Prozessors selbst. Komplexe HDL-Designs für Komponenten wie Mikroprozessoren gelten als wertvolles Geistiges Eigentum (IP ) und die kommerziellen Unternehmen, die diese Designs entwickeln, unternehmen häufig Schritte, um sicherzustellen, dass sie nicht ohne entsprechende Lizenzierung verwendet werden. Wenn Anbieter IP zur Verwendung durch ihre Kunden verteilen, kann es in einem kompilierten Format bereitgestellt werden, das für Endbenutzer undurchsichtig ist. Auf diese Weise können Benutzer das IP in ihre Designs integrieren, aber sie können das HDL, das zu ihrer Entwicklung verwendet wurde, nicht untersuchen. Dies ist konzeptionell ähnlich wie bei Softwareentwicklern, die eine Bibliothek in kompilierter Form veröffentlichen, aber den Quellcode nicht bereitstellen.

C/C++

Eine Reihe von Anbietern bieten Softwaretools an, die traditionelle High-Level-Programmiersprachen, oft C und C++, in HDL-Code zur Verwendung in der FPGA-Entwicklung übersetzen. Dieser Ansatz kann attraktiv sein, wenn Sie einen komplexen Algorithmus in C oder C++ haben, den Sie in einer FPGA-Implementierung beschleunigen möchten. Diese Tools ermöglichen es auch Softwareentwicklern, die mit C/C++ vertraut sind, sofort mit der Implementierung von Code für die FPGA-Nutzung zu beginnen, ohne eine der HDLs erlernen zu müssen.

Während FPGA-Entwicklungstools für diese High-Level-Sprachen in der Lage sind, die resultierende FPGA-Implementierung des C/C++-Codealgorithmus erheblich zu optimieren, besteht dennoch eine gewisse Diskrepanz darin, dass das C/C++-Ausführungsmodell die sequentielle Ausführung von Anweisungen beinhaltet, während die native FPGA-Umgebung besteht aus parallelen Hardwarekomponenten. Das aus C/C++-Code resultierende FPGA-Design ähnelt normalerweise einer Sammlung von Zustandsautomaten, die die sequentielle Ausführung der in den Anweisungen der Programmiersprache definierten Operationen verwalten. Abhängig von der Verfügbarkeit von Möglichkeiten zur parallelen Ausführung innerhalb des C/C++-Codes kann eine FPGA-Implementierung eine erhebliche Leistungssteigerung im Vergleich zur Ausführung desselben Codes auf einem herkömmlichen Prozessor bieten.

In modernen FPGA-Entwicklungstool-Suiten können bei Bedarf alle in diesem Abschnitt beschriebenen Methoden der FPGA-Implementierung (VHDL, Verilog, Blockdiagramme und C/C++) in einem einzigen Design kombiniert werden. Aus diesem Grund möchte ein Teammitglied möglicherweise lieber in VHDL arbeiten, während ein anderes Verilog verwendet. Es mag Gründe für das Projektmanagement geben, die Multi-HDL-Nutzung innerhalb eines einzelnen Projekts abzuraten, aber die Sprachen selbst funktionieren problemlos in einem einzigen Design zusammen. Ein Grund, warum ein Projektmanager die Verwendung mehrerer HDLs vermeiden möchte, besteht darin, dass die zukünftige Aufrechterhaltung der Bemühungen die Teilnahme von Entwicklern mit Kenntnissen in beiden Sprachen erfordert.

Ebenso ist es möglich, eine High-Level-Architektur für ein Projekt in Form eines Blockdiagramms zu definieren und dann detaillierte Subsystem-Funktionalität mit dem HDL der Wahl zu implementieren. Im gleichen Design ist es auch möglich, aus einem C/C++-Algorithmus generiertes HDL zu integrieren. Architekten und Entwickler von eingebetteten Systemen sollten die Auswirkungen sorgfältig abwägen und die geeignete Implementierungsmethode für jeden Teil eines FPGA-Designs auswählen.

Im nächsten Abschnitt werden die Schritte im Standard-FPGA-Entwicklungsprozess vorgestellt.

Nachdruck mit Genehmigung von Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin ist CEO von Ledin Engineering, Inc. Jim ist ein Experte für Design, Entwicklung und Test von eingebetteter Software und Hardware. Er ist auch in der Cybersicherheitsbewertung von eingebetteten Systemen und in Penetrationstests versiert. Er hat einen B. S. Abschluss in Luft- und Raumfahrttechnik von der Iowa State University und einen M.S. Abschluss in Elektro- und Computertechnik vom Georgia Institute of Technology. Jim ist ein registrierter professioneller Elektroingenieur in Kalifornien, ein Certified Information System Security Professional (CISSP), ein Certified Ethical Hacker (CEH) und ein Certified Penetration Tester (CPT).

Jim Ledin ist CEO von Ledin Engineering, Inc. Jim ist ein Experte für Design, Entwicklung und Test von eingebetteter Software und Hardware. Er ist auch in der Cybersicherheitsbewertung von eingebetteten Systemen und in Penetrationstests versiert. Er hat einen B. S. Abschluss in Luft- und Raumfahrttechnik von der Iowa State University und einen M.S. Abschluss in Elektro- und Computertechnik vom Georgia Institute of Technology. Jim ist ein registrierter professioneller Elektroingenieur in Kalifornien, ein Certified Information System Security Professional (CISSP), ein Certified Ethical Hacker (CEH) und ein Certified Penetration Tester (CPT). Verwandte Inhalte:

- Embedded Design mit FPGAs:Hardwareressourcen

- Open-Source-Tools vereinfachen die FPGA-Programmierung

- Implementierung von Gleitkomma-Algorithmen in FPGAs oder ASICs

- Softwaretools migrieren GPU-Code auf FPGAs für KI-Anwendungen

- FPGAs ersetzen ASICs in den Vision-basierten ADAS von Subaru Eyesight

- Wie Flash-basierte FPGAs die Anforderungen an die funktionale Sicherheit vereinfachen

- Die Vorteile von Instant-on-FPGAs nutzen

- FPGA-Konfiguration mit Hochgeschwindigkeits-NOR-Flash

- Wie sich die FPGA-Technologie weiterentwickelt, um neue Systemanforderungen der mittleren Preisklasse zu erfüllen

Für mehr Embedded, abonnieren Sie den wöchentlichen E-Mail-Newsletter von Embedded.

Eingebettet

- Was ist eingebettete Systemprogrammierung und ihre Sprachen

- Was ist Embedded System Design:Schritte im Designprozess

- Umwandeln von Big Data in Smart Data mit eingebetteter KI

- Herausforderungen bei der Implementierung von USB-Typ-C-Ports und Designlösungen

- Schlüsseltrends der Branche prägen das Embedded Design

- FPGA-Beschleuniger für Embedded Vision MIPI-Kameras

- Clientron:multifunktionales POS-Terminal mit integriertem Drucker

- Design-Kit misst den Blutdruck mit optischem Sensor

- Defense FPGA-Debüts mit Early Access

- Alles drin mit Additiv