Embedded Design mit FPGAs:Implementierung

Die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Programmierumgebungen hat die Implementierung von FPGAs erleichtert allgemein zugänglich, aber die Verwendung von FPGAs kann entmutigend erscheinen.

Anmerkung des Herausgebers:Da immer fortschrittlichere Algorithmen für intelligente Produktdesigns entstehen, haben Entwickler oft Schwierigkeiten, eingebettete Systeme zu implementieren, die die entsprechenden Verarbeitungsanforderungen dieser Algorithmen erfüllen. FPGAs können die erforderliche Leistung liefern, aber das Entwerfen mit FPGAs galt lange Zeit als auf FPGA-Programmierexperten beschränkt. Heute jedoch hat die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Entwicklungsumgebungen die FPGA-Entwicklung allgemein zugänglich gemacht. In diesem Auszug, Kapitel 4 aus dem Buch Architecting High-Performance Embedded Systems, bietet der Autor einen umfassenden Überblick über FPGA-Geräte, Implementierungssprachen und den FPGA-Entwicklungsprozess sowie eine detaillierte Anleitung, wie Sie mit der Implementierung eigener FPGAs beginnen können Entwurf. Der vollständige Auszug wird in der folgenden Reihe von Raten präsentiert:

Anmerkung des Herausgebers:Da immer fortschrittlichere Algorithmen für intelligente Produktdesigns entstehen, haben Entwickler oft Schwierigkeiten, eingebettete Systeme zu implementieren, die die entsprechenden Verarbeitungsanforderungen dieser Algorithmen erfüllen. FPGAs können die erforderliche Leistung liefern, aber das Entwerfen mit FPGAs galt lange Zeit als auf FPGA-Programmierexperten beschränkt. Heute jedoch hat die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Entwicklungsumgebungen die FPGA-Entwicklung allgemein zugänglich gemacht. In diesem Auszug, Kapitel 4 aus dem Buch Architecting High-Performance Embedded Systems, bietet der Autor einen umfassenden Überblick über FPGA-Geräte, Implementierungssprachen und den FPGA-Entwicklungsprozess sowie eine detaillierte Anleitung, wie Sie mit der Implementierung eigener FPGAs beginnen können Entwurf. Der vollständige Auszug wird in der folgenden Reihe von Raten präsentiert:

1:Hardwareressourcen

2:Implementierungssprachen

3:Entwicklungsprozess

4:Erstellen eines Projekts

5:Implementierung (dieser Artikel)

Adaptiert aus Architecting High-Performance Embedded Systems, von Jim Ledin.

Testen des logischen Verhaltens

Es ist wichtig, das Verhalten der Logik mithilfe von Simulationen zu testen, bevor Sie versuchen, sie im FPGA auszuführen. Dies liegt daran, dass es in der Simulationsumgebung viel einfacher ist, Probleme zu erkennen und zu beheben als mit der Logik, die im FPGA ausgeführt wird. Die Simulationstools von Vivado können das Schaltungsverhalten sehr gut darstellen:

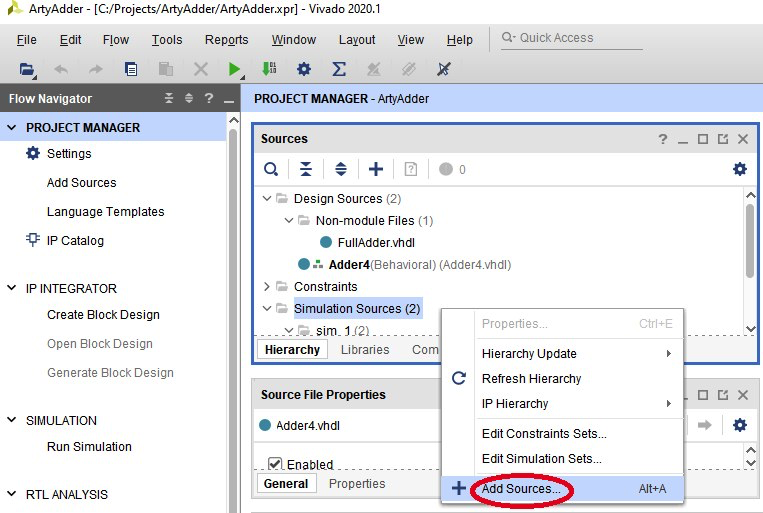

- In den Quellen Klicken Sie im Unterfenster mit der rechten Maustaste auf Simulationsquellen und wählen Sie Quellen hinzufügen… :

Abbildung 4.18 – Quellen hinzufügen… Menüauswahl für Simulationsquellen

- Im Quellen hinzufügen Dialogfeld, stellen Sie sicher, dass Simulationsquellen hinzufügen oder erstellen ausgewählt ist, klicken Sie dann auf Weiter .

- Im Simulationsquellen hinzufügen oder erstellen Klicken Sie im Dialogfeld auf Datei erstellen .

- Geben Sie den Dateinamen vhdl ein und klicken Sie auf OK .

- Klicken Sie auf Fertig stellen um das Simulationsquellen hinzufügen oder erstellen zu verwerfen Dialogfeld, und klicken Sie dann auf OK im Definieren-Modul Dialogfeld und klicken Sie auf Ja wenn Sie gefragt werden, ob Sie diese wirklich verwenden möchten

- Doppelklicken Sie auf Adder4 TestBench (Verhalten) (Adder4TestBench.vhdl) unter Simulationsquellen . Löschen Sie den automatisch ausgefüllten Inhalt des vhdl Editor-Fenster und geben Sie den folgenden Code in die Adder4TestBench.vhdl ein Herausgeber:

Dieser Code übt die 4-Bit-Addierer-Funktionalität aus, indem er jedem der A4 . alle Kombinationen von 4-Bit-Zahlen präsentiert und B4 Eingaben zum Adder4 Komponente. Es vergleicht die SUM4 und C_OUT4 Ausgaben des Adder4 Komponente zu unabhängig berechneten Werten für dieselben Eingaben. Nach jedem Additionsvorgang wird der Fehler Signal wird auf 0 gesetzt, wenn die Adder4 Ausgaben entsprachen den erwarteten Werten oder sind auf 1 . gesetzt wenn eine Abweichung vorliegt.

Der Code in Adder4TestBench.vhdl ähnelt traditionellem Softwarecode in der Art, wie er verschachtelte for-Schleifen verwendet, um alle Testeingabekombinationen auf den Adder4 . anzuwenden Komponente im Test. Code, der Tests im Simulationsmodus ausführt, ist nicht synthetisierbar, d. h. er stellt keine reine Hardware-Logikschaltung dar und ist in der Lage, traditionelle softwareähnliche Operationen durchzuführen, wie z. B. die iterative Ausführung von für Schleifen.

Wie in physikalischen Schaltungen können jedoch Signale, denen Werte im Prüfstandscode mit dem <=-Operator zugewiesen werden, nicht zum gleichen Zeitpunkt in nachfolgenden Ausdrücken verwendet werden. Dies liegt daran, dass die Simulationsumgebung die realen Auswirkungen der Ausbreitungsverzögerung darstellt, die selbst in winzigen FPGA-Geräten signifikant ist. Die drei warten 1 ns; Anweisungen im Prüfstandscode pausieren Schaltungsoperationen, um eine Ausbreitungsverzögerung zu ermöglichen. Diese Verzögerungen von 1 ns bieten Zeit für die berechneten Signalwerte kurz vor der Wartezeit -Anweisung zu propagieren, damit sie in der folgenden Anweisung verwendet werden können. Die letzte Wartezeit von 7 ns; -Anweisung in der inneren Schleife ist eine Pause, die es uns ermöglicht, die Ergebnisse jeder Iteration der Simulationsschleifen in der Signalverfolgungsanzeige klar zu sehen.

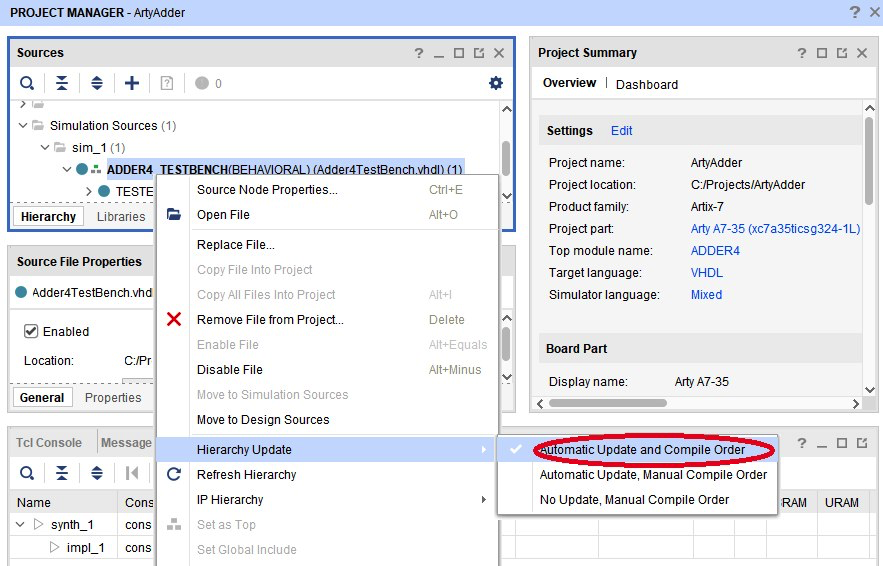

- Klicken Sie mit der rechten Maustaste auf Adder4 TestBench (Verhalten) (Adder4TestBench.vhdl) unter Simulationsquellen und wählen Sie Automatische Aktualisierung und Zusammenstellung der Bestellung . Dies setzt ADDER4_TESTBENCH als oberstes Objekt für den Simulationslauf:

Abbildung 4.19 – Menüauswahl zum Einstellen der automatischen Aktualisierungs- und Kompilierreihenfolge

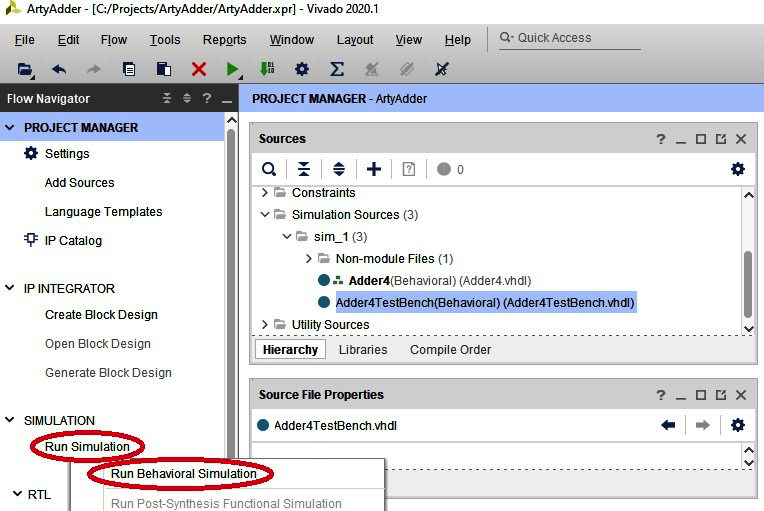

- Klicken Sie auf Simulation ausführen , dann Verhaltenssimulation ausführen im Flow Navigator Fenster, um in den Simulationsmodus zu wechseln. Wenn Sie die Editordateien noch nicht gespeichert haben, werden Sie dazu aufgefordert. Klicken Sie auf Speichern . Die Simulation wird dann ausgeführt:

Abbildung 4.20 – Menüauswahl Verhaltenssimulation ausführen

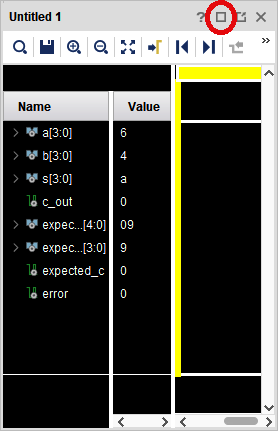

- Wenn die SIMULATION Wenn sich das Fenster öffnet, klicken Sie im Simulationsausgabefenster mit dem Titel Unbenannt 1 auf die Schaltfläche zum Maximieren :

Abbildung 4.21 – Simulationsergebnisfenster

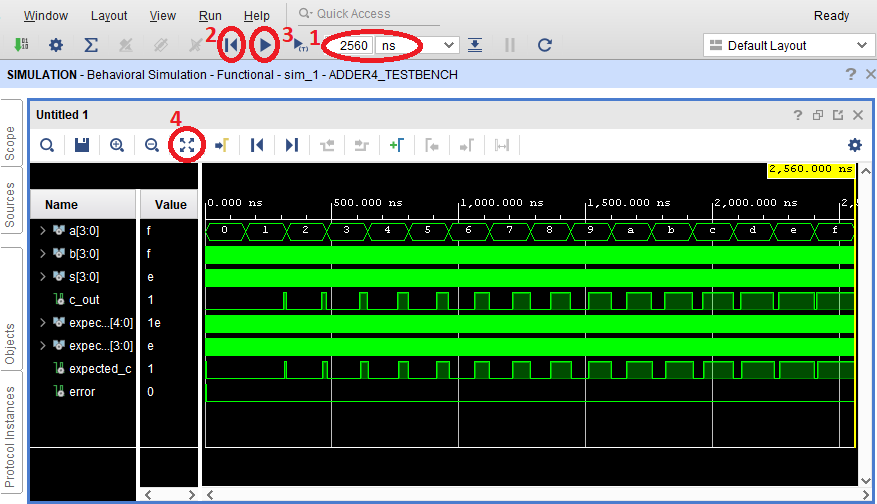

Die simulierte Gesamtzeit jedes Durchgangs durch die innere Schleife beträgt 10 ns. Weil es 256 Durchläufe durch die Schleife in Adder4TestBench.vhdl gibt , die Simulationszeit beträgt 2560 ns.

- Setzen Sie die Simulationslaufzeit in der oberen Symbolleiste auf 2560 ns (Schritt 1 in der folgenden Abbildung), drücken Sie die nach links zeigende Neustart-Taste (Schritt 2 ), dann drücken Sie die nach rechts zeigende Taste, um die Simulation 2560 ns lang auszuführen (Schritt 3 ) und drücken Sie schließlich die Zoom Fit (Schritt 4 ), um den Ausgabedatenbereich der Simulation so zu skalieren, dass er in das Fenster passt:

Abbildung 4.22 – Simulationsergebnisse vom Start bis zum Ende des Laufs

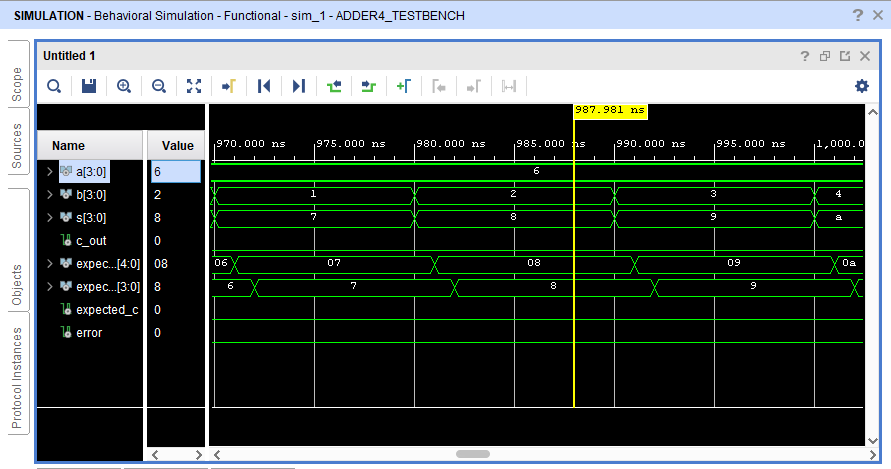

Sie können die Lupensymbole verwenden, um jeden Punkt der Kurve zu vergrößern und die Ergebnisse jeder während des Tests durchgeführten Additionsoperation zu beobachten. Die folgende Abbildung zeigt beispielsweise, dass die Dezimalwerte 6 und 2 addiert wurden, um das Ergebnis 8 mit einem Übertrag von 0 zu erhalten. Diese Werte stimmen mit den erwarteten Werten überein, was zu einem Fehler . führte auf 0 gesetzt werden. Der Fehler Signal ist 0 für alle 256 Testfälle, was anzeigt, dass unsere Logikschaltung alle Tests bestanden hat:

Abbildung 4.23 – Vergrößerte Ansicht der Simulationsergebnisse

- Schließen Sie den Simulationsmodus, indem Sie auf das X klicken im blauen SIMULATION Balken über der Datenverfolgung Klicken Sie auf OK wenn Sie gefragt werden, ob Sie die Simulation schließen möchten.

Nachdem wir die Verhaltenstests bestanden haben, werden wir die im Design verwendeten E/A-Signale definieren.

Definieren von I/O-Signalen

Unser nächster Schritt besteht darin, die Ein- und Ausgänge unserer Schaltung mit Hardwaregeräten auf dem Arty-Board zu verbinden. Die Eingänge sind die Schalter und Taster der Platine und die Ausgänge sind LEDs.

Die folgenden Schritte erstellen eine Einschränkungsdatei, die die I/O-Pins beschreibt, die wir auf dem FPGA-Gerät verwenden, und die Funktionen, die mit diesen Pins auf dem Arty-Board verbunden sind. Einschränkungsdateien haben die Erweiterung xdc:

- In den Quellen Klicken Sie im Unterfenster mit der rechten Maustaste auf Einschränkungen und wählen Sie Quellen hinzufügen… .

- Im Quellen hinzufügen Dialogfeld, stellen Sie sicher, dass Einschränkungen hinzufügen oder erstellen ausgewählt ist, klicken Sie dann auf Weiter .

- Im Einschränkungen hinzufügen oder erstellen Klicken Sie im Dialogfeld auf Datei erstellen .

- Geben Sie den Dateinamen Arty-A7-100.xdc ein (oder Arty-A7-35.xdc falls für Ihr Gerät geeignet) und klicken Sie auf OK .

- Klicken Sie auf Fertig stellen um das Hinzufügen oder Erstellen von Einschränkungen zu verwerfen

- Erweitern Sie die Einschränkungen Quellbaum und doppelklicken Sie auf Arty-A7-35.xdc .

- Digilent bietet vorgefertigte Einschränkungsdateien für die Arty A7-Boards Besuchen Sie https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-35-Master .xdc und kopieren Sie den gesamten Inhalt des Browserfensters in das Editorfenster Arty-A7-35.xdc in Vivado. Verwenden Sie ggf. die Datei unter https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-100-Master.xdc stattdessen.

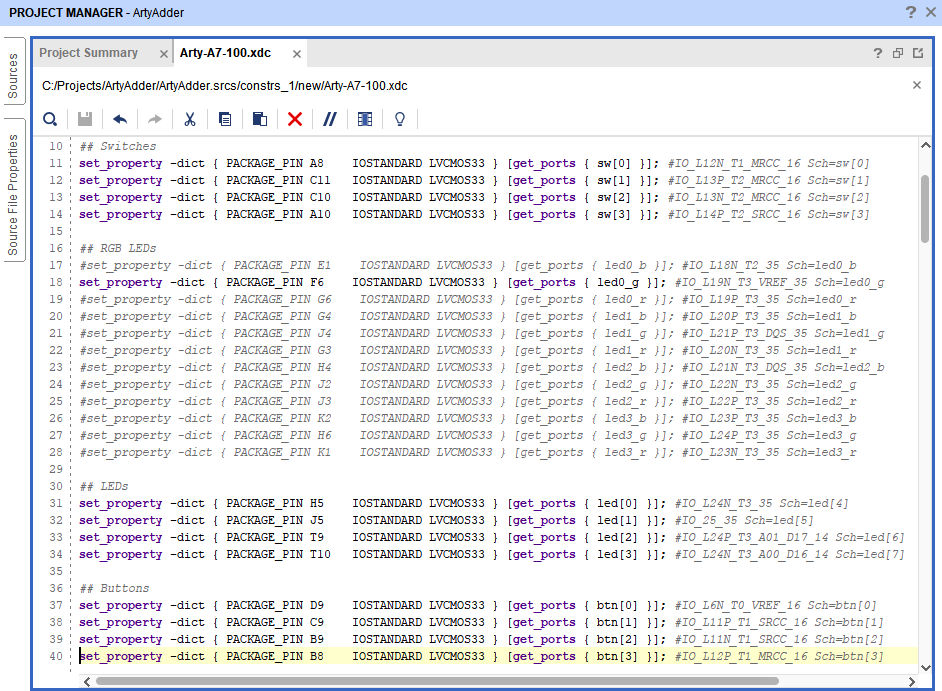

- Alle I/O-Pins werden in der Einschränkungsdatei auskommentiert, indem Sie die entsprechenden Zeilen in der Datei auskommentieren, indem Sie das #-Zeichen am Anfang jeder Zeile entfernen. Wir werden die in den folgenden Abschnitten aufgeführten Pins im Arty- . verwenden A7-100.xdc Datei:Schalter , RGB LEDs (aber nur led0_g , die erste grüne LED), LEDs , und Schaltflächen . Die folgende Abbildung zeigt diese Zeilen, nachdem sie auskommentiert wurden:

Abbildung 4.24 – Fenster des Einschränkungseditors

Im nächsten Abschnitt erstellen wir eine VHDL-Datei der obersten Ebene, die den Addierercode mit den E/A-Geräten verbindet.

Erstellen einer VHDL-Datei der obersten Ebene

Als nächstes erstellen wir eine VHDL-Datei der obersten Ebene, die unsere 4-Bit-Addiererkomponente mit den entsprechenden Board-E/A-Signalen verbindet:

- In den Quellen Klicken Sie im Unterfenster mit der rechten Maustaste auf Designquellen und wählen Sie Quellen hinzufügen… .

- Im Quellen hinzufügen Dialog, vergewissern Sie sich, dass Designquellen hinzufügen oder erstellen ausgewählt ist, klicken Sie dann auf Weiter .

- Im Designquellen hinzufügen oder erstellen Klicken Sie im Dialogfeld auf Datei erstellen .

- Geben Sie den Dateinamen vhdl ein und klicken Sie auf OK .

- Klicken Sie auf Fertig stellen um das Designquellen hinzufügen oder erstellen zu verwerfen Dialogfeld, und klicken Sie dann auf OK im Definieren-Modul Dialogfeld und klicken Sie auf Ja wenn Sie gefragt werden, ob Sie diese wirklich verwenden möchten

- Doppelklick vhdl unter Designquellen . Löschen Sie den automatisch ausgefüllten Inhalt der ArtyAdder.vhdl Editor-Fenster und geben Sie den folgenden Code in die ArtyAdder.vhdl ein Herausgeber:

-- Laden Sie die Standardbibliothekenbibliothek IEEE; use IEEE.STD_LOGIC_1164.ALL;entity ARTY_ADDER ist Port ( sw :in STD_LOGIC_VECTOR (3 bis 0); btn :in STD_LOGIC_VECTOR (3 bis 0); led :out STD_LOGIC_VECTOR (3 bis 0); led0_g :out STD_LOGIC ); ARTY_ADDER;ArchitekturVERHALTEN von ARTY_ADDER ist -- Verweis auf die vorherige Definition der 4-Bit-Addiererkomponente ADDER4 ist Port ( A4 :in std_logic_vector(3 bis 0); B4 :in std_logic_vector(3 bis 0); SUM4 :out std_logic_vector(3 downto 0); C_OUT4 :out std_logic ); end component;begin ADDER :ADDER4 port map ( A4 => sw, B4 => btn, SUM4 => led, C_OUT4 => led0_g );Endarchitektur VERHALTEN;

Dieser Code bildet die Signalnamen für die E/A-Geräte ab, die in Arty-A7-100.xdc . genannt werden als sw (4 Schalter), btn (4 Drucktasten), LED (4 einfarbige LEDs) und led0_g (der grüne Kanal der ersten mehrfarbigen LED) zum ADDER4 Ein- und Ausgänge.

Während bei VHDL die Groß-/Kleinschreibung nicht beachtet wird, ist die Verarbeitung von xdc Constraint-Dateien in Vivado unterscheidet zwischen Groß- und Kleinschreibung. Der Fall, der in E/A-Gerätenamen verwendet wird, die im xdc . definiert sind Datei muss identisch sein, wenn sie in einer VHDL-Datei referenziert wird. Insbesondere müssen die E/A-Signalnamen in VHDL in dieser Datei in Kleinbuchstaben geschrieben werden, da sie in der Einschränkungsdatei kleingeschrieben sind.

Wir sind jetzt bereit, unser Design für das Arty-Board zu synthetisieren, zu implementieren und zu programmieren.

Synthetisieren und Implementieren des FPGA-Bitstreams

Alternativ können Sie Bitstream generieren auswählen und Vivado führt alle erforderlichen Schritte durch, einschließlich Synthese, Implementierung und Bitstream-Generierung ohne weitere Benutzereingriffe. Wenn ein schwerwiegender Fehler auftritt, wird der Vorgang abgebrochen und Fehlermeldungen angezeigt. Führen Sie die folgenden Schritte aus, um den Bitstream zu generieren:

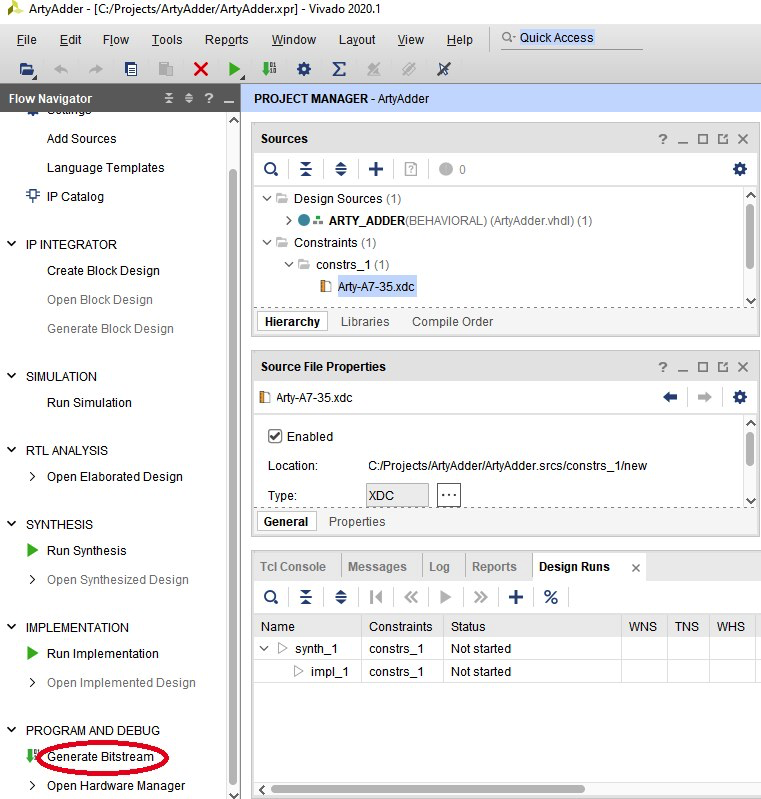

- Klicken Sie auf Bitstream generieren um den Build zu starten Möglicherweise werden Sie gefragt, ob Sie Texteditoren speichern möchten. Klicken Sie auf Speichern . Möglicherweise werden Sie darüber informiert, dass keine Implementierungsergebnisse verfügbar sind, und Sie werden gefragt, ob es in Ordnung ist, die Synthese und Implementierung zu starten. Klicken Sie auf Ja :

Abbildung 4.25 – Menüauswahl „Bitstream generieren“

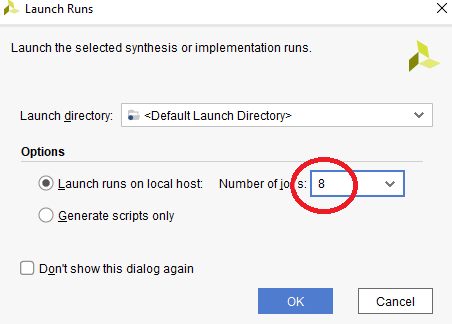

- Die Startläufe Dialog wird dann Sie können einen Wert für Anzahl Jobs auswählen bis zur Anzahl der Prozessorkerne in Ihrem Computer. Die Verwendung von mehr Kernen beschleunigt den Prozess, kann jedoch Ihren Computer blockieren, wenn Sie ihn während eines langwierigen Build-Prozesses weiter verwenden möchten. Klicken Sie auf OK um den Build zu starten:

Abbildung 4.26 – Dialogfeld "Läufe starten"

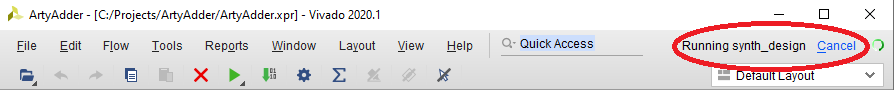

- Während des Build-Prozesses zeigt Vivado den Status in der oberen rechten Ecke des Hauptfensters an. Bei Bedarf können Sie den Build-Prozess abbrechen, indem Sie auf Abbrechen klicken neben der Statusanzeige:

Abbildung 4.27 – Anzeige des Zusammenstellungsstatus

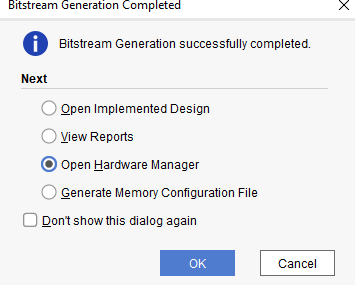

- Wenn der Build-Prozess abgeschlossen ist und keine schwerwiegenden Fehler aufgetreten sind, wird ein Bitstream-Generierung abgeschlossen dialog wird Obwohl andere Optionen angeboten werden, werden wir direkt mit dem Herunterladen des Bitstreams auf das Arty-Board fortfahren. Wählen Sie Hardware-Manager öffnen und klicken Sie auf OK :

Abbildung 4.28 – Dialog Bitstream-Generierung abgeschlossen

Als nächstes laden wir den Bitstream in das FPGA herunter.

Herunterladen des Bitstreams auf das Board

Führen Sie die folgenden Schritte aus, um den Bitstream auf ein Arty A7-Board herunterzuladen:

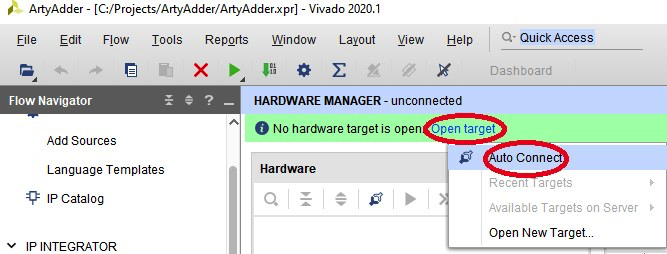

- Der HARDWARE-MANAGER Dialog erscheint und zeigt an, dass Kein Hardwareziel geöffnet ist .

- Verbinden Sie Ihr Arty A7-35- oder A7-100-Board über USB mit dem Computer. Warten Sie einige Sekunden, bis das Board erkannt wird, und klicken Sie dann auf Ziel öffnen , dann Automatisch verbinden :

Abbildung 4.29 – Offenes Ziel und Auto-Connect-Auswahl

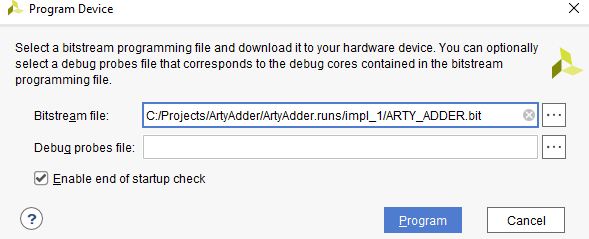

- Nach einigen Sekunden sollte Vivado anzeigen, dass das Board verbunden ist. Klicken Sie auf Gerät programmieren um den FPGA-Bitstream auf den Arty herunterzuladen Sie werden aufgefordert, eine Bitstream-Datei auszuwählen. Wenn Sie dieselbe Verzeichnisstruktur wie in diesem Beispiel verwendet haben, befindet sich die Datei unter C:/Projects/ArtyAdder/ ArtyAdder.runs/impl_1/ARTY_ADDER.bit :

Abbildung 4.30 – Dialogfeld Gerät programmieren

- Klicken Sie auf Programm um das Programm auf das FPGA-Gerät herunterzuladen und zu starten

- Sie können jetzt die Funktion des Programms mit dem Arty I/O testen. Stellen Sie alle vier Schalter in die Aus Position (Schalter zum angrenzenden Platinenrand bewegen) und keinen der vier Taster betätigen. Alle vier grünen LEDs sollten aus sein.

- Wenn Sie einen einzelnen Schalter einschalten oder einen Druckknopf drücken, sollte die entsprechende grüne LED aufleuchten. Wenn Sie eine beliebige Kombination von Schaltern einschalten, während Sie eine beliebige Anzahl von Drucktasten drücken, werden die entsprechenden 4-Bit-Zahlen addiert und die LEDs mit dem Aufleuchten Wenn ein Übertrag vorhanden ist (z. B. SW3 . einschalten) und drücken Sie BTN3 gleichzeitig), leuchtet die grüne Carry-LED.

Der hier durchgeführte Programmiervorgang speicherte das Programm im FPGA-RAM. Wenn Sie das FPGA-Board aus- und wieder einschalten, müssen Sie den Programmiervorgang wiederholen, um das Programm neu zu laden. Alternativ können Sie die FPGA-Konfigurationsdatei im Onboard-Flash-Speicher speichern, wie im folgenden Abschnitt beschrieben.

Programmieren des Bitstreams in den integrierten Flash-Speicher

Um das FPGA jedes Mal zu konfigurieren, wenn das Arty-Board mit Strom versorgt wird, muss die FPGA-Konfigurationsdatei im Flash-Speicher auf dem Board gespeichert werden. Wenn der MODE-Jumper installiert ist, versucht das FPGA, beim Einschalten eine Konfigurationsdatei vom Onboard-Flash-Speicher herunterzuladen. Dieser Speicher befindet sich in einem separaten Chip neben dem Artix-7 FPGA. Befolgen Sie diese Schritte, um die Konfigurationsdatei in den Flash-Speicher zu programmieren:

- Installieren Sie den MODUS Jumper auf dem Arty-Board, wenn es noch nicht drin ist

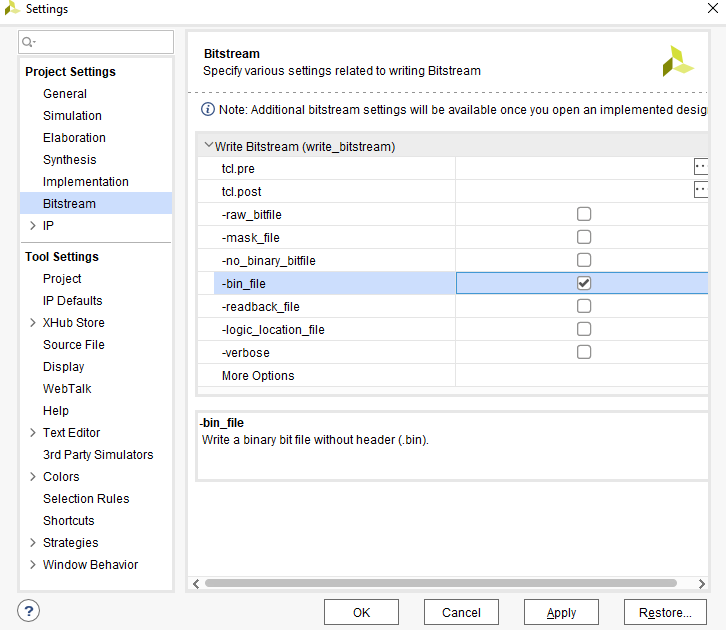

- Klicken Sie mit der rechten Maustaste auf Bitstream generieren und wählen Sie Bitstream-Einstellungen… .

- In den Einstellungen aktivieren Sie das Kontrollkästchen neben -bin_file und klicken Sie auf OK :

Abbildung 4.31 – Dialog für die Bitstream-Einstellungen

- Klicken Sie im Hauptdialog von Vivado auf Bitstream generieren und wiederholen Sie den Bitstrom-Erzeugungsprozess. Klicken Sie auf Abbrechen wenn die Bitstream-Generierung abgeschlossen Dialog

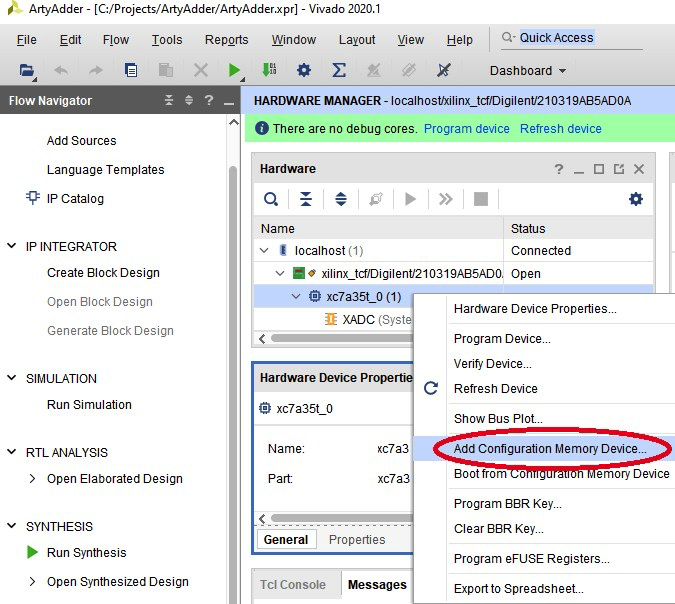

- In der Hardware Klicken Sie mit der rechten Maustaste auf die FPGA-Teilenummer (xc7a100t_0 ) und wählen Sie Konfigurationsspeichergerät hinzufügen… :

Abbildung 4.32 – Menüauswahl Konfigurationsspeichergerät hinzufügen…

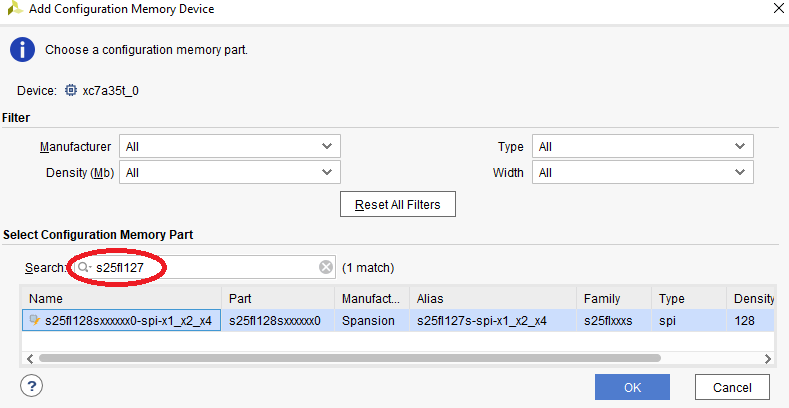

- Geben Sie s25fl127 ein in die Suche Dies sollte eine übereinstimmende Teilenummer hervorbringen. Wählen Sie das Teil aus und klicken Sie auf OK :

Abbildung 4.33 – Dialogfeld „Konfigurationsspeichergerät hinzufügen“

- Es wird ein Dialogfeld mit der Frage angezeigt, Möchten Sie das Konfigurationsspeichergerät jetzt programmieren? Klicken Sie auf OK .

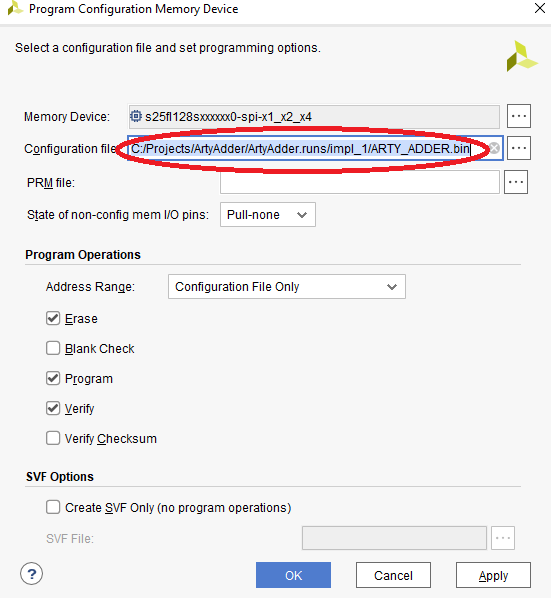

- Dies öffnet ein Speichergerät für die Programmkonfiguration Dialog, der den Namen der Konfigurationsdatei anfordert. Klicken Sie auf … Schaltfläche rechts neben Konfigurationsdatei und wählen Sie C:/Projects/ArtyAdder/ArtyAdder.runs/impl_1/ARTY_ADDER.bin. Klicken Sie auf OK :

Abbildung 4.34 – Dialogfeld „Programmkonfiguration Speichergerät“

- Der Programmiervorgang dauert einige Sekunden bis Sie eine Erfolgsmeldung erhalten, nachdem die Datei in den Board-Flash-Speicher programmiert wurde:

Abbildung 4.35 – Dialogfeld „Flash programmieren abgeschlossen“

Danach wird jedes Mal, wenn Sie die Stromversorgung der Platine aus- und wieder einschalten, das 4-Bit-Addiererprogramm geladen und ausgeführt. Es dauert lange, bis das Programm mit den Einstellungen geladen wird, die wir zum Laden der Konfigurationsdatei verwendet haben. Um zu vermeiden, dass das FPGA das Programm lädt, können Sie das Laden der Konfigurationsdatei beschleunigen, indem Sie die folgenden Schritte ausführen:

- Wählen Sie Offenes synthetisches Design im Flow Navigator .

- Wählen Sie im Vivado-Hauptmenü Extras/Geräteeigenschaften bearbeiten… .

- Im Allgemeinen Registerkarte Bitstream-Komprimierung aktivieren zu WAHR .

- In der Konfiguration Registerkarte Konfigurationsrate (MHz) einstellen bis 33 und klicken Sie dann auf OK .

- Generieren Sie den Bitstream erneut und programmieren Sie den Flash-Speicher wie beschrieben. Sie müssen den Konfigurationsspeicher entfernen und wieder hinzufügen, um die Option zur Neuprogrammierung anzuzeigen.

- Schließen Sie Hardware Manager .

- Ziehen Sie das USB-Kabel des Arty-Boards ab und stecken Sie es ein. Das Programm sollte beim Einschalten praktisch sofort starten.

In diesem Abschnitt wurde ein Beispiel für eine einfache kombinatorische Logik vorgestellt, die mit Signalen an den FPGA-I/O-Pins interagiert. Die Absicht hier war, Sie mit dem Vivado vertraut zu machen

Tool-Suite zu demonstrieren und zu demonstrieren, wie die Tools verwendet werden, um einen vollständigen FPGA-Entwicklungszyklus durchzuführen.

Zusammenfassung

Dieses Kapitel begann mit einer Diskussion über den effektiven Einsatz von FPGAs in Echtzeit-Embedded-Systemarchitekturen und wurde mit einer Beschreibung von Standard-FPGA-Geräten und den darin enthaltenen Low-Level-Komponenten fortgesetzt. Die Palette der FPGA-Designsprachen, einschließlich HDLs, Blockdiagrammmethoden und gängiger Softwareprogrammiersprachen wie C/C++, wurde vorgestellt. Ein Überblick über den FPGA-Entwicklungsprozess wurde vorgestellt. Das Kapitel endete mit einem vollständigen Beispiel eines FPGA-Entwicklungszyklus, beginnend mit einer Anforderungsbeschreibung und endend mit einem funktionalen System, das auf einem kostengünstigen FPGA-Entwicklungsboard implementiert ist.

Nachdem Sie dieses Kapitel abgeschlossen haben, sollten Sie wissen, wie FPGAs effektiv in Echtzeit-Embedded-Systemarchitekturen eingesetzt werden können, und die Komponenten innerhalb einer integrierten FPGA-Schaltung verstehen. Sie haben die Programmiersprachen, die beim Design von FPGA-Algorithmen verwendet werden, die Schritte im FPGA-Entwicklungszyklus kennengelernt und die Abfolge der Schritte im FPGA-Entwicklungsprozess verstanden.

Das nächste Kapitel wird den FPGA-Entwicklungsprozess erweitern, um einen vollständigen Ansatz für die Architektur eingebetteter Echtzeitsysteme mit FPGAs bereitzustellen. Es wird auch mit der Entwicklung eines Prototyps eines Hochleistungs-Embedded-Systems, eines digitalen Oszilloskops, beginnen, das als Beispiel für die folgenden Kapitel dienen wird.

Nachdruck mit Genehmigung von Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin ist CEO von Ledin Engineering, Inc. Jim ist ein Experte für Design, Entwicklung und Test von eingebetteter Software und Hardware. Er ist auch in der Cybersicherheitsbewertung von eingebetteten Systemen und in Penetrationstests versiert. Er hat einen B. S. Abschluss in Luft- und Raumfahrttechnik von der Iowa State University und einen M.S. Abschluss in Elektro- und Computertechnik vom Georgia Institute of Technology. Jim ist ein registrierter professioneller Elektroingenieur in Kalifornien, ein Certified Information System Security Professional (CISSP), ein Certified Ethical Hacker (CEH) und ein Certified Penetration Tester (CPT).

Jim Ledin ist CEO von Ledin Engineering, Inc. Jim ist ein Experte für Design, Entwicklung und Test von eingebetteter Software und Hardware. Er ist auch in der Cybersicherheitsbewertung von eingebetteten Systemen und in Penetrationstests versiert. Er hat einen B. S. Abschluss in Luft- und Raumfahrttechnik von der Iowa State University und einen M.S. Abschluss in Elektro- und Computertechnik vom Georgia Institute of Technology. Jim ist ein registrierter professioneller Elektroingenieur in Kalifornien, ein Certified Information System Security Professional (CISSP), ein Certified Ethical Hacker (CEH) und ein Certified Penetration Tester (CPT). Verwandte Inhalte:

- Embedded Design mit FPGAs:Hardwareressourcen

- Embedded Design mit FPGAs:Implementierungssprachen

- Embedded Design mit FPGAs:Entwicklungsprozess

- Open-Source-Tools vereinfachen die FPGA-Programmierung

- Implementierung von Gleitkomma-Algorithmen in FPGAs oder ASICs

- Einsatz von FPGAs für Deep Learning

- Softwaretools migrieren GPU-Code auf FPGAs für KI-Anwendungen

Für mehr Embedded, abonnieren Sie den wöchentlichen E-Mail-Newsletter von Embedded.

Eingebettet

- Was ist Embedded System Design:Schritte im Designprozess

- Endbearbeitung von 3D-gedruckten Teilen mit… Buntstiften?

- Experteninterview:Cheftechnologe von ANSYS zum Erfolg beim Metall-3D-Druck mit Simulation

- Umwandeln von Big Data in Smart Data mit eingebetteter KI

- Herausforderungen bei der Implementierung von USB-Typ-C-Ports und Designlösungen

- Schlüsseltrends der Branche prägen das Embedded Design

- Open-Source-Plattform zielt auf das IoT mit eingebettetem Linux ab

- Clientron:multifunktionales POS-Terminal mit integriertem Drucker

- Design-Kit misst den Blutdruck mit optischem Sensor

- Alles drin mit Additiv