Arm bietet neurale Verarbeitungs-IP für Anwendungsprozessoren

Arm hat eine neue Version seiner microNPU (Neural Processing Unit) IP entwickelt, die sich für den Einsatz neben Cortex-A-CPU-Kernen in Anwendungsprozessoren eignet. Der Hauptlizenznehmer NXP plant, diese IP in einer kommenden Familie von Anwendungsprozessoren zu verwenden, die KI-Anwendungen wie Posenschätzung, Mehrgesichtserkennung und Objekterkennung in Videos sowie Spracherkennung über die grundlegende Schlüsselworterkennung hinaus verarbeiten können.

Ethos-U65

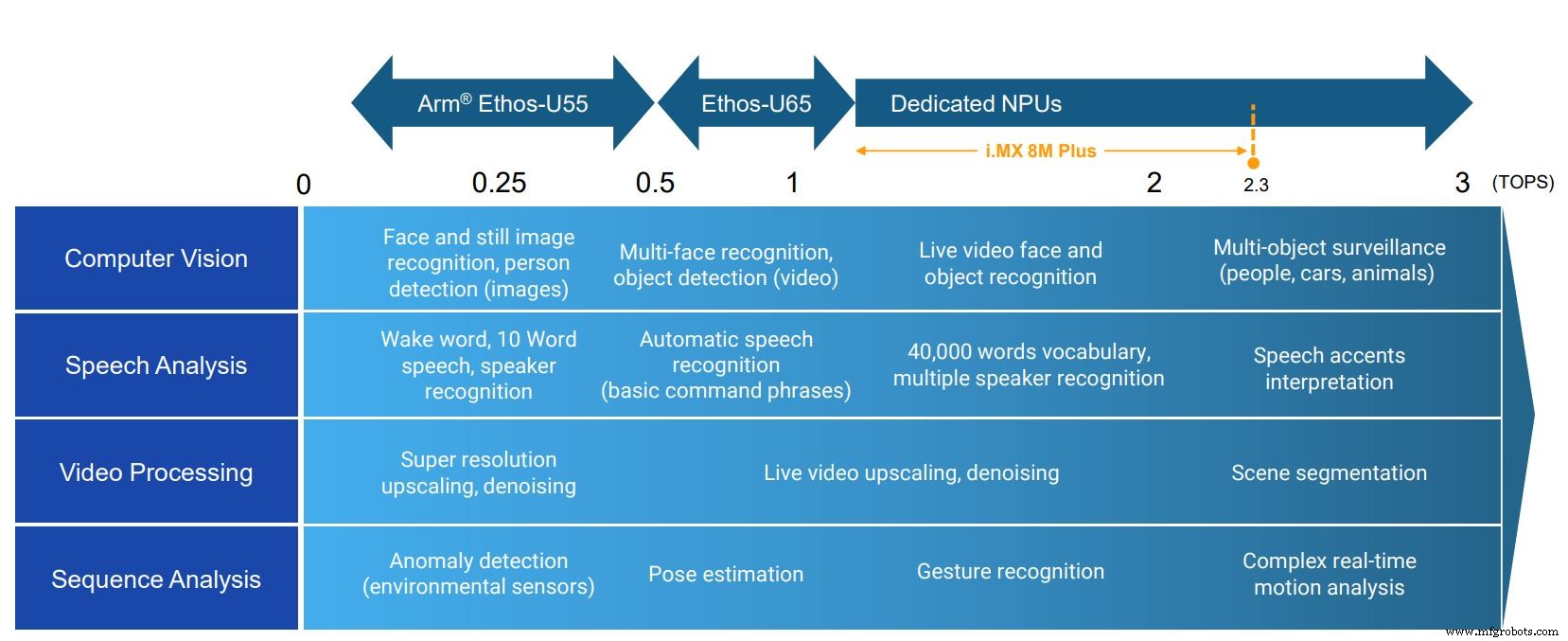

Arms bestehendes microNPU-Produkt Ethos-U55, das im Februar 2020 auf den Markt kam, zielt neben Cortex-M-Kernen auf Produkte der Mikrocontroller-Klasse ab. Es bietet bis zu 0,5 TOPS Beschleunigung (basierend auf kleineren Geometrien wie 16 oder 7 nm, bei 1 GHz) mit zwischen 3 und 256 Multiply-Accumulate-Units (MACs). Das Portfolio von Arm umfasst auch die Ethos-N77, N57 und N37, die jeweils 4, 2 und 1 TOPS bieten.

Der Ethos-U65 wurde entwickelt, um die Energieeffizienz des Ethos-U55 beizubehalten und gleichzeitig die verfügbaren MACs zu verdoppeln – bis zu 512 parallele MACs bei 1 GHz – für insgesamt 1 TOPS. Diese Kombination aus Leistung und Leistung ist speziell für die Verwendung zusammen mit Cortex-A-Kernen in Geräten der Anwendungsprozessorklasse vorgesehen. Die native Unterstützung der Ethos-U-Linie für ML-Operatoren wurde laut Arm ebenfalls aktualisiert und erweitert.

Hauptlizenznehmer

Führender Technologiepartner (und leitender Lizenznehmer) NXP arbeitete eng mit Arm an den definierenden Aspekten des Ethos-U65 auf Systemebene zusammen und hat angekündigt, das Ethos-U65 IP in seine nächste Generation von i.MX-Anwendungsprozessoren zu integrieren.

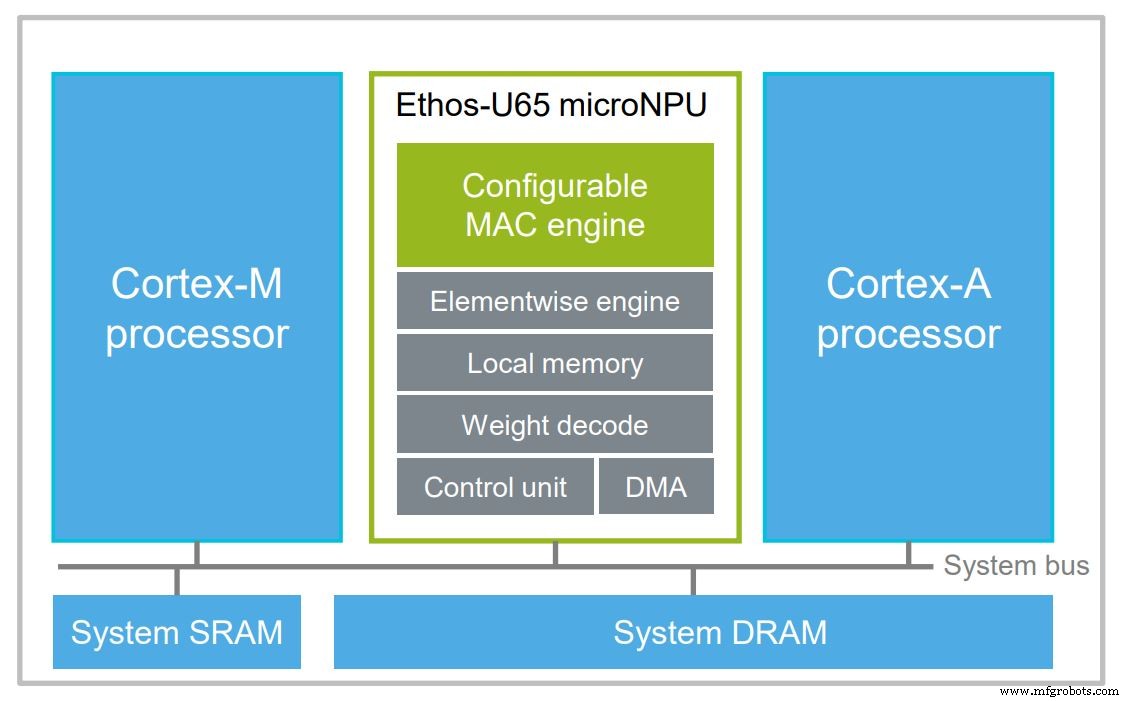

Die Architektur, die NXP für einen Anwendungsprozessor mit einer microNPU entwickelt hat, verwendet sowohl Cortex-A- als auch Cortex-M-Kerne (Bild:NXP)

Die Architektur, die NXP für einen KI-Anwendungsprozessor vorschwebt, sieht die Ethos-U65-microNPU neben Cortex-M- und Cortex-A-Kernen vor, erklärte Ben Eckermann, Chief Engineer of AI/ML Hardware, NXP. Der Cortex-A führt die Anwendung aus, handhabt Treiber für (beispielsweise) ein Mikrofon oder eine Kamera und stellt der NPU eine Arbeitslast bereit. Die microNPU und der Cortex-M berechnen die Arbeitslast des maschinellen Lernens und präsentieren die Antwort zurück an den Cortex-A.

„Genau wie ein Ethos-U55 ist [das Ethos-U65] auf einen Cortex-M-Prozessor angewiesen, der sich irgendwo in der Nähe des Systems befindet, nur für den Fall, dass es maschinelle Lernoperatoren aus dem neuronalen Netzwerk gibt, deren vollständige Auslagerung keinen Sinn ergibt.“ in der Hardware“, sagte Eckermann. „Es gibt viele Operatoren für maschinelles Lernen, die selten aufgerufen werden und eine reine Hardwareimplementierung nicht rechtfertigen.“

Die Flexibilität des Cortex-M in dieser Konfiguration ermöglicht auch eine gewisse Zukunftssicherheit, so Eckermann.

Der U65 verfügt über breitere interne Systembusse als der U55 und wurde auf die zusätzliche Pufferung und Latenz im Zusammenhang mit DRAM zugeschnitten (üblich in Systemen, die Anwendungsprozessoren verwenden, während Cortex-M-Systeme normalerweise SRAM verwenden).

Befüllen des Portfolios

NXP ergänzt sein Portfolio an KI-fähigen SoCs.

Die zuvor angekündigten i.MX 8M+-Anwendungsprozessoren des Unternehmens verfügen neben Dual- oder Quad-Cortex-A53-Kernen über einen NPU-KI-Beschleunigerblock. Die in diesen Produkten enthaltene NPU-IP stammt nicht von Arm. Es ist ein Verisilicon-Design, das 2,3 TOPS bietet, genug für Szenensegmentierung, Live-Video-Gesichts- und Objekterkennung oder Sprachakzentinterpretation. Am unteren Ende des Spektrums können die Mikrocontroller von NXP mit Arm Ethos-U55-NPUs Personenerkennung, Weckworterkennung und Video-Entrauschung handhaben.

Ethos-U65-fähige Produkte werden zwischen diesen beiden Produktkategorien angesiedelt sein und KI-Anwendungen wie Multi-Face-Erkennung, aufwändigere Spracherkennung oder Posenschätzung verarbeiten. Alle neuen Produkte in dieser Kategorie werden sich daher nicht mit dem i.MX 8M+ überschneiden, so Eckermann.

Der Rechenaufwand für verschiedene KI-Anwendungen (x-Achse) und die entsprechende NPU (Bild:NXP)

>> Dieser Artikel wurde ursprünglich veröffentlicht am unsere Schwesterseite EE Times.

Eingebettet

- Arm ermöglicht benutzerdefinierte Anweisungen für Cortex-M-Kerne

- Cervoz:ultradünner NVMe-Speicher für industrielle Embedded-Anwendungen

- CEVA:KI-Prozessor der zweiten Generation für tiefe neuronale Netzwerk-Workloads

- Multicore-Prozessor integriert neuronale Verarbeitungseinheit

- Spezialisierte Prozessoren beschleunigen Endpoint-KI-Workloads

- Induktiver Positionssensor für Industriemotoren bietet hohe Geschwindigkeit und hohe Genauigkeit

- Manhattan Skyline:kompakte ARM COM mit NXP i.MX 8MM

- Logiktechnologie:NXP iMX8M COM-Board für ARM Quad-Core

- LCE bietet Zuverlässigkeit für Manager

- Container-Builds für Arm auf x86