Ein Leitfaden zum Beschleunigen von Anwendungen mit genau richtigen benutzerdefinierten RISC-V-Anweisungen

Die offene Befehlssatzarchitektur (ISA) von RISC-V ermöglicht eine breite Flexibilität bei der Implementierung und bietet optionale Funktionen, die neue Ansätze zur Auflösung von Hardware-Software-Design-Kompromissen ermöglichen. Basierend auf einem modularen Aufbau kann der Basisprozessor als Ausgangspunkt mit einer Reihe von Standarderweiterungen und Optionen konfiguriert werden. Der wahre Wert liegt jedoch in den Möglichkeiten, die RISC-V Entwicklern bietet, um neue Erweiterungen, Anweisungen und Konfigurationen zu erstellen, die auf einzigartige Weise die Anforderungen ihrer innovativen Anwendungsideen erfüllen.

Die Softwareherausforderung für feste ISAs

Traditionell waren ISAs geistiges Eigentum (IP) kommerzieller Organisationen, die entweder Mikroprozessoren oder Mikrocontroller verkaufen oder ihre Designs für andere lizenzieren wollten. Embedded-Entwickler müssen Benchmarking-Software ausführen, um festzustellen, welche Lösung für ihre Anwendungsanforderungen am besten optimiert ist. Aufgrund der Kosten für die Entwicklung eines unabhängigen ISA mit dem gesamten notwendigen Ökosystem verließen sich Halbleiterhersteller zunehmend auf die standardmäßigen festen ISAs der Mainstream-IP-Anbieter, verließen sich auf das Moore'sche Gesetz und integrierte Peripheriegeräte, um Differenzierung zu ermöglichen, wie beispielsweise Ultra-Low-Power , an ihre Kunden.

Die Herausforderung hierbei besteht darin, dass die zum Ausführen von Code verwendeten Anweisungen nicht geändert werden können. Daher können Effizienzen, die beispielsweise durch eine optimierte Anweisung für einen Verschlüsselungsalgorithmus potenziell gewonnen werden könnten, nicht realisiert werden. Dies kann bedeuten, dass die Anwendung des Entwicklers zu langsam ist, möglicherweise zu viel Strom verbraucht oder regelmäßig einen harten Echtzeittermin in einem Regelkreis verpasst. Selbst mit dem besten Willen der Welt sind dies Faktoren, die allein durch Verbesserungen der Halbleiterfertigung oder Prozessverkürzungen nur schwer zu lösen sind.

Die RISC-V ISA begann als Projekt an der University of California, Berkeley und wird heute von der RISC-V International Association, einer gemeinnützigen Gruppe mit über 300 Mitgliedern, betreut. Diese tragen zu den ISA-Spezifikationen, Softwaretools wie Simulatoren und Compilern und dem Rest des Ökosystems bei, das zur Unterstützung eines solchen Vorhabens benötigt wird. Ob eine Nutzung sinnvoll ist oder nicht, hängt davon ab, ob einer von zwei Faktoren genutzt werden kann:Die Lizenzfreiheit oder die Freiheit, die sie bietet.

Offen und frei verfügbar bietet es eine grundlegende Verarbeitungsplattform, die sowohl von der Wissenschaft für Lehre und Forschung als auch für kommerzielle Anwendungen leicht genutzt werden kann. Eine offene ISA unterstützt auch eine Reihe von Geschäftsmodellen für Entwickler, die Halbleiter-IP beschaffen möchten, vom kommerziellen IP-Anbieter bis hin zu Open-Source-Projekten und selbst erstellten Designs. Auch kommerzielle Organisationen finden dies attraktiv und verwenden es in FPGAs, SoCs oder sogar im Kern eines Mikrocontrollers oder Standardproduktangebots.

Dank der Freiheit, die es bietet, kann die Wissenschaft neue Ansätze zur Bewältigung von Rechenherausforderungen untersuchen und alles von neuen Anweisungen und anderen Beschleunigern über heterogene Multi-Core- und Many-Core-Designs bis hin zu verschiedenen Mikroarchitekturoptionen implementieren. Viele dieser Optionen sind auch für Start-ups und Unternehmen attraktiv, die komplexe Herausforderungen meistern möchten, wie z

Da das Ökosystem mit integrierter RISC-V-Flexibilität eingerichtet wurde, sollte jede Standardkonfiguration oder benutzerdefinierte Erweiterung in der Lage sein, die Tools und Software innerhalb des ISA-konformen Frameworks zu nutzen.

Die Flexibilität des offenen RISC-V ISA verstehen

Dank der Zugänglichkeit des RISC-V ISA und der zugehörigen Tools ist es einfach, ein Untersuchungsprojekt zu starten, um seine Eignung für den Einsatz in einer bestimmten Anwendung zu bewerten. Simulationswerkzeuge ermöglichen das Erproben einer standardmäßigen Basis-ISA, um die Out-of-the-Box-Leistung zu bestimmen. Ein guter Ausgangspunkt wäre beispielsweise eine 32-Bit-RISC-V-Konfiguration mit ganzzahligen „I“- und multiplizierten „M“-Erweiterungen (die als RV32IM bezeichnet werden können), die einen 32-Bit-Integer-Basisbefehlssatz unterstützen; Es stehen weitere Optionen zur Verfügung, dies ist jedoch für dieses Beispiel ausreichend. Dieser wird dann zusammen mit einem simulierten Speicher inklusive Zugriffsverzögerungen und Wartezuständen instanziiert.

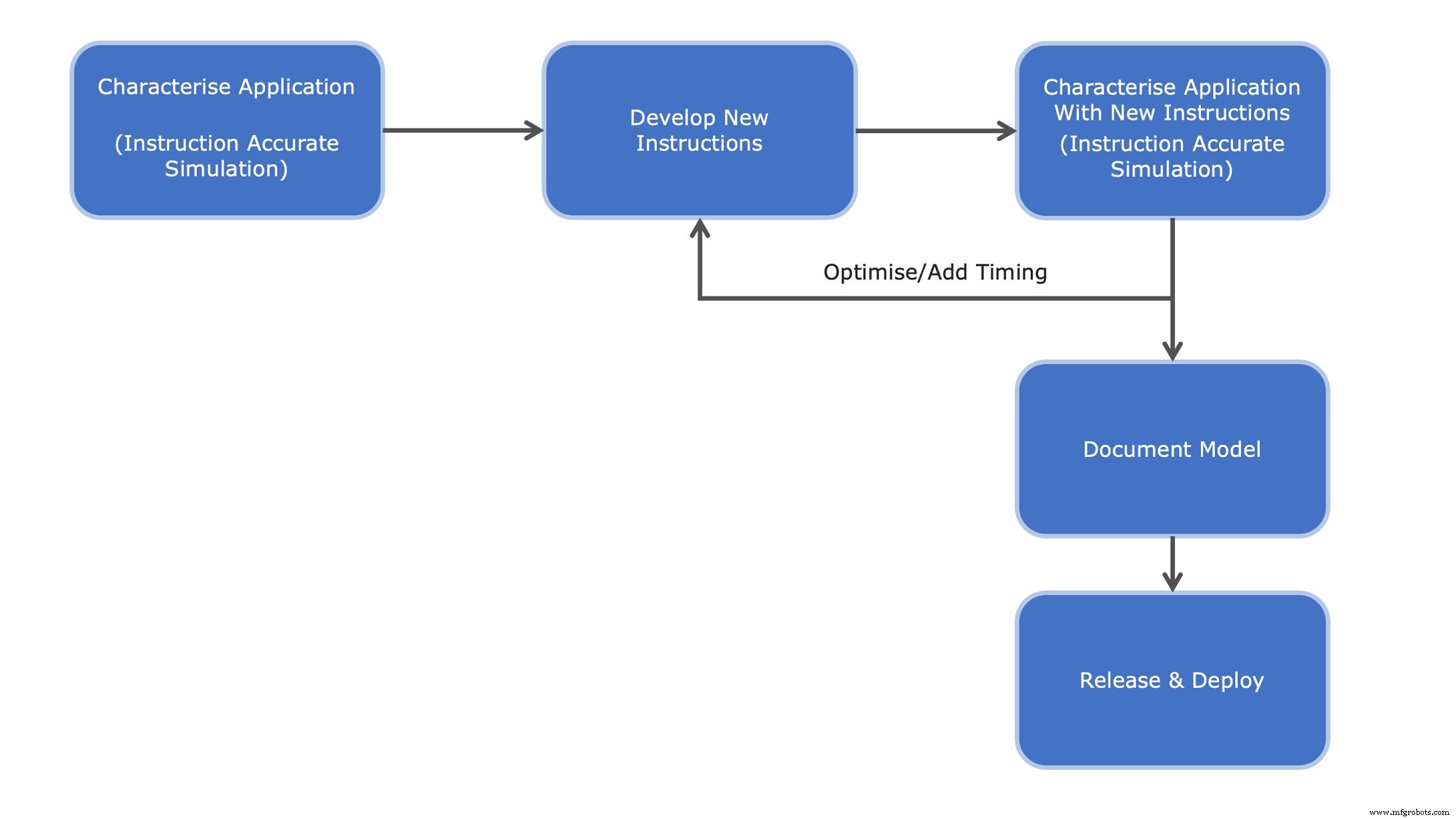

Eine in C/C++ geschriebene Anwendung kann dann mit Standard-Toolchains querkompiliert werden. Dies kann auf Bare Metal oder als Teil eines (Echtzeit-)Betriebssystems (RTOS/OS) ausgeführt werden. Der resultierende Binärcode wird dann mit Werkzeugen wie einem Befehlssatzsimulator (ISS) ausgeführt, der es ermöglicht, das gewählte Basisprozessormodell zu integrieren und zu simulieren (Abbildung 1). Diese Umgebung bietet auch Standard-Eingabe-/Ausgabefunktionalität und Zugriff auf das Host-Dateisystem. Standardmäßige integrierte Entwicklungsumgebungs-(IDE)-Tools wie Eclipse können dann verwendet werden, um die Codeausführung zu steuern und über den GNU-Debugger GDB zu verbinden.

Von hier aus werden durch einen Profiling- und Analyseprozess Instruktionskandidaten identifiziert, entworfen und modelliert. Durch die Verwendung des ursprünglichen Anwendungscodes als grundlegendes Funktionsmodell kann die resultierende Verbesserung schnell getestet, verifiziert und die Leistung verglichen werden. Diese schnelle Iteration von Profiling und Analyse ermöglicht eine schnelle Auswahl und Optimierung von Anweisungen, die es wert sind, implementiert zu werden. Die Dokumentation kann aus dem Modell generiert werden und bildet die Grundlage für eine Funktionsspezifikation für das Register-Transfer-Logic (RTL)-Design und ein optimiertes Modell.

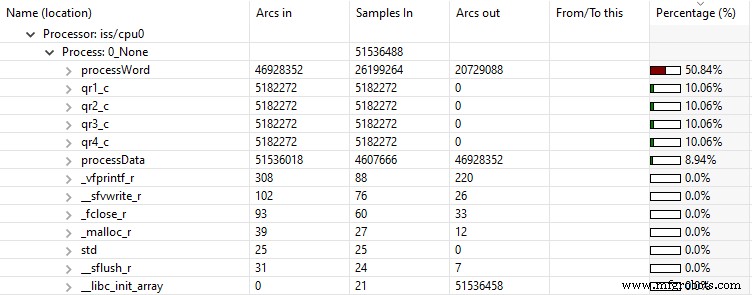

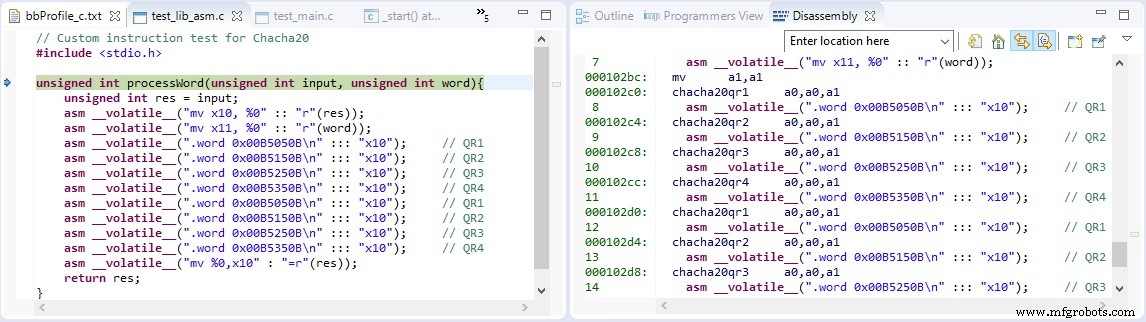

Beispielsweise kann ein Verschlüsselungsalgorithmus wie ChaCha20 für eine bestimmte Anwendung kritisch sein. Verfügbarer Quellcode kann für eine „Vanille“-RV32IM-Basis kompiliert, ausgeführt und dann mit geschätztem Befehlszyklus-Timing analysiert werden, indem grundlegendes Blockprofiling verwendet wird, um festzustellen, wie viel Zeit in welchen Codeabschnitten verbracht wurde. Der Kern des ChaCha20-Algorithmus verwendet intensiv XOR- und Rotationsbefehle, die als Viertelrunden bekannt sind (Abbildung 2). Die Ergebnisse der Blockprofilerstellung zeigen sofort, dass der Großteil der Ausführungszeit für diese Funktionen aufgewendet wird.

Eine grafische Visualisierung dieser Hotspots kann auch mithilfe eines Verifikations-, Analyse- und Profilierungstools (VAP) erstellt werden. Anstatt eine Textausgabe bereitzustellen, wird die Ausführungszeit als Baum aus zusammenklappbaren Statistiken bereitgestellt, wodurch Hotspots mit einem hohen Anteil ausgeführter Anweisungen besser visualisiert werden können. Dies ist in Abbildung 3 zu sehen, wo die Funktion processWord() implementiert den ChaCha20-Algorithmus und ruft der Reihe nach die vier qrx_c Funktionen, um die erforderlichen Viertelrundenfunktionen zu implementieren.

Durch Überprüfen des vom Compiler erzeugten Assemblercodes und/oder durch Ausführen einer grundlegenden Blockprofilerstellung ist es dann möglich zu bestimmen, welche Befehle und Befehlskombinationen verwendet wurden, um den Algorithmus zu implementieren. Von hier aus besteht der nächste Schritt darin, zu bestimmen, welche benutzerdefinierten Anweisungen innerhalb der Grenzen der Spezifikationen der ISA möglicherweise die Ausführungsgeschwindigkeit erhöhen könnten.

Bestimmung der potenziellen Verbesserung, die RISC-V liefern könnte

Der ChaCha20-Algorithmus verwendet intensiv ein XOR in Verbindung mit einer Linksdrehung von 7, 8, 12 und 16 Bit. Die Verwendung der verfügbaren Anweisungen der RV32IM-Basisspezifikation zeigt, dass dies eine XOR-Anweisung gefolgt von einer Shift-Links-Anweisung erfordert. Dies bedeutet, dass es möglich ist, diese beiden Schritte in vier dedizierte Anweisungen zu optimieren, die ein XOR zusammen mit 7, 8, 12 oder 16 Bit Linksdrehung implementieren.

Da es sich um eine Load-Store-Architektur handelt, müssen alle benutzerdefinierten Befehle davon ausgehen, dass sich die zu bearbeitenden Daten bereits in einem der 32-Bit-Register dieses RISC-V befinden. Dadurch wird sofort festgestellt, dass eine Anweisung vom Typ R (Register) benötigt wird, die sich in custom-1 befinden kann Dekodierungsraum (Abbildung 4).

Die ISA bietet eine klare Struktur für solche Anweisungen. Indem wir diese Regeln befolgen, können wir schnell feststellen, wie unsere neuen Anweisungen zu codieren sind. Die unteren 7 Bits sind als Opcode definiert dem ein Wert zugewiesen wird, der ihn als benutzerdefinierte Anweisung im custom-1 . markiert Raum dekodieren. Dies steht im Gegensatz zum OP oder OP-IMM Opcodes, die für die bestehenden XOR- bzw. Shift-Links-Befehle verwendet werden.

Die ISA bietet eine klare Struktur für solche Anweisungen. Indem wir diese Regeln befolgen, können wir schnell feststellen, wie unsere neuen Anweisungen zu codieren sind. Die unteren 7 Bits sind als Opcode definiert dem ein Wert zugewiesen wird, der ihn als benutzerdefinierte Anweisung im custom-1 . markiert Raum dekodieren. Dies steht im Gegensatz zum OP oder OP-IMM Opcodes, die für die bestehenden XOR- bzw. Shift-Links-Befehle verwendet werden.

In der ISA-Definition sind drei vordefinierte Bitblöcke reserviert, um die beiden Quellregister und das Zielregister für das Ergebnis vorzugeben. Dies hinterlässt einen Bitblock, der als funct3 bekannt ist . Diese drei Bits bieten uns Platz zum Kodieren von acht möglichen Befehlen, von denen vier in diesem Beispiel verwendet werden.

Ohne die detaillierte Hardwareimplementierung der RTL für diese Anweisungen zu benötigen, ist es möglich, sie in der ISS-Umgebung zu simulieren, um zu sehen, ob sie für die gestellte Herausforderung überhaupt von Nutzen sind. Die vier neuen Anweisungen werden unter Verwendung der VMI-Anwendungsprogrammierschnittstelle (API) für offene virtuelle Plattformen (OVP) modelliert. Dies ermöglicht dem Entwickler, das Design der Anweisungen schnell zu wiederholen, das das optimale gewünschte Ergebnis basierend auf den neuen Anweisungen für die Zielanwendung liefert. Erst wenn dies erreicht ist, müssen Ressourcen für eine RTL-Implementierung bereitgestellt werden.

Für eine erste funktionale Bewertung der Anleitung gibt es zwei mögliche Vorgehensweisen. Die erste besteht darin, die ursprüngliche C/C++-Version des Algorithmus aufzurufen und die neuen Anweisungen an diese Funktion zu binden (Abbildung 5a). Die zweite besteht darin, sie als VMI-Morph-Befehle zu implementieren, die das gleiche Verhalten erzeugen (Abbildung 5b). Dies hat den Vorteil, dass es effizienter ist und wird empfohlen.

Die bloße Existenz neuer Anweisungen bedeutet natürlich nicht, dass ein Compiler diese sofort verwenden kann. Daher muss die ursprüngliche C/C++-Anwendung mit Inline-Assembler neu geschrieben und querkompiliert werden, um die neuen Anweisungen zu verwenden. Da die Profilerstellung und Analyse von Kandidatenanweisungen eine iterative Aufgabe sein kann, bietet der intrinsische Ansatz die effizienteste Möglichkeit, die ursprüngliche C-Anwendung an die Verwendung der neuen benutzerdefinierten Anweisungen anzupassen.

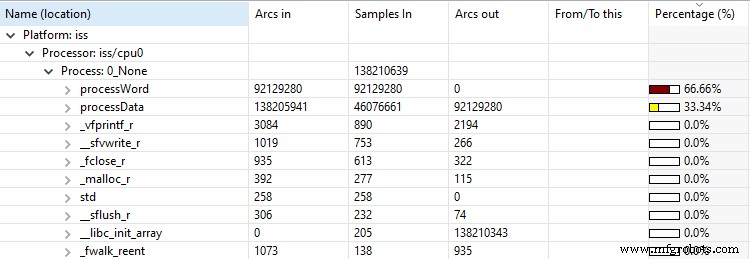

Die in den Simulator geladene RISC-V-Basisimplementierung muss auch auf die neuen Anweisungen aufmerksam gemacht werden, um davon zu profitieren. Dies wird erreicht, indem sie in das Modell aufgenommen werden, bevor die Simulation erneut ausgeführt wird. In diesem speziellen Beispiel bedeutet die Wiederholung der Profilerstellung weniger Gesamtzeit, die für die Durchführung des Algorithmus aufgewendet wird (Abbildung 6). Das Imperas VAP-Profiling-Tool zeigt, dass das processWord() Funktion, die die dedizierten Inline-Befehle verwendet, macht jetzt 66% der gesamten Algorithmusausführung aus, aber die Gesamtausführungszeit für den Algorithmus ist stark reduziert (Abbildung 6b).

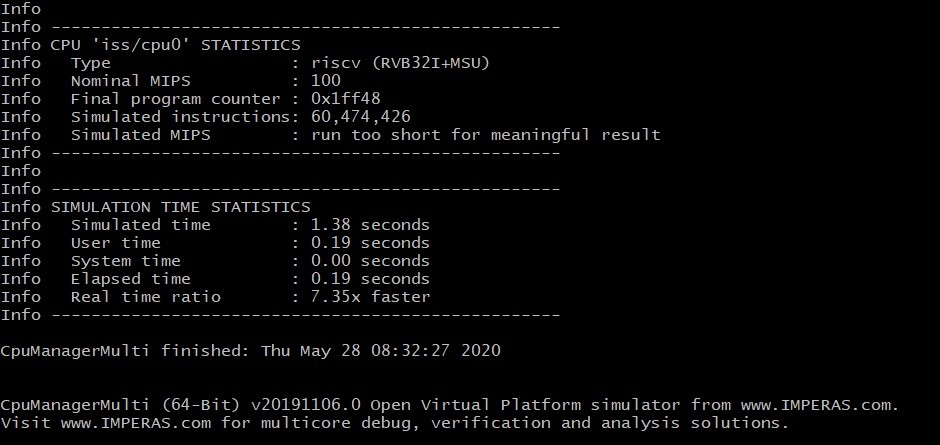

Ergebnisse mit der ursprünglichen C-Implementierung

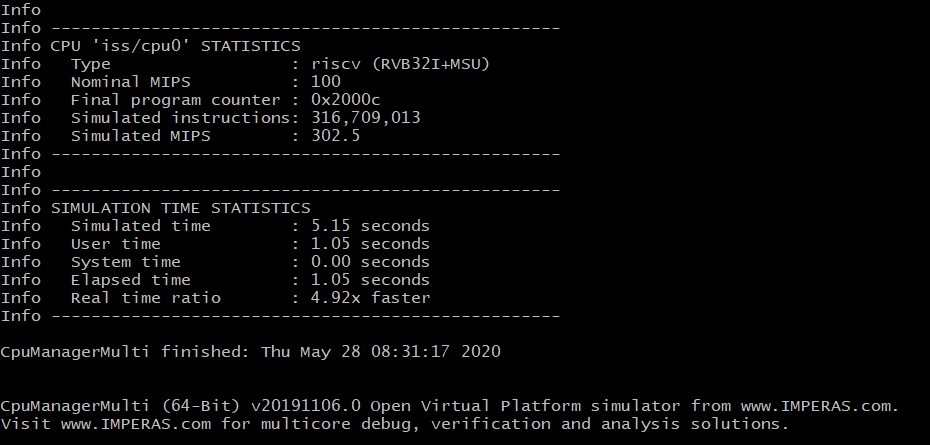

Info Simulierte Anweisungen:316.709.013

Info Simulierte Zeit :5,15 Sekunden

Ergebnisse mit benutzerdefinierten Anweisungen

Info Simulierte Anweisungen:60.474.426

Info Simulierte Zeit :1,38 Sekunden

Sobald die korrekte Funktionalität bestimmt wurde, wird das Modell weiter verfeinert, indem die Ausführungszeit für jeden Befehl in Prozessorzyklen deklariert wird. Weitere Simulationsrunden können dann verwendet werden, um eine Leistungsverbesserung zu bestimmen, sogar unter Berücksichtigung von Wartezuständen im Zusammenhang mit Speicherzugriffen, die bei einer eventuellen Hardwareimplementierung auftreten können.

Dank der engen Integration mit gängigen Open-Source-IDEs und GDB-Tools kann ein vollständiges Debugging der Lösung in Verbindung mit dem optimierten RISC-V-Design durchgeführt werden, bevor das Design einer Hardwareimplementierung übergeben wird (Abbildung 7).

Von der Simulation zur Implementierung wechseln

Nachdem die potenzielle Leistungsverbesserung ermittelt wurde, erfordert der nächste Schritt die Implementierung der vier neuen Anweisungen in RTL. Durch die geleisteten Vorarbeiten wird daraus die funktionale Spezifikation, die die Anforderungen definiert und auch im Rahmen des RTL-Verifikationstestplans als goldenes Referenzmodell verwendet werden kann. Während die Verwendung intrinsischer Funktionen in der C-Anwendung die Profilerstellung und Analyse benutzerdefinierter Anweisungen unterstützte, kann dieser Ansatz auch für die zukünftige Entwicklung von Produktionscode verwendet werden oder für potenzielle Verbesserungen der Compiler-Toolkette in Betracht gezogen werden.

Die andere verbleibende wesentliche Aufgabe, die Dokumentation, ist ebenfalls ein einfacher Prozess. Alle schnellen Prozessormodelle der offenen virtuellen Plattformen (OVP) enthalten eine Dokumentation, die erweitert werden kann, um die Funktionalität von Änderungen und Modifikationen abzudecken. Nach der vorgegebenen Vorlage können die neuen Anweisungen deklariert und beschrieben werden, sodass die Entwicklergemeinschaft ihre Fähigkeiten entdecken und nutzen kann. Anschließend wird die Dokumentation in eine TeX-Datei umgewandelt, aus der ein PDF generiert werden kann (Abbildung 8).

Zusammenfassung

Mit den Freiheiten der offenen ISA von RISC-V können Anwender zusätzlich zu den in der Spezifikation definierten Standardoptionen und Features weitere kundenspezifische Erweiterungen und Anleitungen entwickeln. Im einfachsten Fall ermöglicht es neue und kreative Geschäftsmodelle, einschließlich kommerzieller und Open-Source-Implementierungen, und bietet mehr Freiheit, um Mehrwertfunktionen jenseits der herkömmlichen herkömmlichen Ansätze zu erkunden.

Der wahre Wert liegt jedoch darin, einen vollwertigen, dokumentierten und unterstützten Basiskern zu nehmen und ihn an die spezifischen Anwendungsanforderungen anzupassen. Durch sorgfältige Anwendungsanalyse, Profilerstellung von Code und Simulation können signifikante Leistungsverbesserungen erreicht werden, die mit festen ISAs nicht realisierbar wären. All dies kann mit realen Anwendungsworkloads entwickelt und profiliert werden, bevor mit der detaillierten Hardwareimplementierung begonnen wird.

Eingebettet

- Profilerstellung verteilter Anwendungen mit Perf

- Eine kurze Anleitung zum 3D-Druck mit Binder Jetting

- Mikrochip:Skalieren von Weltraumanwendungen mit COTS-zu-strahlungstoleranten Core-MCUs

- Renesas:RX72M-MCUs mit EtherCAT-Unterstützung für industrielle Anwendungen

- Axiomtek:eingebettetes System mit integriertem Layer-2-Managed-PoE-Switch

- Kosten mit bestehenden Lieferanten neu verhandeln:Ein Leitfaden

- CNC-Holzfräser - mit atemberaubenden Anwendungen

- Erste Schritte mit KI im Versicherungswesen:Ein Einführungsleitfaden

- 5 reale Anwendungen von KI in der Medizin (mit Beispielen)

- Ein Leitfaden für kundenspezifische Bremsbacken und Bremsbeläge für Hochgeschwindigkeitsanwendungen