Vereinfachung von AC- und DC-Signalketten zur Datenerfassung

Abtastphänomene in Analog-Digital-Wandlern (ADCs) führen zu den Problemen von Aliasing und kapazitivem Rückschlag. Um diese Probleme zu lösen, verwenden Designer Filter und Treiberverstärker, die ihre eigenen Herausforderungen mit sich bringen. Dies macht das Erreichen einer präzisen Gleichstrom- und Wechselstromleistung in Anwendungsbereichen mit mittlerer Bandbreite zu einer Herausforderung, und Entwickler müssen dafür die Systemziele abwägen.

Dieser Artikel beschreibt zeitkontinuierliche Sigma-Delta (∑-Δ)-ADCs, die die Abtastprobleme durch Vereinfachung der Signalketten von Natur aus und dramatisch lösen. Sie machen Antialiasing-Filter und -Puffer überflüssig und lösen Signalketten-Offset-Fehler und Drift-Probleme, die mit den zusätzlichen Komponenten verbunden sind. Diese Vorteile verkleinern die Lösungsgröße, vereinfachen das Lösungsdesign und verbessern die Phasenanpassung und die Gesamtlatenz des Systems. Dieser Artikel zieht auch einen Vergleich mit zeitdiskreten Wandlern und hebt die Systemvorteile sowie die Einschränkungen bei der Verwendung von zeitkontinuierlichen Sigma-Delta-ADCs hervor.

Grundlagen der Stichprobenziehung

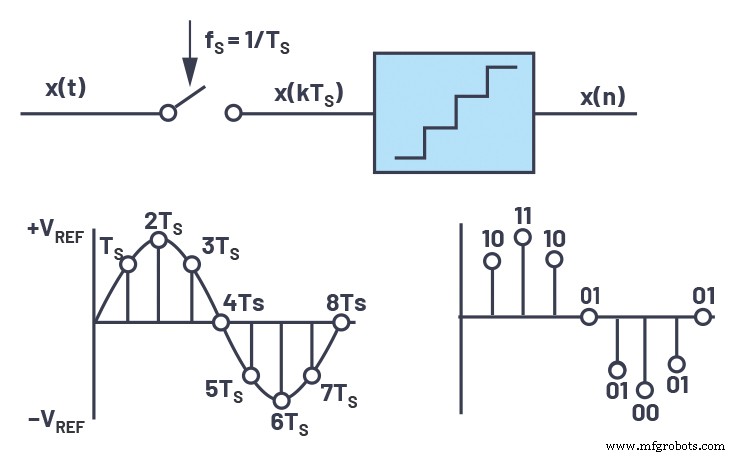

Die Digitalisierung von Daten umfasst die beiden grundlegenden Prozesse Abtastung und Quantisierung, wie in Abbildung 1 gezeigt. Die Abtastung ist der erste Schritt, bei dem ein zeitkontinuierlich variierendes analoges Signal x(t) mithilfe von Abtastung in ein zeitdiskretes Signal x(n) umgewandelt wird Frequenz fS. Das Ergebnis wird gleichmäßig durch eine Periode von 1/TS (fS =1/TS) getrennt.

Klicken für größeres Bild

Abbildung 1. Datenstichprobe. (Quelle:Analog Devices)

Der zweite Schritt ist die Quantisierung, die den Wert dieser zeitdiskreten Abtastwerte an einen der endlichen möglichen Werte annähert und in digitalem Code dargestellt wird, wie in Abbildung 1 gezeigt. Diese Quantisierung in eine endliche Menge von Werten führt zu einem Fehler bei der Digitalisierung, genannt Quantisierungsrauschen.

Der Sampling-Prozess führt auch zu Aliasing, bei dem wir einen Foldback von Eingangssignalen und seinen Oberwellen um die Sample-and-Hold-Taktfrequenz sehen. Das Nyquist-Kriterium erfordert, dass die Abtastfrequenz mindestens das Doppelte der höchsten im Signal enthaltenen Frequenz beträgt. Wenn die Abtastfrequenz weniger als das Doppelte der maximalen analogen Signalfrequenz beträgt, tritt ein Phänomen auf, das als Aliasing bekannt ist.

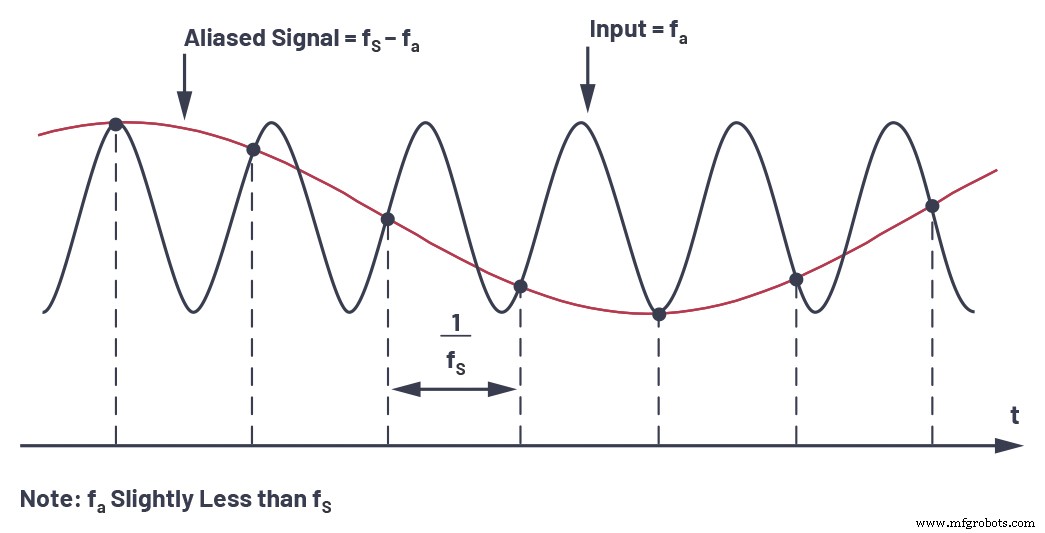

Um die Auswirkungen von Aliasing sowohl im Zeit- als auch im Frequenzbereich zu verstehen, betrachten wir zunächst den Fall einer Zeitbereichsdarstellung einer einzelnen Tonsinuswelle, die wie in Abbildung 2 gezeigt abgetastet wird. In diesem Beispiel ist die Abtastfrequenz fS nicht mindestens 2fa, aber nur geringfügig höher als die analoge Eingangsfrequenz fa, wodurch das Nyquist-Kriterium nicht erfüllt wird. Beachten Sie, dass das Muster der tatsächlichen Samples eine verfälschte Sinuswelle mit einer niedrigeren Frequenz von fS – fa erzeugt.

Klicken für größeres Bild

Abbildung 2. Aliasing:Darstellung im Zeitbereich. (Quelle:Analog Devices)

Klicken für größeres Bild

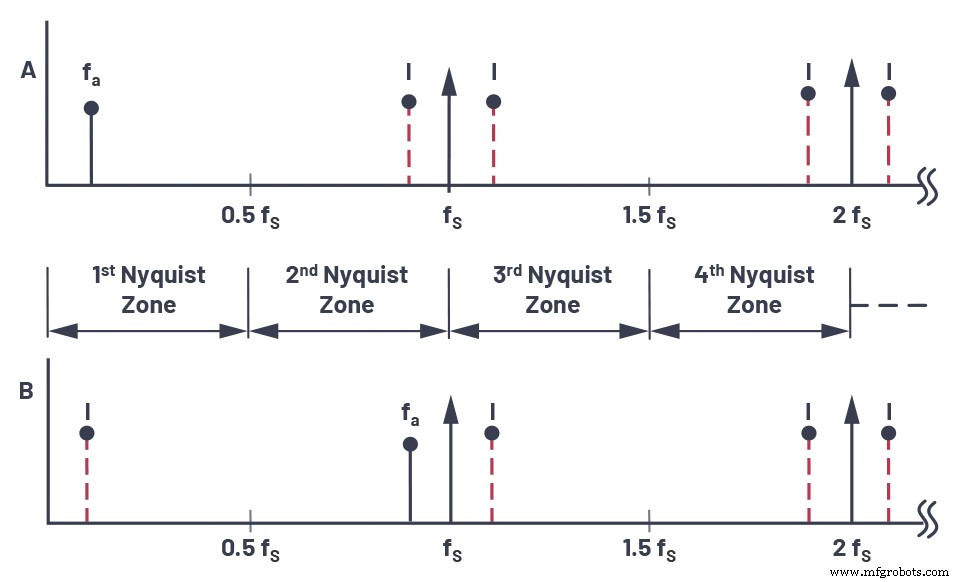

Abbildung 3. Aliasing:Darstellung im Frequenzbereich. (Quelle:Analog Devices)

Die entsprechende Frequenzbereichsdarstellung dieses Szenarios ist in Abbildung 3 dargestellt.

Die Nyquist-Bandbreite ist definiert als das Frequenzspektrum von DC bis fS/2. Das Frequenzspektrum ist in unendlich viele Nyquist-Zonen unterteilt, die jeweils eine Breite von 0,5 fS aufweisen. In der Praxis wird der ideale Sampler durch einen ADC gefolgt von einem FFT-Prozessor ersetzt. Der FFT-Prozessor liefert nur eine Ausgabe von DC bis fS/2; das sind die Signale oder Aliase, die in der ersten Nyquist-Zone erscheinen.

Betrachten Sie den Fall einer Sinuswelle mit einer einzigen Frequenz der Frequenz fa, die bei einer Frequenz fS von einem idealen Impulsabtaster abgetastet wird (siehe Abbildung 1). Nehmen Sie auch an, dass fS> 2fa ist. Der Frequenzbereichsausgang des Abtasters zeigt Aliase oder Bilder des Originalsignals um jedes Vielfache von fS; das heißt, bei Frequenzen gleich | ± KfS ± fa|, K =1, 2, 3, 4 usw.

Betrachten Sie nun den Fall eines Signals, das sich außerhalb der ersten Nyquist-Zone in Abbildung 3 befindet. Die Signalfrequenz ist nur geringfügig niedriger als die Abtastfrequenz, entsprechend der Bedingung, die in der Zeitbereichsdarstellung in Abbildung 2 gezeigt wird. Beachten Sie, dass, obwohl die Signal befindet sich außerhalb der ersten Nyquist-Zone, sein Bild (oder Alias), fS – fa, fällt hinein. Zurück zu Abbildung 3 ist klar, dass, wenn ein unerwünschtes Signal bei einer der Spiegelfrequenzen von fa auftritt, es auch bei fa auftritt, wodurch eine Störfrequenzkomponente in der ersten Nyquist-Zone erzeugt wird.

Herausforderungen für Präzisionsleistung bekämpfen

Für Hochleistungsanwendungen müssen Systemdesigner Quantisierungsrauschen, Aliasing und Eingangsabtastprobleme mit geschalteten Kondensatoren bekämpfen, die sich aus dem Abtastprozess ergeben. Beide Arten von Präzisions-ADCs – d. h. sukzessive Approximationsregister (SARs) und Sigma-Delta-ADCs, die in der Industrie erhältlich sind – werden mit Sampling-Techniken auf Basis von geschalteten Kondensatoren entwickelt.

Quantisierungsrauschen

In einem idealen Nyquist-ADC bestimmt die LSB-Größe des ADC das Quantisierungsrauschen, das dem Eingang bei der Analog-Digital-Wandlung hinzugefügt wird. Dieses Quantisierungsrauschen wird über die Bandbreite von fS/2 verteilt. Um das Quantisierungsrauschen zu bekämpfen, ist die erste Technik das Oversampling, bei dem das Eingangssignal mit einer viel höheren Rate als die Nyquist-Frequenz abgetastet wird, um das Signal-Rausch-Verhältnis (SNR) und die Auflösung (ENOB) zu erhöhen. Beim Oversampling wird die Abtastfrequenz N-mal die Nyquist-Frequenz (2 × fIN) gewählt, und folglich muss sich das gleiche Quantisierungsrauschen nun über die N-fache Nyquist-Frequenz verteilen. Dadurch werden auch die Anforderungen an den Antialiasing-Filter gelockert. Das Oversampling-Verhältnis (OSR) ist als fS/2fIN definiert, wobei fIN das interessierende Signal BW ist. Als allgemeine Richtlinie gilt, dass ein Oversampling des ADC um den Faktor vier ein zusätzliches Bit an Auflösung oder eine 6-dB-Vergrößerung des Dynamikbereichs bietet. Eine Erhöhung des Oversampling-Verhältnisses führt zu einem insgesamt reduzierten Rauschen und die Verbesserung des Dynamikbereichs (DR) aufgrund von Oversampling beträgt ΔDR =10log10 OSR in dB.

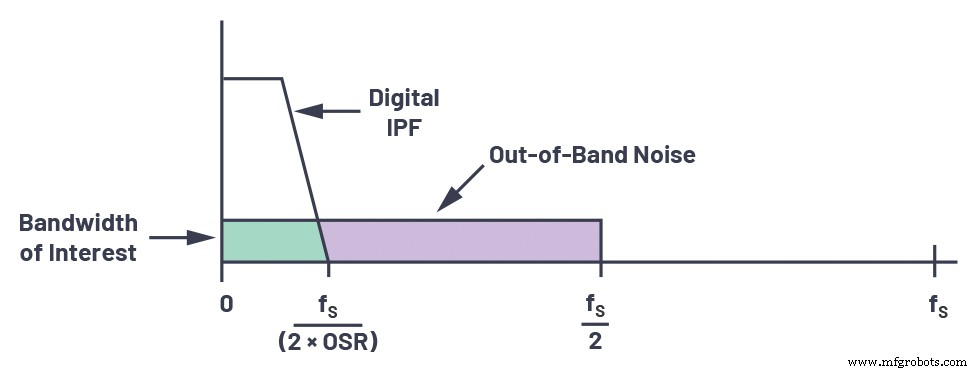

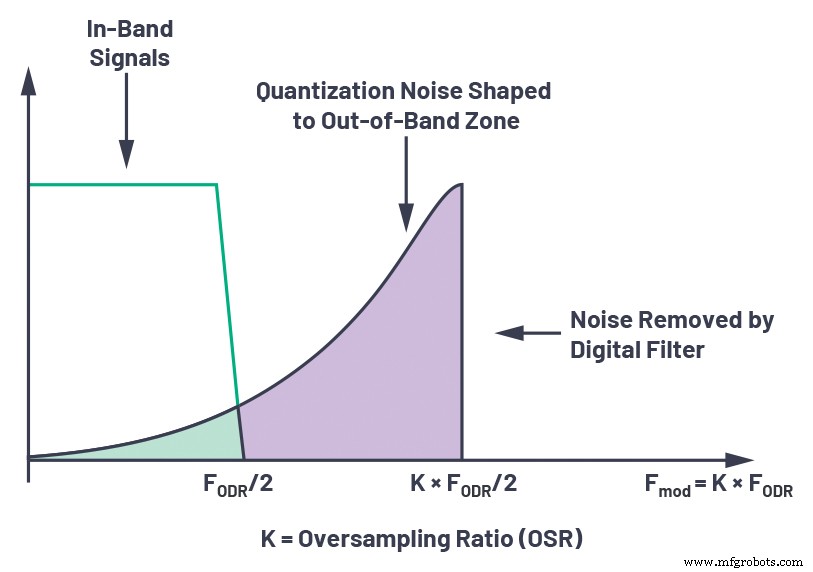

Oversampling wird von Natur aus verwendet und zusammen mit einem integrierten digitalen Filter und einer Dezimierungsfunktionalität implementiert. Der grundlegende Oversampling-Modulator im Sigma-Delta-ADC formt das Quantisierungsrauschen so, dass das meiste davon außerhalb der interessierenden Bandbreite auftritt, was zu einem erhöhten Gesamtdynamikbereich bei niedrigen Frequenzen führt, wie in Abbildung 4 gezeigt. Der digitale Tiefpassfilter (LPF ) entfernt dann das Quantisierungsrauschen außerhalb der interessierenden Bandbreite, und der Dezimator reduziert die Ausgangsdatenrate zurück auf die Nyquist-Rate.

Klicken für größeres Bild

Abbildung 4. Ein Beispiel für Oversampling. (Quelle:Analog Devices)

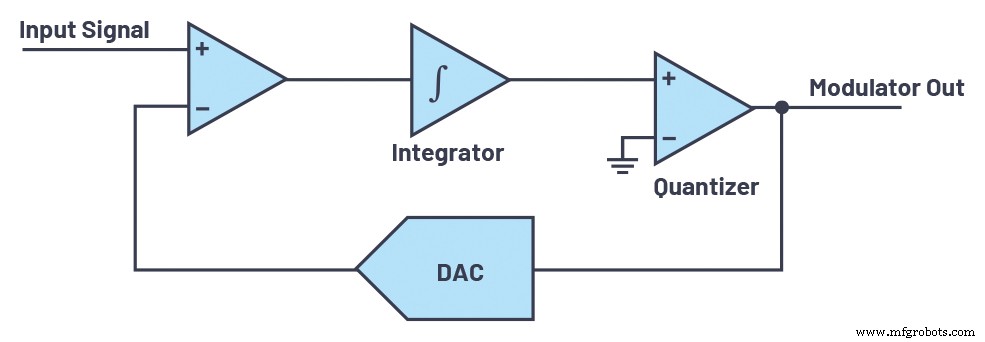

Rauschformung ist die andere Technik, um das Quantisierungsrauschen zu reduzieren. In Sigma-Delta-ADCs wird ein Quantisierer mit niedriger Auflösung (ein Bit bis fünf Bits) innerhalb einer Schleife nach dem Schleifenfilter verwendet. Ein DAC wird als Feedback verwendet, um das quantisierte Signal vom Eingang zu subtrahieren, wie in Abbildung 5 gezeigt.

Klicken für größeres Bild

Abbildung 5. Rauschformung. (Quelle:Analog Devices)

Der Integrator summiert weiterhin den Quantisierungsfehler, was dazu führt, dass das Quantisierungsrauschen zu höheren Frequenzen geformt wird, die dann unter Verwendung eines digitalen Filters gefiltert werden können. 6 veranschaulicht die spektrale Leistungsdichte (PSD) des Ausgangs x[n] eines typischen Sigma-Delta-ADC. Die Rauschformungssteigung hängt von der Ordnung des Schleifenfilters H(z) ab (siehe Abbildung 11) und beträgt (20 × n) dB/Dekade, wobei n die Ordnung des Schleifenfilters ist. Der Sigma-Delta-ADC erreicht eine hohe Auflösung im Band durch eine Kombination aus Rauschformung und Oversampling. Die Inband-Bandbreite ist gleich fODR/2 (ODR steht für Output Data Rate). Eine höhere Auflösung kann durch Erhöhen der Ordnung des Schleifenfilters oder durch Erhöhen des Oversampling-Verhältnisses erreicht werden.

Klicken für größeres Bild

Abbildung 6. Oversampling- und Rauschformungsdiagramm. (Quelle:Analog Devices)

Aliasing

Um Aliasing in Hochleistungsanwendungen zu bekämpfen, werden Antialiasing-Filter höherer Ordnung verwendet, um jedes Ausmaß an Foldback zu vermeiden. Ein Antialiasing-Filter ist ein Tiefpassfilter, der das Eingangssignal bandbegrenzt und sicherstellt, dass keine Frequenzkomponente im Signal jenseits der interessierenden Bandbreite vorhanden ist, die zurückklappen kann. Die Filterleistung hängt davon ab, wie nahe das Außerbandsignal an fS/2 liegt und wie stark die Dämpfung erforderlich ist.

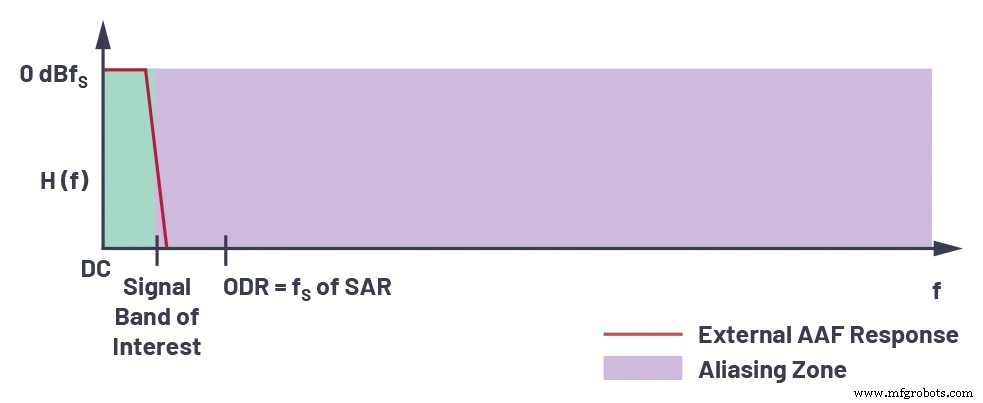

Bei SAR-ADCs ist die Lücke zwischen dem Eingangssignal BW und der Abtastfrequenz nicht groß, daher benötigen wir einen Filter höherer Ordnung, der ein komplexes Filterdesign höherer Ordnung mit mehr Leistung und mehr Verzerrung erfordert. Wenn beispielsweise ein SAR mit einer Abtastgeschwindigkeit von 200 kSPS einen Eingangs-BW von 100 kHz hat, muss der Antialiasing-Filter ein Eingangssignal von> 100 kHz zurückweisen, um sicherzustellen, dass kein Aliasing auftritt. Dies erfordert einen Filter sehr hoher Ordnung. Abbildung 7 zeigt die Nachfrage mit steiler Kurve.

Klicken für größeres Bild

Abbildung 7. Alias-Anforderung. (Quelle:Analog Devices)

Wenn eine Abtastgeschwindigkeit von 400 kSPS gewählt wird, um die Ordnung des Filters zu lockern, wird die Unterdrückung für eine Eingangsfrequenz von>300 kHz benötigt. Eine Erhöhung der Abtastgeschwindigkeit erhöht die Leistung, und bei doppelter Geschwindigkeit würde die Leistung ebenfalls verdoppelt. Ein weiteres Oversampling auf Kosten der Leistung wird die Antialiasing-Filteranforderungen weiter lockern, da die Abtastfrequenz viel höher ist als das Eingangs-BW.

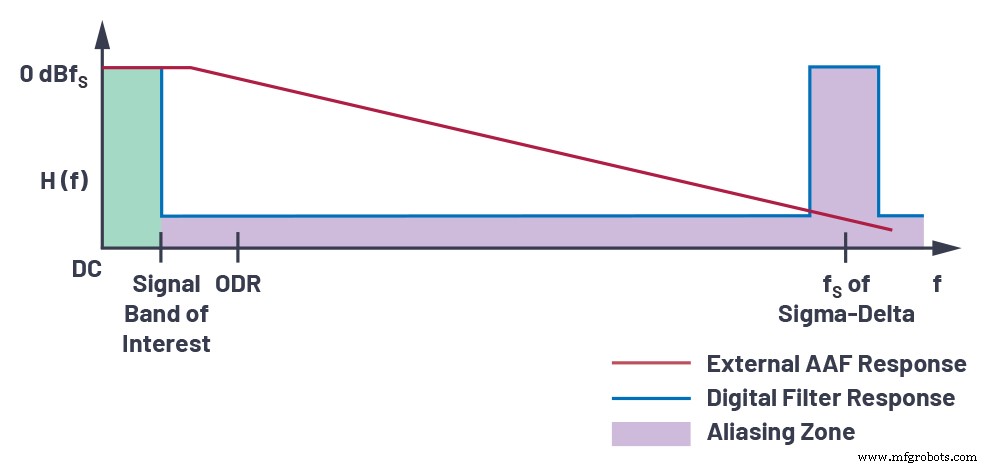

In Sigma-Delta-ADCs wird der Eingang bei einem viel höheren OSR überabgetastet, sodass die Antialiasing-Filteranforderung gelockert wird, da die Abtastfrequenz viel höher ist als die Eingangs-BW, wie in Abbildung 8 gezeigt.

Klicken für größeres Bild

Abbildung 8. Antialiasing-Filteranforderung in Sigma-Delta. (Quelle:Analog Devices)

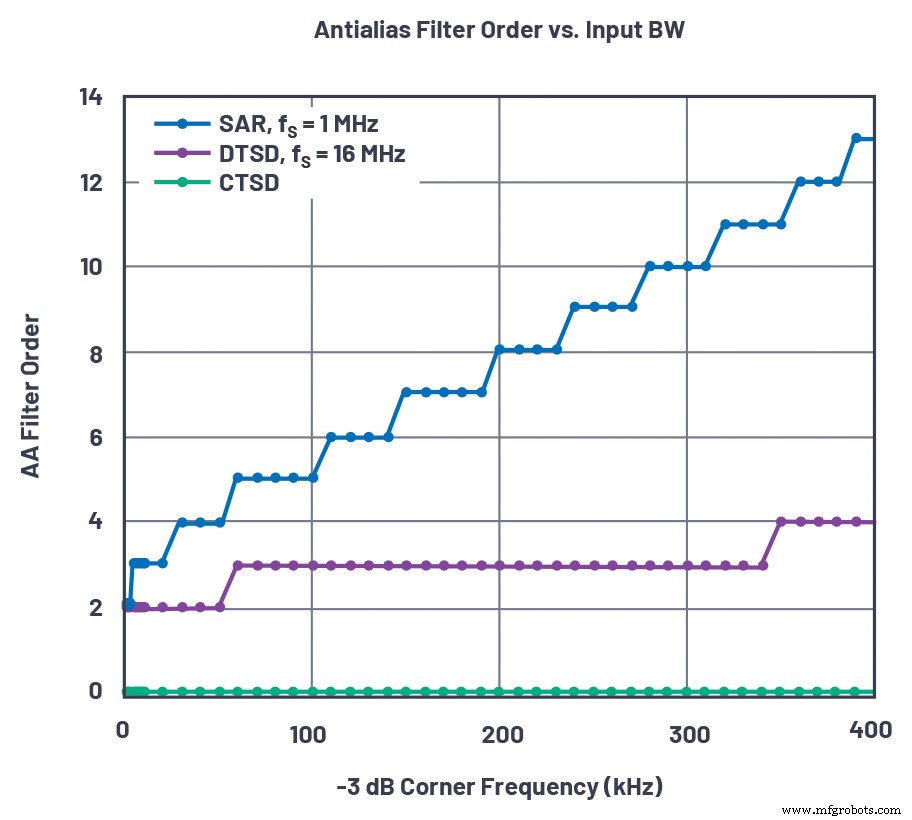

Abbildung 9 gibt eine Vorstellung von der AAF-Komplexität für SAR- und zeitdiskrete Sigma-Delta (DTSD)-Architekturen. Wenn wir eine Eingangsbandbreite von –3 dB von 100 kHz nehmen, um eine Dämpfung von 102 dB bei der Abtastfrequenz fS zu erreichen, wird ein Antialiasing-Filter zweiter Ordnung für einen DTSD-ADC benötigt, während für die gleiche Dämpfung bei fS ein Filter fünfter Ordnung mit benötigt wird ein SAR-ADC.

Bei einem zeitkontinuierlichen Sigma-Delta-ADC (CTSD) ist die Dämpfung inhärent, daher benötigen wir keinen Antialiasing-Filter.

Klicken für größeres Bild

Abbildung 9. AAF-Filteranforderungen für verschiedene Architekturen. (Quelle:Analog Devices)

Diese Filter können für Systemdesigner ein Problem darstellen, und sie müssen sie für die Abweichung, die sie im interessierenden Band bieten, optimieren und so viel Zurückweisung wie möglich bieten. Sie fügen dem System auch viele andere Fehler wie Offset, Verstärkung, Phasenfehler und Rauschen hinzu und reduzieren so seine Leistung.

Außerdem sind Hochleistungs-ADCs differenzieller Natur, sodass wir die doppelte Anzahl passiver Komponenten benötigen. Um bei Mehrkanalanwendungen eine bessere Phasenanpassung zu erzielen, müssen alle Komponenten in der Signalkette gut zusammenpassen. Daher sind Komponenten mit engeren Toleranzen erforderlich.

Geschalteter Kondensatoreingang

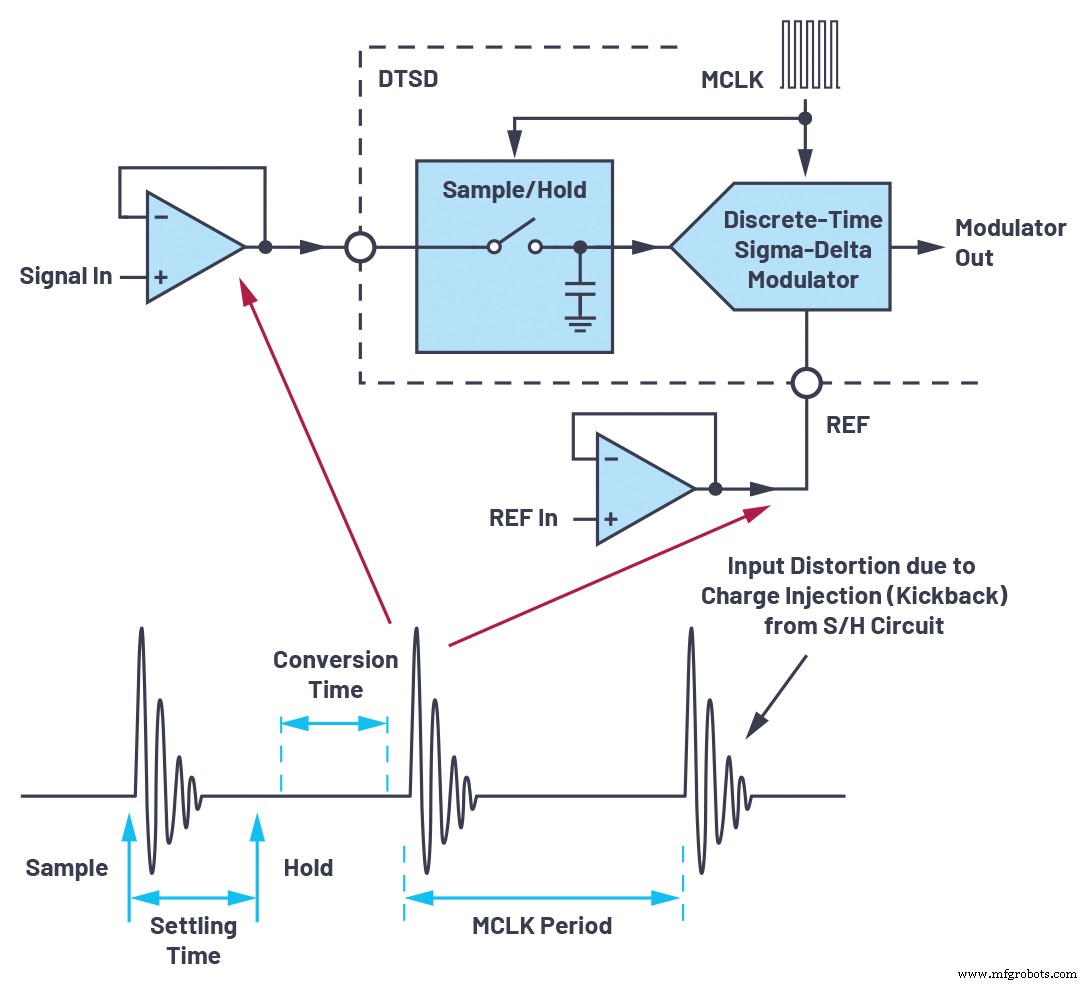

Die Eingangsabtastung mit geschalteten Kondensatoren beruht auf der Einschwingzeit des abgetasteten Eingangs auf einen Kondensator, wodurch ein Bedarf für das Laden/Entladen eines Übergangsstroms entsteht, wenn der Abtastschalter ein-/ausgeschaltet wird. Dies wird als Rückschlag am Eingang bezeichnet und erfordert einen Eingangstreiberverstärker, der diese Übergangsströme unterstützen kann. Außerdem muss der Eingang am Ende der Abtastzeit eingeschwungen werden, und die Genauigkeit des abgetasteten Eingangs bestimmt die Leistung des ADC, was bedeutet, dass der Treiberverstärker nach dem Rückschlagereignis schnell einschwingen muss. Dies führt dazu, dass ein Treiber mit hoher Bandbreite benötigt wird, der ein schnelles Einschwingen unterstützen und den Rückschlag des Schaltkondensatorbetriebs absorbieren kann. Bei geschalteten Kondensatoreingängen muss der Treiber immer dann, wenn die Abtastung eingeschaltet ist, sofort die Ladung für den Haltekondensator liefern. Dieser plötzliche Stromstoß kann nur rechtzeitig bereitgestellt werden, wenn der Treiber über ausreichende Bandbreitenkapazitäten verfügt. Aufgrund der Parasiten des Schalters kommt es zum Zeitpunkt der Probenahme zu einem Rückschlag auf den Treiber. Wenn sich der Kickback vor der nächsten Abtastung nicht einpendelt, führt dies zu einem Abtastfehler, wodurch der ADC-Eingang beschädigt wird.

Klicken für größeres Bild

Abbildung 10. Rückschlag bei der Probenahme. (Quelle:Analog Devices)

Abbildung 10 zeigt den Rückschlag des DTSD-ADC. Wenn die Abtastfrequenz beispielsweise 24 MHz beträgt, muss das Datensignal innerhalb von 41 ns einschwingen. Da die Referenz auch ein Eingang mit geschaltetem Kondensator ist, wird auch ein Puffer mit hoher Bandbreite am Referenzeingangspin benötigt. Diese Eingangssignal- und Referenzpuffer erhöhen das Rauschen und verringern die Gesamtleistung der Signalkette. Darüber hinaus erhöhen die Verzerrungskomponenten des Eingangssignaltreibers (um die S&H-Frequenz) die Antialiasing-Anforderungen weiter. Außerdem führen bei geschalteten Kondensatoreingängen Änderungen der Abtastgeschwindigkeit zu unterschiedlichen Eingangsströmen. Dies könnte zu einer Neuabstimmung des Systems führen, um Verstärkungsfehler zu reduzieren, die im Treiber oder in der vorhergehenden Stufe erzeugt werden, während der ADC betrieben wird.

Zeitkontinuierlicher Sigma-Delta-ADC

Ein CTSD-ADC ist eine alternative Sigma-Delta-ADC-Architektur, die sich Prinzipien wie Oversampling und Noise Shaping zunutze macht, aber eine alternative Methode zur Implementierung des Sampling-Vorgangs bietet, die erhebliche Systemvorteile bietet.

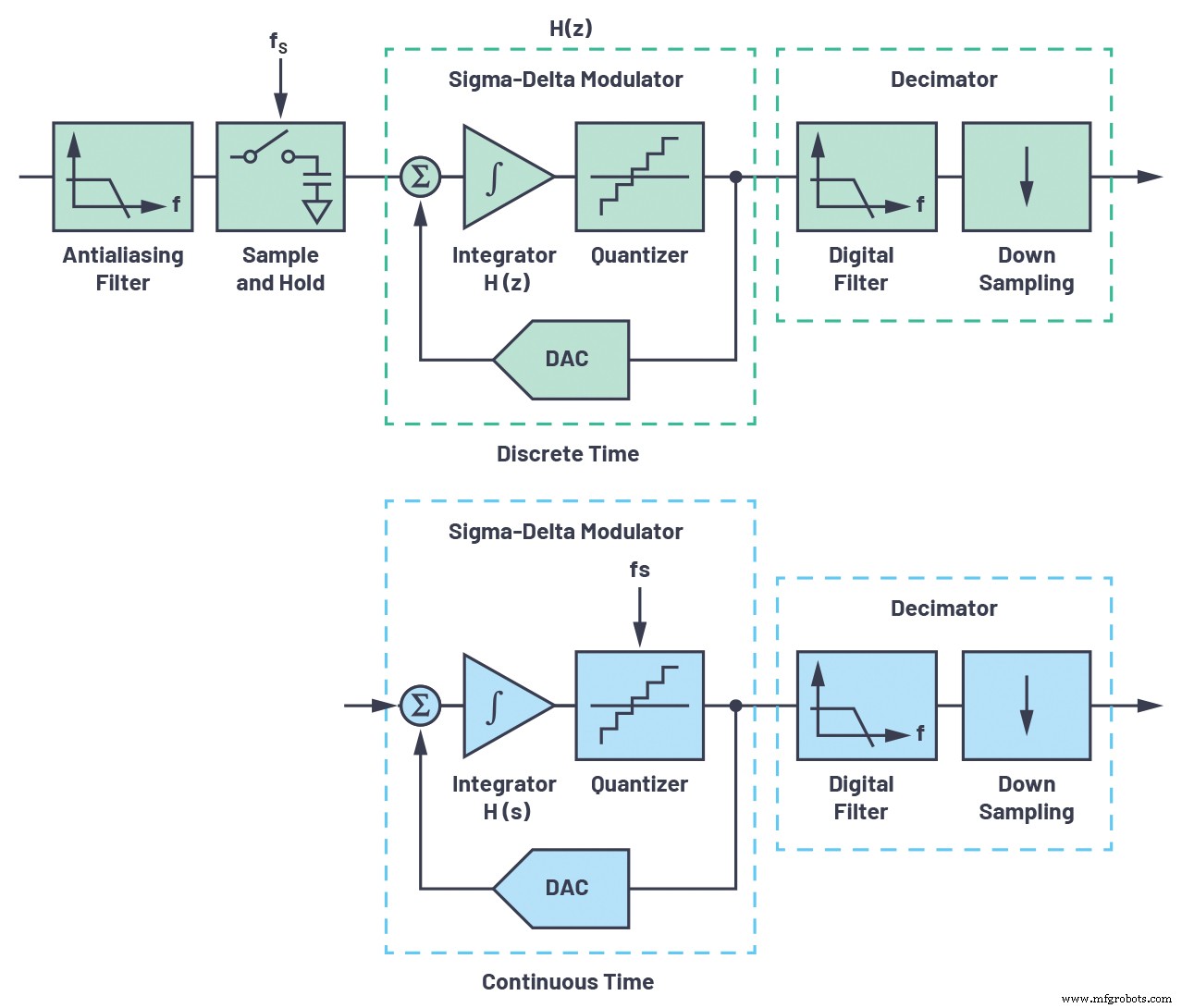

Abbildung 11 zeigt einen Vergleich einer DTSD-Architektur und einer CTSD-Architektur. Wie wir in der DTSD-Architektur sehen, wird die Eingabe vor der Schleife abgetastet. Das Schleifenfilter H(z) ist zeitdiskret und unter Verwendung von Integratoren mit geschalteten Kondensatoren implementiert. Der Rückkopplungs-DAC basiert ebenfalls auf einem geschalteten Kondensator. Da am Eingang eine Abtastung stattfindet, führt dies zu einem Aliasing-Problem von fS , ist am Eingang ein zusätzlicher Antialiasing-Filter erforderlich, bevor er abgetastet wird.

Klicken für größeres Bild

Abbildung 11. Zeitdiskrete und zeitkontinuierliche modulare Blockschaltbilder. (Quelle:Analog Devices)

CTSD hat keinen Sampler am Eingang. Stattdessen wird es am Quantisierer innerhalb der Schleife abgetastet. Der Schleifenfilter ist jetzt mit zeitkontinuierlichen Integratoren zeitkontinuierlich, ebenso wie der Rückkopplungs-DAC. Ähnlich wie bei der Quantisierung, die geformt wird, wird auch das Aliasing aufgrund von Sampling geformt. Dies führt zu einem fast nicht abtastenden ADC, der eine eigene Klasse bildet.

Die Abtastfrequenz des CTSD ist fest, im Gegensatz zum DTSD, wo die Abtastfrequenz des Modulators leicht skaliert werden kann. Außerdem ist bekannt, dass CTSD-ADCs weniger tolerant gegenüber Jitter sind als Äquivalente mit geschalteten Kondensatoren. Standard-Quarz- oder CMOS-Oszillatoren liefern lokal jitterarme Takte für ADCs, was dazu beiträgt, die Übertragung eines jitterarmen Takts über die Isolation zu vermeiden und die EMV zu reduzieren.

Die beiden Hauptvorteile von CTSD sind die inhärente Alias-Unterdrückung und die resistiven Eingänge für Signale und Referenz.

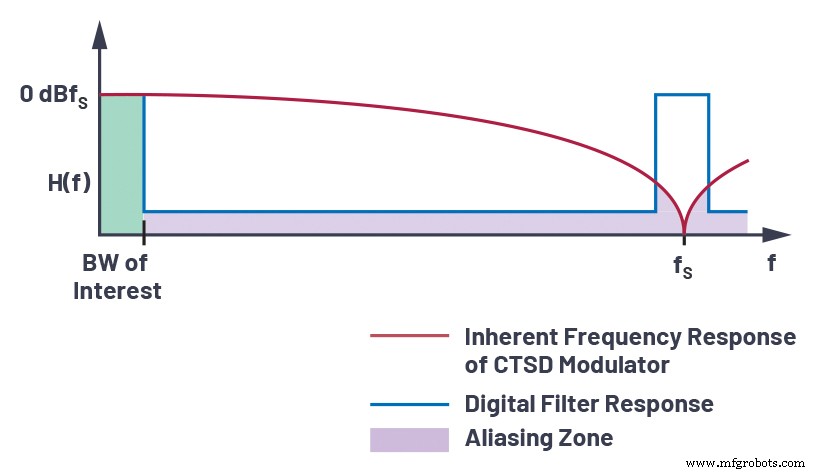

Inhärentes Antialiasing

Das Verschieben des Quantisierers innerhalb der Schleife führt zu einer inhärenten Alias-Unterdrückung. Wie in Abbildung 12 gezeigt, passiert das Eingangssignal den Schleifenfilter, bevor es abgetastet wird, und der am Quantisierer eingeführte Foldback-(Alias-)Fehler sieht auch diesen Filter. Das Signal und der Alias-Fehler haben dieselbe Rauschübertragungsfunktion wie die Sigma-Delta-Schleife, und beide haben eine ähnliche Rauschformung wie das Quantisierungsrauschen in Sigma-Delta-Architekturen. Somit weist der Frequenzgang der CTSD-Schleife natürlich Eingangssignale um ganzzahlige Vielfache der Abtastfrequenz zurück und wirkt als Antialiasing-Filter.

Klicken für größeres Bild

Abbildung 12. Frequenzgang eines CTSD-Modulators. (Quelle:Analog Devices)

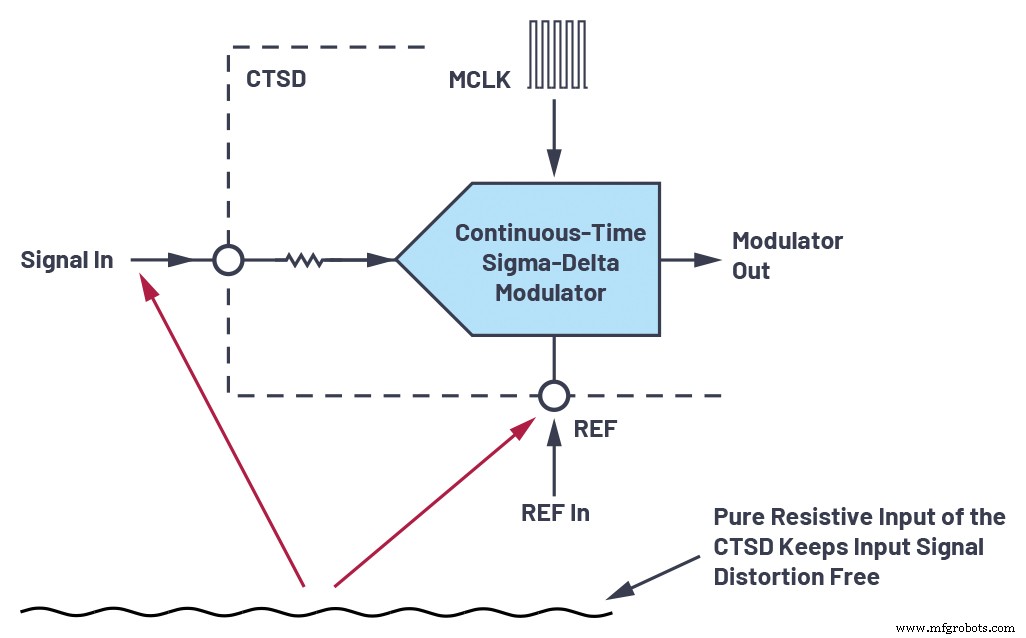

Widerstandseingabe

Widerstandseingänge an Signal- und Referenzeingängen machen die Ansteuerung einfacher als die Sample-and-Hold-Konfigurationen. Bei konstant ohmschen Eingängen gibt es keinen Rückschlag und der Treiber kann komplett entfernt werden. Der Eingang ist verzerrungsfrei, wie in Abbildung 13 gezeigt. Da der Eingangswiderstand konstant ist, entfällt auch die Neuabstimmung des Systems auf Verstärkungsfehler.

Klicken für größeres Bild

Abbildung 13. Eingangsabstimmung für CTSD. (Quelle:Analog Devices)

Analogeingänge können bipolar sein, obwohl der ADC unipolar versorgt wird. Dies kann die Notwendigkeit einer Pegelverschiebung von einem bipolaren Front-End zum ADC beseitigen. Die Gleichstromleistung des ADC ist möglicherweise nicht dieselbe, da der Eingangswiderstand jetzt neben dem Eingangsstrom auch einen gleichtaktabhängigen Eingangsstrom hat.

Die Referenzlast ist auch ohmsch, was den Schaltrückschlag reduziert, daher ist kein separater Referenzpuffer erforderlich. Der Widerstand für einen Tiefpassfilter kann auf dem Chip hergestellt werden, sodass er mit der ohmschen Last auf dem Chip (da sie aus dem gleichen Material sein könnten) mitlaufen kann, um die Temperaturdrift des Verstärkungsfehlers zu reduzieren.

Die CTSD-Architektur ist nicht neu, aber die Megatrends in den Industrie- und Instrumentierungsmärkten erfordern eine DC- und AC-Präzisionsleistung bei höheren Bandbreiten. Darüber hinaus bevorzugen Kunden ein einziges Plattformdesign, das den meisten ihrer Lösungen gerecht wird, um ihre Markteinführungszeit zu verkürzen.

Die CTSD-Architektur war aufgrund einer Reihe von Vorteilen gegenüber anderen Arten von ADCs die erste Wahl in einer Vielzahl von Anwendungen, die von Hochleistungs-Audio bis hin zum HF-Frontend von Mobiltelefonen reichen. Zu den Vorteilen gehören eine bessere Integrationsfähigkeit und ein geringer Stromverbrauch, aber auch, und möglicherweise noch wichtiger, weil die Verwendung eines CTSD eine Reihe wichtiger Probleme auf Systemebene löst. Aufgrund einer Reihe von technologischen Mängeln war die Verwendung von CTSD bisher auf die relative Audiofrequenz/Bandbreite und den unteren Dynamikbereich beschränkt. Daher sind Hochleistungs-Nyquist-Ratenwandler wie ADCs mit sukzessiver Approximation und überabgetastete DTSD-Wandler die Mainstream-Lösung für Präzisionsanwendungen mit hoher Leistung und mittlerer Bandbreite.

Die jüngsten technologischen Durchbrüche haben es jedoch ermöglicht, viele Einschränkungen zu überwinden. Der AD7134 von Analog Devices unterstützt beispielsweise hochpräzisen ADC mit einer Bandbreite von DC bis 400 kHz auf der Grundlage von CTSD, der wesentlich höhere Leistungsspezifikationen erreicht, während er gleichzeitig eine DC-Genauigkeit bietet und wiederum die Lösung einer Reihe wichtiger Probleme auf Systemebene in hohen Anwendungen zur Leistungsinstrumentierung. Der AD7134 integriert auch einen asynchronen Abtastratenwandler (ASRC), der Daten mit variablen Datenraten liefert, die von der festen Abtastgeschwindigkeit von CTSD abgeleitet werden. Die Ausgangsdatenrate kann unabhängig von der Modulator-Abtastfrequenz sein und kann eine erfolgreiche Verwendung von CTSD-ADCs für verschiedene granulare Durchsätze ermöglichen. Die Flexibilität, die Ausgabedatenrate auf granularer Ebene zu ändern, ermöglicht es Benutzern auch, kohärentes Sampling zu verwenden.

Die inhärente Alias-Unterdrückung macht einen Antialiasing-Filter überflüssig, was zu weniger Komponenten und einer kleineren Lösungsgröße führt. Noch wichtiger ist, dass Leistungsprobleme, die mit einem Antialiasing-Filter einhergehen, wie Droop, Fehler wie Offset, Verstärkung und Phasenfehler, sowie Rauschen im System nicht mehr vorhanden sind. Ein Antialiasing-Filter trägt je nach benötigter Unterdrückung auch erheblich zur Gesamtlatenz in der Signalkette bei. Das Entfernen des Filters beseitigt diese Verzögerung vollständig und ermöglicht eine präzise Umwandlung in verrauschten digitalen Regelkreisanwendungen.

Ohne Antialiasing-Filter auf Systemebene kann die Phasenanpassung in Mehrkanalsystemen erheblich verbessert werden. Dies ist besonders nützlich bei Anwendungen, die eine geringe Kanal-zu-Kanal-Fehlanpassung erfordern, wie z. B. Schwingungsüberwachung, Leistungsmessungen, Datenerfassungsmodule und Sonar. Aufgrund ihrer inhärenten Filterwirkung sind CTSD-ADCs auch gegen jede Art von Interferenz auf Systemebene sowie innerhalb des ICs selbst immun. Bei DTSD-ADCs und SAR-ADCs muss darauf geachtet werden, dass beim Abtasten des ADCs weniger Interferenzen auftreten. Außerdem wäre aufgrund der inhärenten Filterwirkung Immunität gegen Störungen auf Stromversorgungsleitungen gegeben. Mit konstanten ohmschen Analogeingängen und Referenzeingängen kann die Treiberanforderung ebenfalls vollständig beseitigt werden. Auch hier werden Leistungsprobleme wie Fehler wie Offset, Verstärkung, Phasenfehler und Rauschen des Systems behoben, die nicht mehr vorhanden sind.

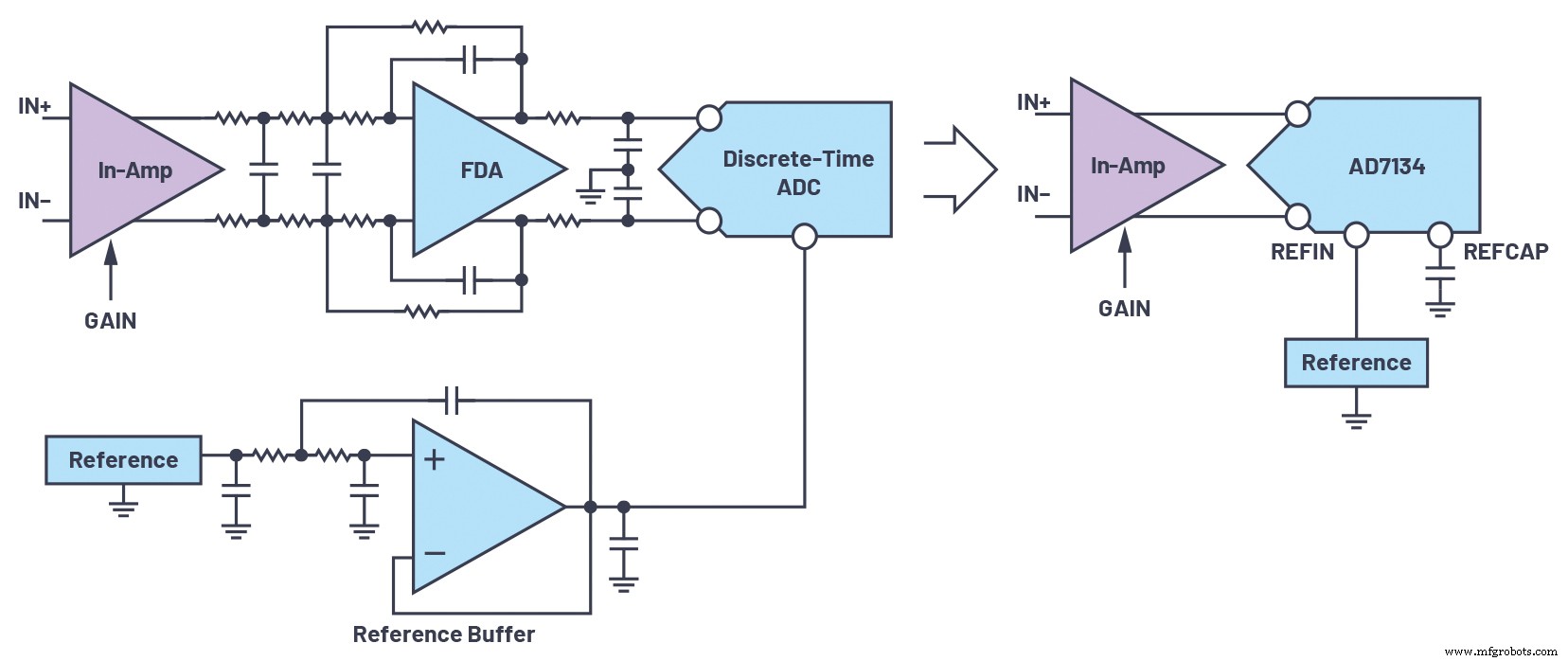

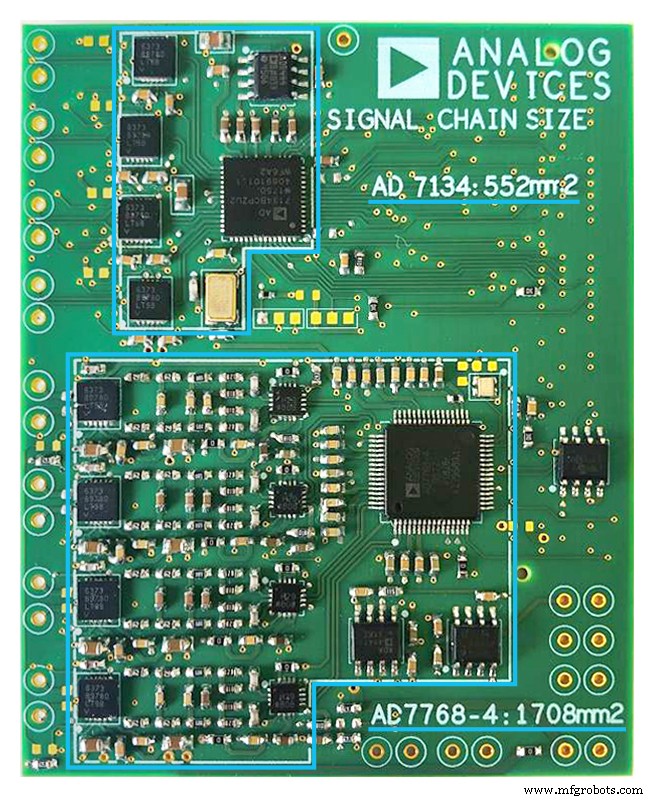

Der Kampf um die Präzisionsleistung ist sehr gering, da die Anzahl der entworfenen Elemente erheblich reduziert wird. Dies führt zu einer schnelleren Konstruktionszeit, einer schnelleren Markteinführungszeit für Kunden, einer einfacheren Stücklistenverwaltung und einer Zuverlässigkeit. Das Entfernen eines Antialiasing-Filters, eines Treibers und eines Referenzpuffers verringert die Systemplatinenfläche erheblich. Ein Instrumentenverstärker kann verwendet werden, um den ADC direkt anzusteuern. Da es sich beispielsweise beim AD7134 um einen reinen Differenzeingangs-ADC handelt, kann ein Differenzeingangsverstärker wie der LTC6373 als Treiber verwendet werden. Der Vergleich in Abbildung 14 zeigt die Signalkette für eine zeitdiskrete Signalkette und eine zeitkontinuierliche Signalkette. Unser Experiment zeigt 70 % der Flächeneinsparungen im Vergleich zu einer entsprechenden zeitdiskreten Signalkette, was es zu einer ausgezeichneten Wahl für Mehrkanalanwendungen mit hoher Dichte macht.

Zusammenfassend lässt sich sagen, dass dieser Ansatz eine erhebliche Reduzierung der Systemgröße bietet, das Design der Signalkette vereinfacht, das System robuster macht und die Gesamtzeit bis zur Markteinführung durch einfaches Design-In verkürzt, ohne Leistungsparameter einzutauschen, die von Präzisionsinstrumentierungsanwendungen gefordert werden.

Klicken für größeres Bild

Abbildung 14. Ein zeitdiskreter (links) und ein zeitkontinuierlicher (rechts) Signalkettenvergleich. (Quelle:Analog Devices)

Klicken für größeres Bild

Abbildung 15. Größenvergleich von zeitdiskreter und zeitkontinuierlicher Signalkette. (Quelle:Analog Devices)

Referenzen

Kester, Walt. „MT-002:Was das Nyquist-Kriterium für Ihr Stichprobendatensystemdesign bedeutet.“ Analog Devices, Inc., 2009.

Pavan, Shanti. „Alias-Unterdrückung von zeitkontinuierlichen Δ∑-Modulatoren mit DACs mit geschalteter Kondensator-Rückkopplung.“ IEEE-Transaktionen auf Schaltkreisen und Systemen I:Regelmäßige Papiere , Bd. 58, Nr. 2, Februar 2011.

Schreier, Richard und Gabor C. Temes. Delta-Sigma-Datenkonverter verstehen. John Wiley und Söhne, 2005.

Danksagungen

Der Autor möchte Abhilasha Kawle, Avinash Gutta und Roberto Maurino für ihre Unterstützung bei diesem Artikel danken.

Eingebettet

- Begriffe und Konzepte des digitalen Speichers

- C#-Variablen und (primitive) Datentypen

- Python-Typkonvertierung und Typumwandlung

- Semaphoren:Versorgungsdienste und Datenstrukturen

- Apacer:CV110-SD- und CV110-MSD-Karten weltweit eingeführt

- Swissbit:hardwarebasierte Sicherheitslösungen zum Schutz von Daten und Geräten

- Hyperkonvergenz und Sekundärspeicher:Teil 2

- Aufbau einer verantwortungsvollen und vertrauenswürdigen KI

- Blockchain und Lieferketten:Das Potenzial freisetzen

- Die Bedeutung von Data Fabrics – und wie sie Lieferketten zugute kommen