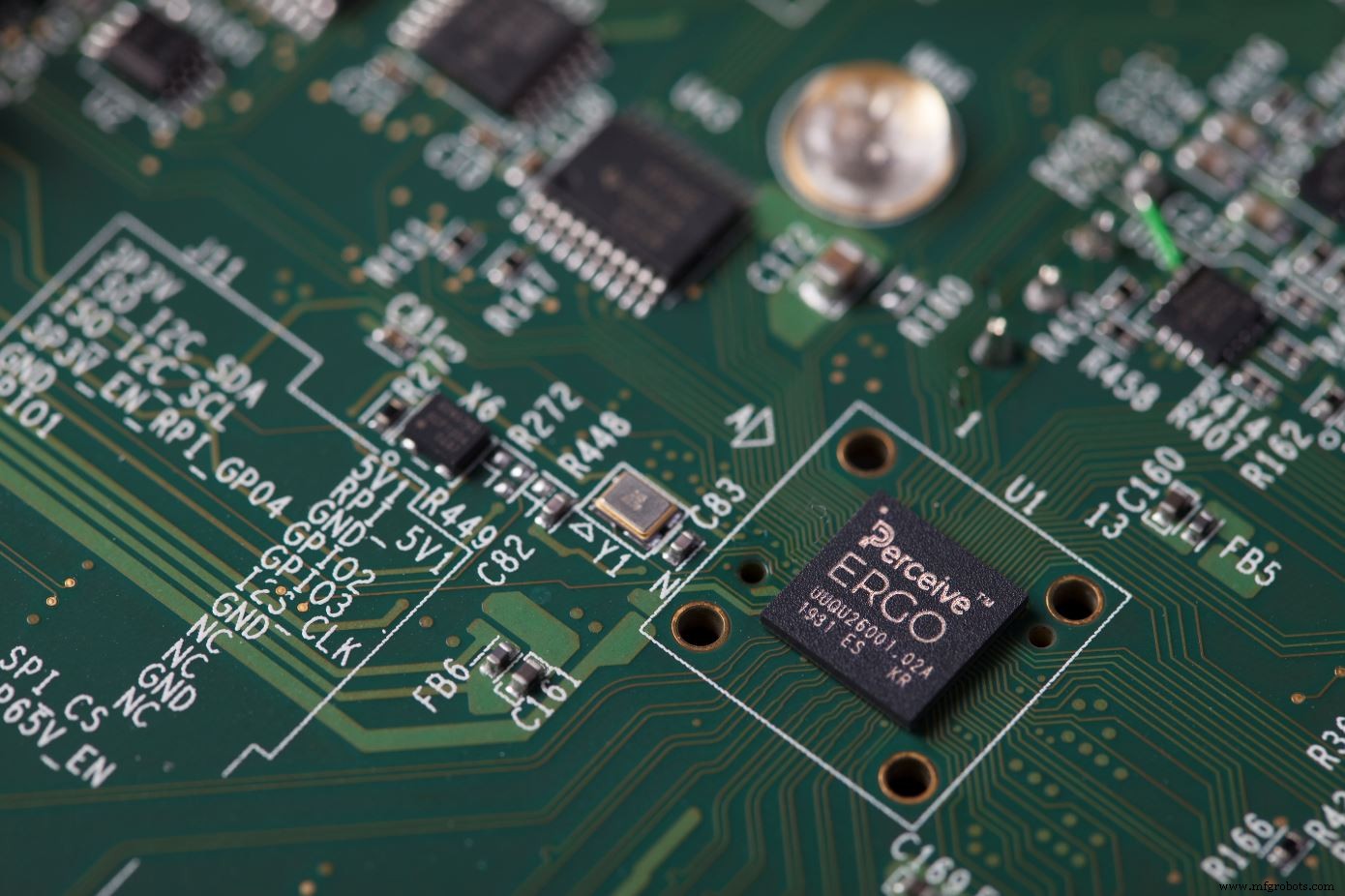

Edge AI-Chip verzichtet auf Multiply-Accumulate-Array, um 55 TOPS/W zu erreichen

Ein Startup aus dem Silicon Valley behauptet, es habe die Mathematik neuronaler Netze neu erfunden und einen komplementären Edge-KI-Chip produziert, der bereits Sampling hat, der nicht die übliche große Anzahl von Multiplikator-Einheiten verwendet. Der Chip kann das Äquivalent von 4 TOPS bei einem beeindruckenden Stromverbrauch von 55 TOPS/W ausführen und erreicht nach Angaben des Unternehmens Inferenz der Rechenzentrumsklasse in unter 20 mW (YOLOv3 bei 30 fps).

Perceive aus San Jose war bisher im Super-Stealth-Modus – als Spin-out von Xperi wurde es seit der offiziellen Gründung vor zwei Jahren vollständig von seiner Muttergesellschaft finanziert. Das Team besteht aus 41 Personen, wobei eine ähnliche Anzahl innerhalb von Xperi an Apps für den Chip arbeitet. Gründungs-CEO Steve Teig ist auch CTO von Xperi; Zuvor war er Gründer und CTO von Tabula, dem Startup für programmierbare 3D-Logik, das vor fünf Jahren seine Pforten geschlossen hat, und davor CTO von Cadence.

Teig erklärte, dass die ursprüngliche Idee darin bestand, das klassische Wissen von Xperi in der Bild- und Audioverarbeitung mit maschinellem Lernen zu kombinieren. Xperi besitzt Marken wie DTS, IMAX Enhanced und HD Radio — sein Technologieportfolio umfasst Bildverarbeitungssoftware für Funktionen wie Rote-Augen-Foto und Bildstabilisierung, die in Digitalkameras weit verbreitet sind, sowie Audioverarbeitungssoftware für Blu-Ray-Disc-Player.

Steve Teig (Bild:Wahrnehmen)

„Wir begannen mit einem leeren Blatt Papier und stellten mithilfe der Informationstheorie die Frage:Welche Berechnungen führen neuronale Netze eigentlich durch? Und gibt es eine andere Herangehensweise an diese Berechnung, die ändern könnte, was [am Rand] möglich ist?“ sagte Teig. „Nachdem wir diese Arbeit ein paar Jahre lang gemacht hatten, stellten wir fest, dass dies der Fall war und entschieden uns dann … wir sollten einen Chip herstellen, der diese Ideen verkörpert.“

Die Idee, die Teig dem Xperi-Vorstand präsentierte, bestand darin, ein Unternehmen auszugliedern, um einen Chip herzustellen, der in Edge-Geräten mit einem Leistungsbudget von 20 mW sinnvolle Rückschlüsse ziehen kann. Das Ergebnis, ein 7x7-mm-Chip namens Ergo, kann 4 TOPS ohne externen RAM ausführen (tatsächlich läuft er mit dem, was eine GPU mit 4 TOPS erreichen kann, erklärte Teig). Ergo unterstützt viele Arten neuronaler Netze, einschließlich Faltungsnetze (CNNs) und rekurrente Netze (RNNs), im Gegensatz zu vielen Lösungen auf dem Markt, die auf CNNs zugeschnitten sind. Ergo kann sogar mehrere heterogene Netzwerke gleichzeitig betreiben.

„Das einzige, was die Anzahl der Netzwerke, die wir betreiben können, einschränkt, ist der Gesamtspeicher, der für die Kombination benötigt wird“, sagte Teig und fügte hinzu, dass Perceive gezeigt hat, dass YOLOv3 oder M2Det gleichzeitig ausgeführt werden – mit 60 oder 70 Millionen Parametern – plus ResNet 28 mit mehreren Millionen Parameter sowie ein LSTM oder RNN für die Sprach- und Audioverarbeitung. In einer Anwendung kann dies gleichzeitig Bild- und Audioinferenz entsprechen.

Perceive behauptet auch, dass sein Ergo-Chip außergewöhnlich energieeffizient ist und 55 TOPS/W erreicht. Diese Zahl liegt eine Größenordnung über dem, was einige Wettbewerber behaupten. Laut den Zahlen von Perceive läuft YOLOv3, ein großes Netzwerk mit 64 Millionen Parametern, mit 30 Bildern pro Sekunde bei einem Verbrauch von nur 20 mW.

Perceive behauptet, dass die Effizienz seines Ergo-Chips bis zu 55 TOPS/W beträgt und YOLOv3 bei 30 fps mit nur 20 mW läuft (Bild:Perceive)

Diese Energieeffizienz ist auf einige aggressive Power-Gating- und Clock-Gating-Techniken zurückzuführen, die die deterministische Natur der neuronalen Netzwerkverarbeitung ausnutzen – im Gegensatz zu anderen Codearten gibt es keine Verzweigungen, sodass die Timings zur Kompilierzeit bekannt sind. Dadurch kann Perceive genau erkennen, was wann eingeschaltet werden muss.

„In einer batteriebetriebenen Einstellung kann [der Chip] buchstäblich ausgeschaltet sein – null Milliwatt – und eine Art Mikrowatt-Bewegungssensor oder ein analoges Mikrofon haben, um etwas zu erkennen, das von Interesse sein könnte“, sagte Teig. „Wir können aus dem Off aufwachen, ein riesiges neuronales Netzwerk der Rechenzentrumsklasse laden und es in etwa 50 Millisekunden ausführen, einschließlich Entschlüsselung. Wir lassen also nur etwa zwei Videobilder auf dem Boden.“

Aber sorgfältiges Hardware-Design ist nur ein Teil des Bildes.

Informationstheorie

„Wir haben uns eine andere Art ausgedacht, die zugrunde liegende Berechnung selbst und die damit verbundene Arithmetik darzustellen“, sagte Teig. „Wir repräsentieren das Netzwerk selbst auf eine neue Art und Weise, und das ist unser Vorteil.“

Perceive begann mit der Informationstheorie – einem Zweig der Wissenschaft, der mathematische Methoden zur Unterscheidung von Signalen von Rauschen umfasst – und verwendete ihre Konzepte, um zu untersuchen, wie viel Rechenleistung erforderlich ist, um das Signal aus dem Rauschen zu ziehen. Teig verwendet als Beispiel ein Objekterkennungsnetzwerk.

„Du übergibst dem Netzwerk Millionen von Pixeln und alles was du wissen willst ist, ist auf diesem Bild ein Hund oder nicht?“ er sagte. „Alles andere auf dem Bild ist Rauschen, außer Dogness [das Signal]. Die Informationstheorie macht es quantifizierbar – wie viel muss man wissen [um zu sagen, ob ein Hund auf dem Bild ist]? Man kann es sogar mathematisch präzise machen.“

Wie Teig es beschreibt, können neuronale Netze des Mainstreams auf der Grundlage vieler Bilder von Hunden verallgemeinern, weil sie zumindest einen Teil des Signals im Rauschen gefunden haben, aber dies geschah auf empirische Weise und nicht mit einem mathematisch rigorosen Ansatz. Dies bedeutet, dass Rauschen mit dem Signal übertragen wird, wodurch die gängigen neuronalen Netze sehr groß und anfällig für gegnerische Beispiele und andere Tricks werden.

„Je mathematischer Sie herausfinden können, welche Teile aufbewahrt werden müssen und welche nur Rauschen sind, desto besser können Sie bei der Verallgemeinerung arbeiten und desto weniger Aufwand müssen Sie mit sich führen“, sagte Teig. „Ich würde behaupten, dass sogar aktuelle neuronale Netze Signale aus Rauschen extrahieren, aber sie tun es nicht so streng und tragen daher zusätzliches Gewicht mit sich.“

Diese informationstheoretische Sichtweise ist die Grundlage für die Machine-Learning-Strategie von Perceive, die neuronale Netze auf neue Weise darstellt.

„Dies ist wirklich eine Verbindung zwischen einer informationstheoretischen Perspektive auf maschinelles Lernen und einem Chip, der diese Ideen verkörpert“, sagte Teig.

Chiparchitektur

Mit Teigs Hintergrund als CTO von Tabula könnte man Hardware erwarten, die auf programmierbarer Logik basiert, aber das ist hier nicht der Fall.

„Ich bin seit einem Jahrzehnt stark davon beeinflusst, über programmierbare Logik nachzudenken und wie man reichhaltige Verbindungsarchitekturen baut, um hochperformante, sehr parallele Berechnungen zu ermöglichen, da vieles von dem, was auf einem FPGA passiert, massiv parallel und sehr intensiv ist Interaktion zwischen Rechenleistung und Speicher“, sagte Teig. „Diese Arbeit hat meine Arbeit bei Perceive definitiv beeinflusst, aber was wir haben, ist keine programmierbare Logik per se . Es wurde von dieser Denkweise beeinflusst, aber die Architektur selbst basiert auf neuronalen Netzen.“

Die neuronale Netzwerkstruktur von Perceive ist skalierbar, wobei der anfängliche Chip Ergo über vier Rechencluster mit jeweils eigenem Speicher verfügt. Während genaue Details noch unter Verschluss sind, sagte Teig, dass sich diese Cluster deutlich von allem unterscheiden, was in anderen KI-Beschleunigern zu finden ist, die normalerweise Arrays von Multiply-Accumulate-Einheiten (MACs) verwenden, um Punktprodukte von Vektoren und Matrizen zu berechnen.

Die Technologie von Perceive basiert auf der Neuerfindung neuronaler Netzmathematik unter Verwendung von Techniken der Informationstheorie (Bild:Perceive)

„Das machen wir nicht“, sagte Teig. „Wir haben kein Array von MACs. Als Ergebnis sind wir 20- bis 100-mal so energieeffizient wie alles andere auf dem Markt, der Grund dafür ist, dass alle anderen dasselbe tun und wir nicht. Unsere Darstellung der Netze ist recht neu, und das hat uns zu einer so hohen Effizienz verholfen. Dazu kommt die Machine-Learning-Technologie, die diese Darstellung der Netzwerke finden und die Netzwerke so trainieren kann, dass sie mit dem kompatibel sind, was der Chip sehen möchte.“

Bild und Ton

Ergo kann zwei Kameras unterstützen und enthält eine Bildverarbeitungseinheit, die als Vorprozessor arbeitet und Dinge wie das Entzerren von Fischaugenobjektivbildern, Gammakorrektur, Weißabgleich und Zuschneiden verarbeitet.

"Es ist nicht schick, aber die Vorverarbeitung, die bei Hardware offensichtlich nützlich ist, machen wir in Hardware", sagte Teig. „Und wir haben auch das Audio-Äquivalent – wir können zum Beispiel mehrere Stereomikrofone verwenden und Beamforming durchführen.“

Es gibt auch einen Synopsis ARC-Mikroprozessor mit einem DSP-Block, der auch für die Vorverarbeitung verwendet werden kann, sowie einen Sicherheitsblock, ebenfalls von Synopsis.

„Eines der Dinge, die wir getan haben, ist, absolut alles zu verschlüsseln, um ein Sicherheitsniveau in einer IoT-Umgebung aufrechtzuerhalten. Wir verschlüsseln die Netzwerke, verschlüsseln den Code, der auf dem Mikroprozessor läuft, verschlüsseln die Schnittstellen, verschlüsseln alles“, sagte Teig.

Der Chip verfügt über entsprechende I/Os für Sensoren außerhalb von Bild und Audio und unterstützt einen externen Flash-Speicher und/oder Mikroprozessor, der Over-the-Air-Updates ermöglicht. Dies könnte verwendet werden, um die auf dem Chip geladenen neuronalen Netze zu aktualisieren oder nach Bedarf verschiedene Netze zu laden.

Ergo bemustert jetzt zusammen mit einer begleitenden Referenztafel. Die Massenproduktion wird im 2. Quartal 2020 erwartet.

Eingebettet

- Entwerfen mit Bluetooth Mesh:Chip oder Modul?

- KI-Chiparchitektur zielt auf die Grafikverarbeitung ab

- Kleines Bluetooth 5.0-Modul integriert Chipantenne

- Kleines KI-Modul baut auf Google Edge TPU auf

- Forscher bauen winzige Authentifizierungs-ID-Tags

- Debüts des bildgebenden Radarprozessors für die Automobilindustrie mit 30 fps

- Low-Power-Radarchip verwendet neuronale Spiking-Netzwerke

- Smart Sensor Board beschleunigt die Entwicklung von Edge-KI

- Smart-Kamera bietet schlüsselfertige Edge Machine Vision Edge-KI

- Bericht:Chipknappheit und Edge/IoT werden den IT-Wandel im Jahr 2022 vorantreiben