Das „Puffer“-Tor

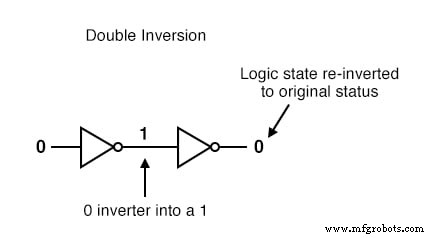

Wenn wir zwei Inverter-Gates miteinander verbinden würden, so dass der Ausgang des einen in den Eingang eines anderen gespeist wird, würden sich die beiden Inversionsfunktionen gegenseitig "aufheben", so dass es keine Inversion vom Eingang zum endgültigen Ausgang gibt:

Dies mag zwar sinnlos erscheinen, hat jedoch eine praktische Anwendung. Denken Sie daran, dass Gate-Schaltungen Signal-Verstärker sind , unabhängig davon, welche logische Funktion sie ausführen können.

Eine schwache Signalquelle (eine, die nicht in der Lage ist, sehr viel Strom zu einer Last zu liefern oder zu ziehen) kann mit zwei Wechselrichtern wie dem in der vorherigen Abbildung gezeigten Paar verstärkt werden. Der Logikpegel bleibt unverändert, aber die vollen Stromliefer- oder -senkfähigkeiten des letzten Wechselrichters stehen zur Verfügung, um bei Bedarf einen Lastwiderstand zu treiben.

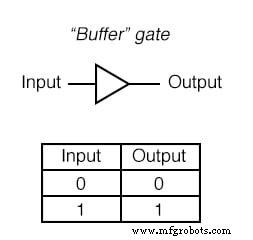

Zu diesem Zweck wird ein spezielles Logikgatter namens Puffer wird hergestellt, um die gleiche Funktion wie zwei Wechselrichter zu erfüllen. Sein Symbol ist einfach ein Dreieck ohne invertierende „Blase“ am Ausgangsanschluss:

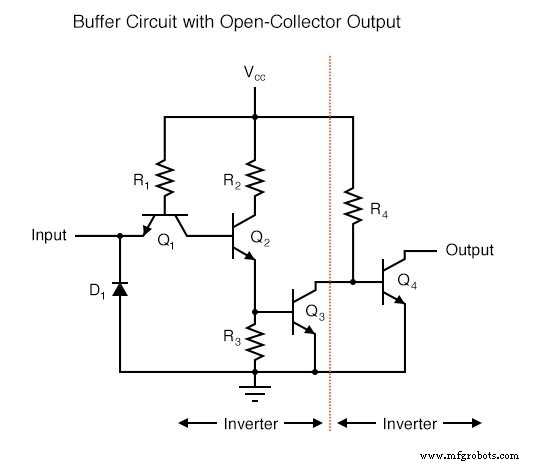

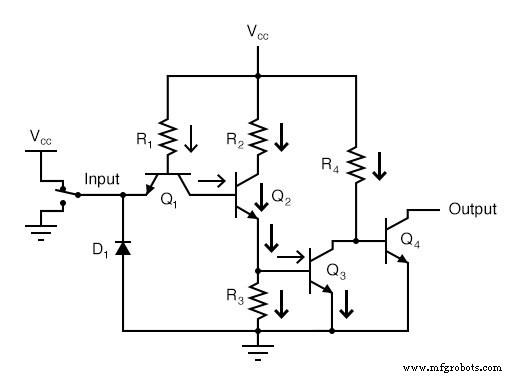

Pufferschaltung mit Open-Collector-Ausgang

Der interne Schaltplan eines typischen Open-Collector-Puffers unterscheidet sich nicht wesentlich von dem eines einfachen Inverters:Es wird nur eine weitere Transistorstufe mit gemeinsamem Emitter hinzugefügt, um das Ausgangssignal erneut zu invertieren.

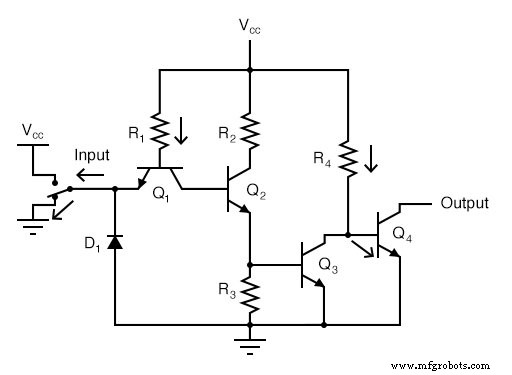

„Hohe“ Eingangsanalyse

Lassen Sie uns diese Schaltung auf zwei Bedingungen hin analysieren:einen logischen Eingangspegel von „1“ und einen logischen Eingangspegel von „0“. Zuerst ein „high“ (1) Eingang:

Wie zuvor bei der Inverterschaltung bewirkt der „high“-Eingang keine Leitung durch die linke Steuerdiode von Q1 (Emitter-Basis-PN-Übergang). Der gesamte Strom von R1 fließt durch die Basis des Transistors Q2 und sättigt ihn:

Wenn Q2 gesättigt ist, wird auch Q3 gesättigt, was zu einem sehr geringen Spannungsabfall zwischen der Basis und dem Emitter des letzten Ausgangstransistors Q4 führt. Somit befindet sich Q4 im Abschaltmodus und leitet keinen Strom.

Der Ausgangsanschluss ist schwebend (weder mit Masse noch mit Vcc verbunden), und dies entspricht einem „High“-Zustand am Eingang des nächsten TTL-Gatters, in das dieses einspeist. Somit ergibt ein „hoher“ Eingang einen „hohen“ Ausgang.

„Niedrige“ Input-Analyse

Bei einem „niedrigen“ Eingangssignal (Eingangsklemme geerdet) sieht die Analyse etwa so aus:

Der gesamte Strom von R1 wird jetzt durch den Eingangsschalter umgeleitet, wodurch der Basisstrom durch Q2 eliminiert wird. Dies zwingt den Transistor Q2 zum Abschalten, so dass auch kein Basisstrom durch Q3 fließt.

Wenn auch Q3 abgeschaltet wird, wird Q4 durch den Strom durch den Widerstand R4 gesättigt, wodurch der Ausgangsanschluss mit Masse verbunden wird, was ihn zu einem "niedrigen" Logikpegel macht. Somit ergibt ein „niedriger“ Eingang einen „niedrigen“ Ausgang.

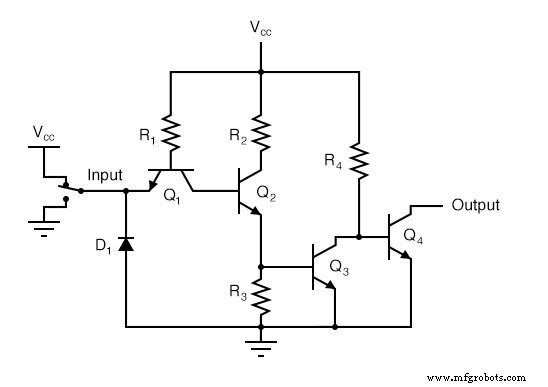

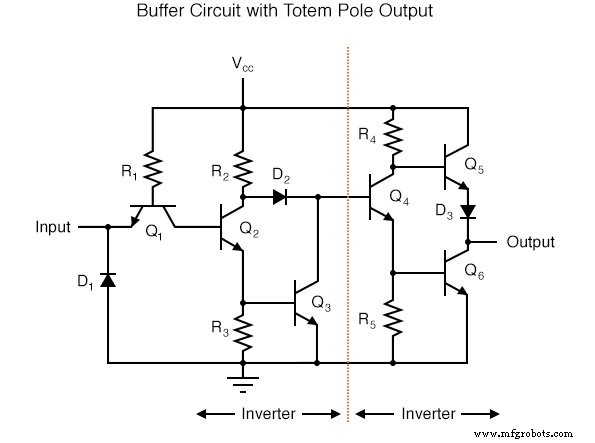

Schematische Darstellung mit Totem-Pole-Ausgangstransistoren

Der Schaltplan für eine Pufferschaltung mit Totempfahl-Ausgangstransistoren ist etwas komplexer, aber die Grundprinzipien und sicherlich die Wahrheitstabelle sind die gleichen wie für die Open-Collector-Schaltung:

RÜCKBLICK:

- Zwei Inverter- oder NICHT-Gatter, die in "Reihe" geschaltet sind, um ein binäres Bit zu invertieren und dann wieder zu invertieren, erfüllen die Funktion eines Puffers. Puffergatter dienen lediglich der Signalverstärkung:Sie nehmen eine „schwache“ Signalquelle, die nicht in der Lage ist, viel Strom zu liefern oder zu ziehen, und erhöht die Stromkapazität des Signals, um eine Last antreiben zu können.

- Pufferschaltungen werden durch ein Dreiecksymbol ohne Wechselrichter-„Blase“ symbolisiert.

- Puffer können wie Wechselrichter als Open-Collector-Ausgang oder als Totempfahl-Ausgangsform hergestellt werden.

VERWANDTES ARBEITSBLATT:

- TTL Logic Gates-Arbeitsblatt

Industrietechnik