Verwenden von Integrated Logic Analyzer (ILA) und Virtual Input/Output (VIO)

Dieses Tutorial behandelt die Verwendung des Integrated Logic Analyzer (ILA) und Virtuelle Eingabe/Ausgabe (VIO) Cores zum Debuggen und Überwachen Ihres VHDL-Designs in der Xilinx Vivado IDE.

In vielen Fällen müssen Designer eine On-Chip-Verifizierung durchführen. Das heißt, Zugriff auf das Verhalten eines internen Signals in ihrem FPGA-Design zu Verifizierungszwecken zu erhalten.

Eine Möglichkeit besteht darin, diese Signale zu den FPGA-Pins zu bringen und sie mit LEDs zu verbinden, um ihr Verhalten visuell zu sehen. Diese Option ist einfach, schnell und funktioniert gut für einfache Fälle, aber sie ist nicht flexibel, skalierbar oder realistisch.

Eine weitere Option ist ein externer Logikanalysator mit erweiterten Funktionen, der das Verhalten dieser Signale anzeigen und darstellen kann, aber dafür sind externe und relativ teure Geräte erforderlich.

Der Integrierte Logikanalysator (ILA) ist eine Alternative, die die Vorteile der beiden vorherigen Optionen kombiniert. Es ist einfach, schnell, flexibel und verfügt über viele erweiterte Funktionen, mit denen Designer das Verhalten der ausgewählten Signale schnell anzeigen und überprüfen können.

Übersicht

Dieser Artikel enthält mehrere Screenshots der Vivado-GUI. Klicken Sie auf die Bilder, um sie zu vergrößern!

Verwenden Sie die Seitenleiste, um durch die Gliederung zu navigieren für dieses Tutorial oder scrollen Sie nach unten und klicken Sie auf die Pop-up-Navigationsschaltfläche in der oberen rechten Ecke, wenn Sie ein Mobilgerät verwenden.

ILA und VIO

ILA und VIO sind kostenlos anpassbare IPs von Xilinx. Das ILA IP hilft Ihnen, interne Signale in Ihrem FPGA einfach zu untersuchen und sie in eine simulationsähnliche Umgebung zu bringen, um sie zu überwachen und ihr Verhalten zu überprüfen.

Im Gegensatz zu ILA ermöglicht Ihnen das VIO IP, interne Signale in Ihrem FPGA virtuell anzusteuern, um Ihr Design zu stimulieren oder zu steuern, wie z. B. das Ansteuern des RESET-Signals.

- Geistiges Eigentum von Xilinx:Integrierter Logikanalysator (ILA)

- Geistiges Eigentum von Xilinx:Virtuelle Eingabe/Ausgabe (VIO)

Anforderungen

- Ein Xilinx FPGA-Board

- Die Vivado Design Suite

- Grundlegende VHDL-Kenntnisse

Ich verwende das Kintex-7 FPGA KC705 Evaluierungskit, aber die in diesem Tutorial gezeigten Methoden sollten auf jedem modernen Xilinx FPGA-Board funktionieren.

Beispielprojekt herunterladen

Sie können das Beispielprojekt und den VHDL-Code über das untenstehende Formular herunterladen. Es sollte in Vivado Version 2020.2 oder neuer funktionieren.

Extrahieren Sie die ZIP-Datei und öffnen Sie die ila_tutorial.xpr Datei in Vivado, um das Beispieldesign anzuzeigen, oder lesen Sie den Rest dieses Artikels, um zu erfahren, wie Sie es von Grund auf neu erstellen.

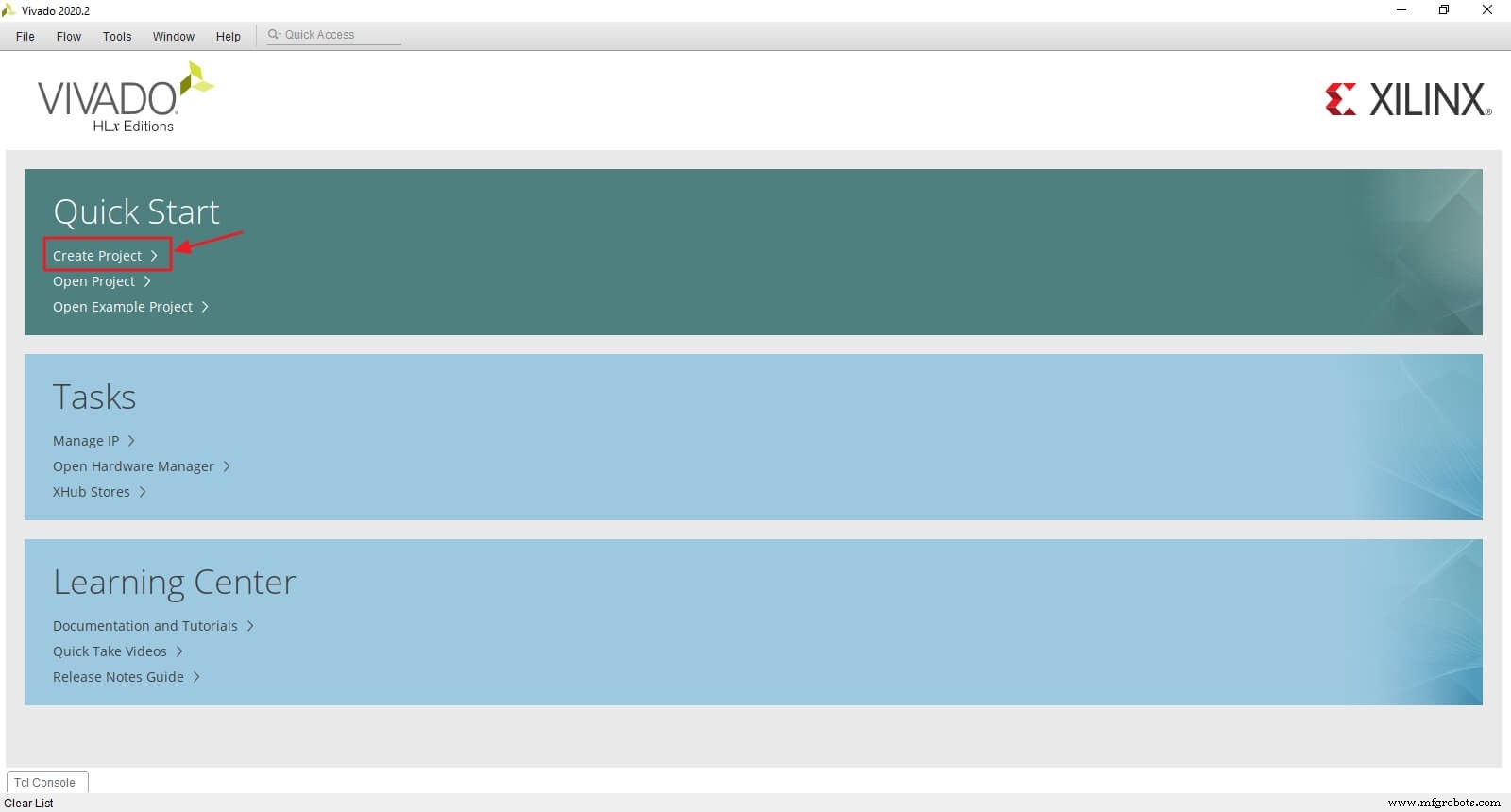

Projekt mit Vivado erstellen

Öffnen Sie zunächst Vivado. Klicken Sie im Begrüßungsbildschirm von Vivado auf Projekt erstellen Schaltfläche.

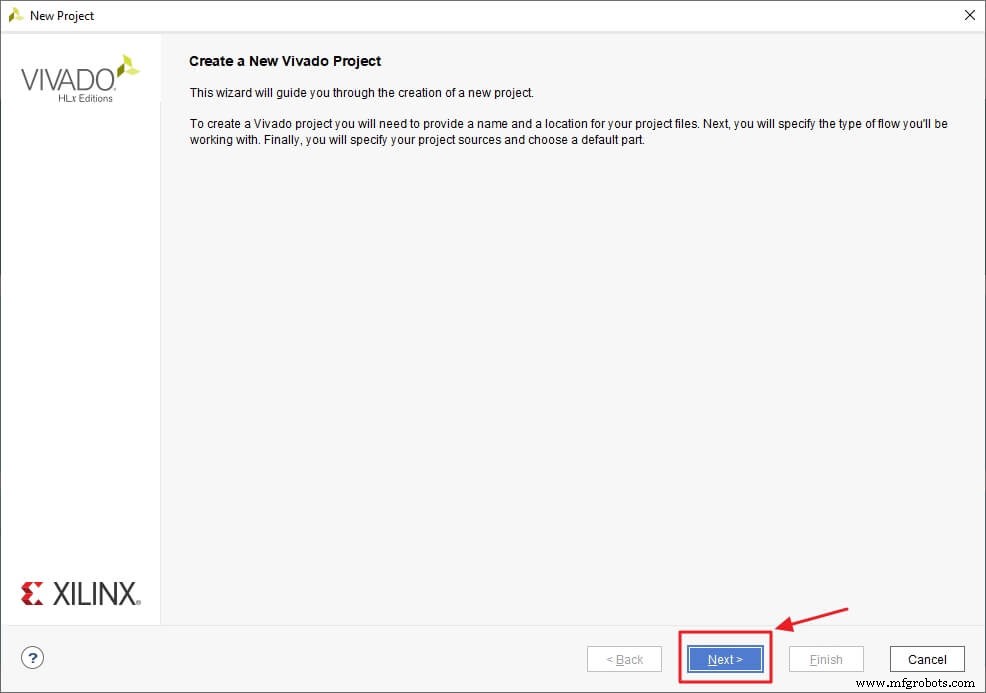

Klicken Sie auf Weiter um fortzufahren.

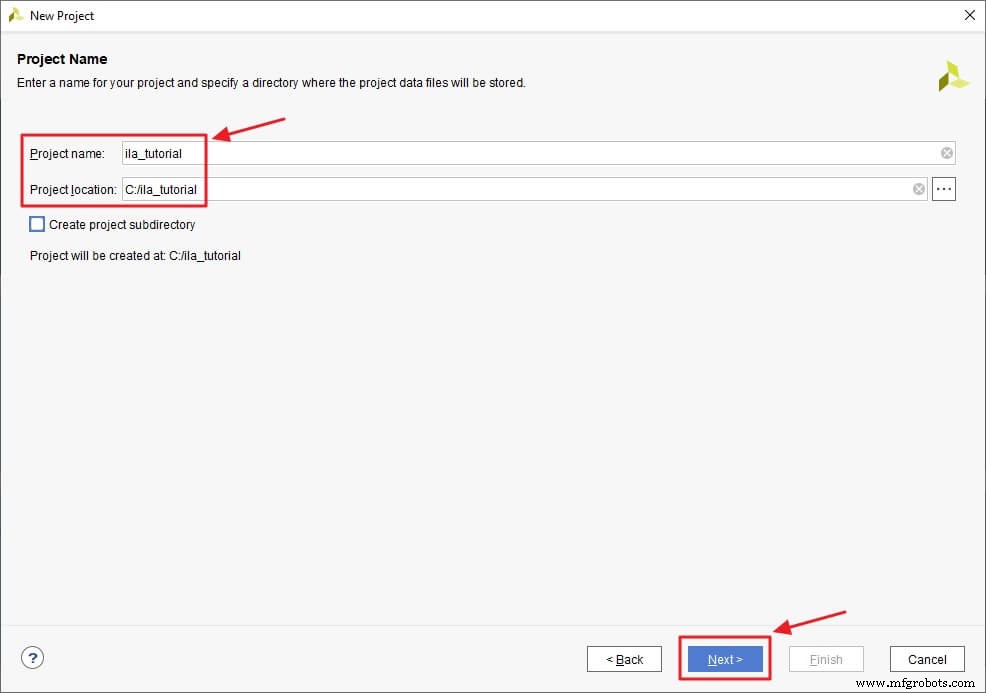

Ändern Sie den Namen des Projekts in ila_tutorial und klicken Sie auf Weiter.

Hinweis: Verwenden Sie keine Leerzeichen im Projektnamen. Verwenden Sie stattdessen einen Unterstrich oder Bindestrich.

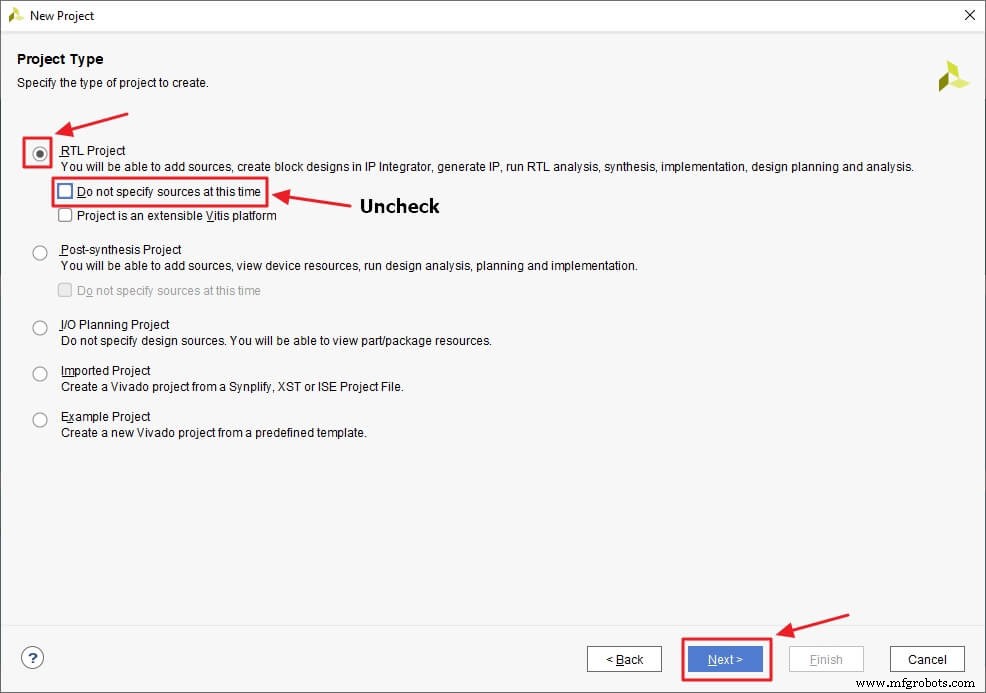

Wählen Sie RTL-Projekt aus und deaktivieren Sie Zu diesem Zeitpunkt keine Quellen angeben und klicken Sie auf Weiter um fortzufahren.

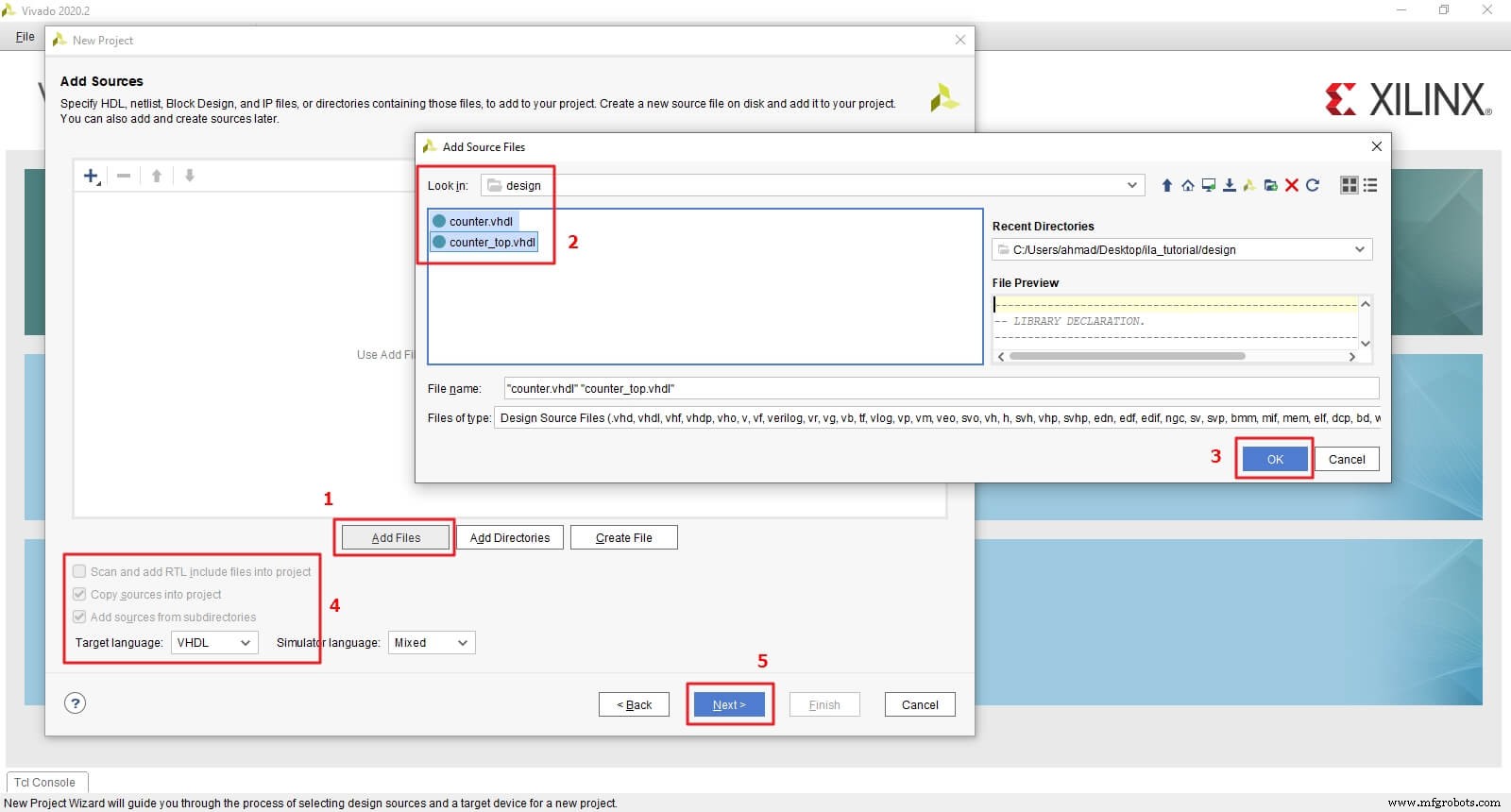

Fügen Sie die Quelldateien hinzu; counter.vhdl und counter_top.vhdl aus dem Designordner. Wählen Sie VHDL für die Zielsprache. Aktivieren Sie Quellen in Projekt kopieren und klicken Sie auf Weiter um fortzufahren.

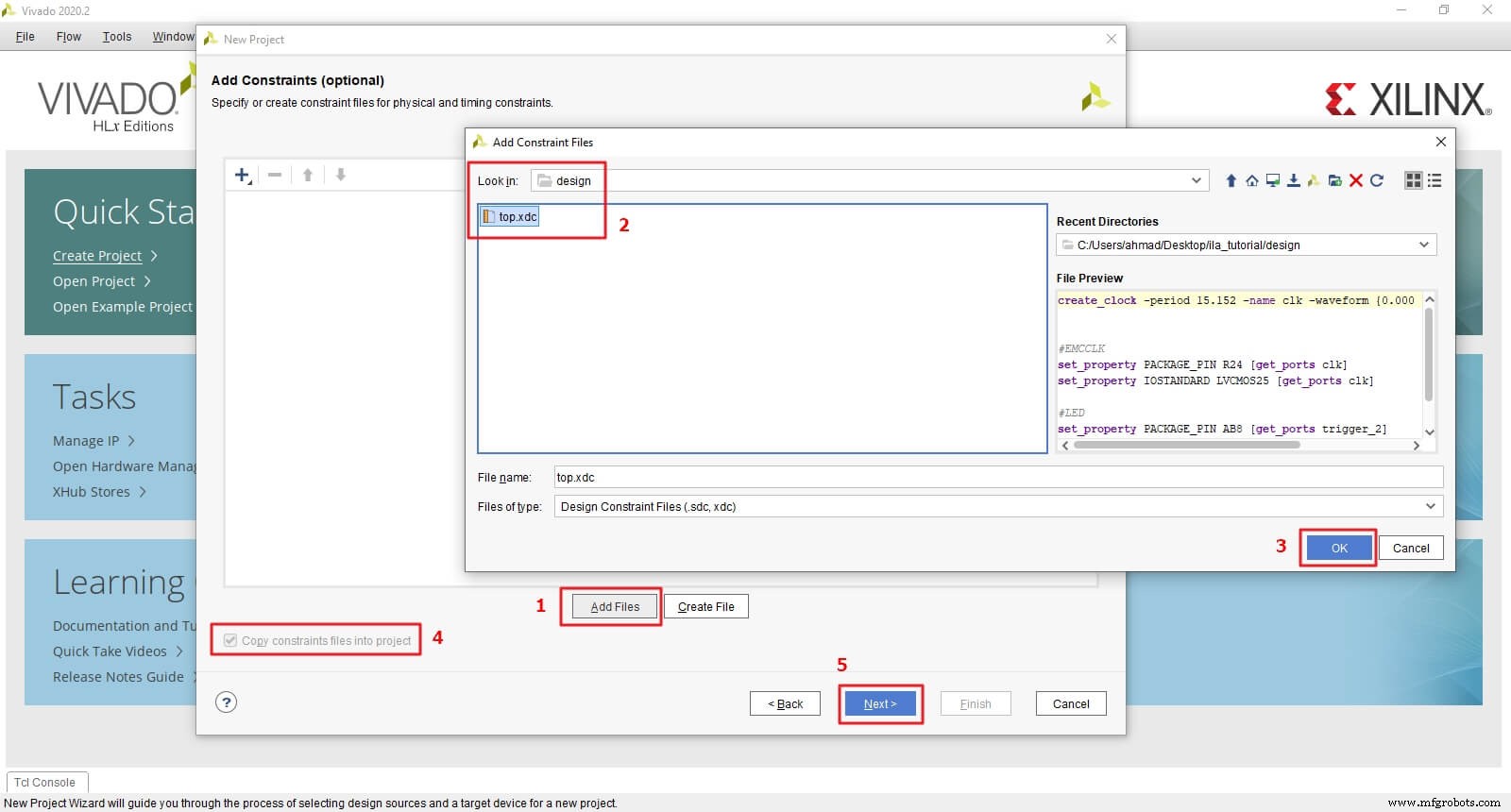

Fügen Sie die Beschränkungsdatei top.xdc hinzu aus dem Designordner. Aktivieren Sie Beschränkungsdateien in Projekt kopieren und klicken Sie auf Weiter um fortzufahren.

Hinweis: Diese Einschränkungsdatei ist spezifisch für das KC705-Board. Sie müssen den clk-Pin ändern und der LED-Stift nach deinem Board. Und auch der -Zeitpunkt Ihrer Borduhr.

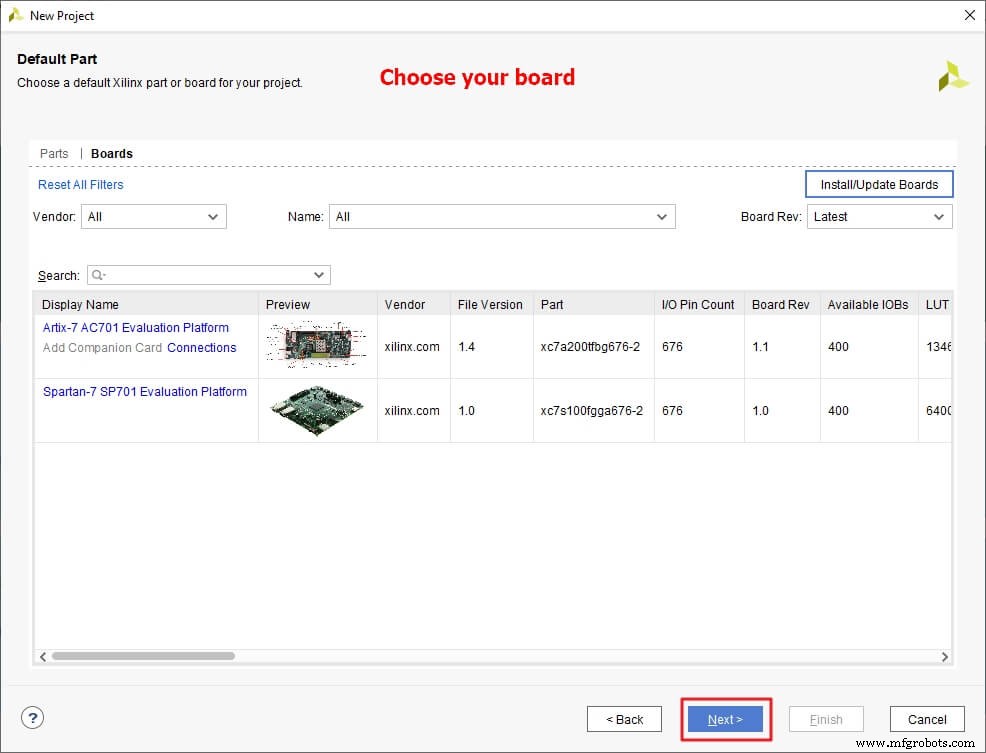

Suchen Sie nach Ihrem Board und wählen Sie es aus der Liste aus. Klicken Sie auf Weiter um fortzufahren.

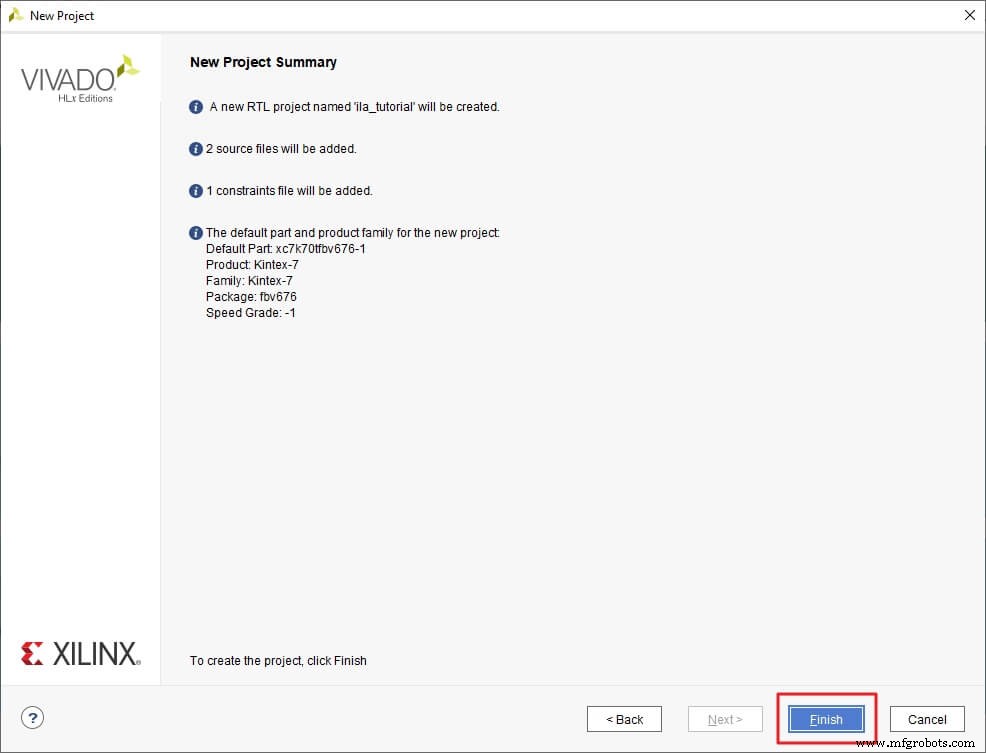

Dies ist der letzte Bildschirm des Assistenten für neue Projekte. Klicken Sie auf Fertig stellen um Ihr Projekt zu öffnen.

Die Erklärung des Designbeispiels

Wir werden für dieses Tutorial ein einfaches Kettenbeispiel mit zwei Zählern verwenden.

Die counter.vhdl enthält den RTL-Code für einen trivialen 4-Bit-Zähler, der bei Aktivierung von 0 bis 15 zählt. Es bestätigt den 1-Bit-Ausgang, wenn der Zählwert zwischen 12 und 15 liegt. Für alle anderen Werte bleibt der Ausgang low ‘0’ .

Hier ist die Entitätsschnittstelle für das Zählermodul.

----------------------------------------------------------------------------

-- ENTITY DECLARATION.

----------------------------------------------------------------------------

ENTITY counter IS

PORT(clk : IN STD_LOGIC; -- Main clock

reset : IN STD_LOGIC; -- reset, active_high

enable : IN STD_LOGIC; -- enable the next counter

trigger : OUT STD_LOGIC -- trigger the next counter

);

END ENTITY;

Das Zählerdesign hat zwei interne Signale:count und trigger_o .

– Zählung wird verwendet, um die Zählfunktion zu implementieren.

– und trigger_o ist ein Zwischensignal zum Anschluss des Ausgangsports Trigger .

Machen Sie sich keine Sorgen um ATTRIBUTE , wird später erklärt.

----------------------------------------------------------------------------

-- ARCHITECTURE DECLARATION.

----------------------------------------------------------------------------

ARCHITECTURE rtl OF counter IS

-- INTERNAL SIGNALS DECLARATION --

SIGNAL count : UNSIGNED(3 DOWNTO 0) := (OTHERS => '0');

SIGNAL trigger_o : STD_LOGIC := '0';

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

In der folgenden Auflistung sehen wir die Implementierung für den Zähler. Die seq_proc Der Prozess wird auf der steigenden Flanke des Eingangsports clk ausgelöst und befindet sich im Reset-Modus, wenn der Eingangsport zurückgesetzt wird ist hoch „1“.

Die Zählung Signal wird inkrementiert, wenn der Eingangsport aktiviert wird ist hoch „1“, und der trigger_o Signal wird hoch behauptet, wenn der Wert des Signals count ist liegt zwischen 12 und 15.

seq_proc: PROCESS (reset, clk)

BEGIN -- for seq_proc

IF (reset = '1') THEN

count <= (OTHERS => '0');

trigger_o <= '0';

ELSIF rising_edge(clk) THEN

IF (enable = '1') THEN

count <= count + 1;

IF (count > x"B" AND count <= x"F") THEN

trigger_o <= '1';

ELSE

trigger_o <= '0';

END IF;

END IF;

END IF;

END PROCESS;

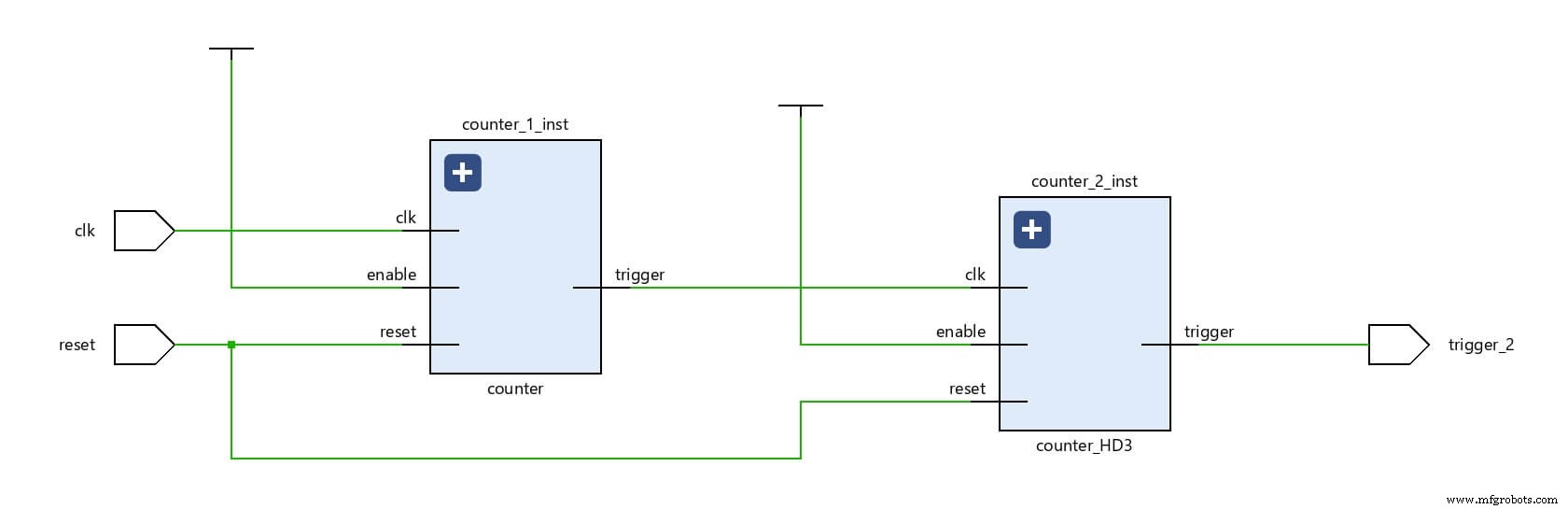

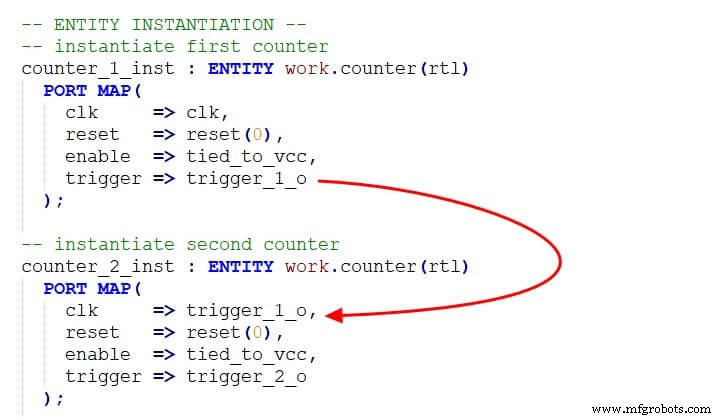

Die Datei counter_top.vhdl enthält zwei sequentiell verbundene Zeitpunkte des Zählers.

– Der counter_1_inst ist immer aktiviert und taktet den counter_2_inst . Das heißt, der Trigger des Ausgangsports von counter_1_inst ist mit dem Eingangsport clk verbunden von counter_2_inst .

– Das resultierende Verhalten ist dieses counter_1_inst aktiviert counter_2_inst nur 4 von 16 Taktzyklen. Also counter_2_inst wird seinen Zähler alle 16 Zählungen viermal erhöhen.

Erstellen des VIO-Kerns für RESET

Nachdem Sie nun das Designbeispiel verstanden haben, erstellen wir ein VIO, um den Eingangsport zurücksetzen zu steuern . Dadurch können wir das Zurücksetzen von Vivado IDE manipulieren (umschalten), sodass wir manuell steuern können, wann die Zähler gestartet/gestoppt werden sollen.

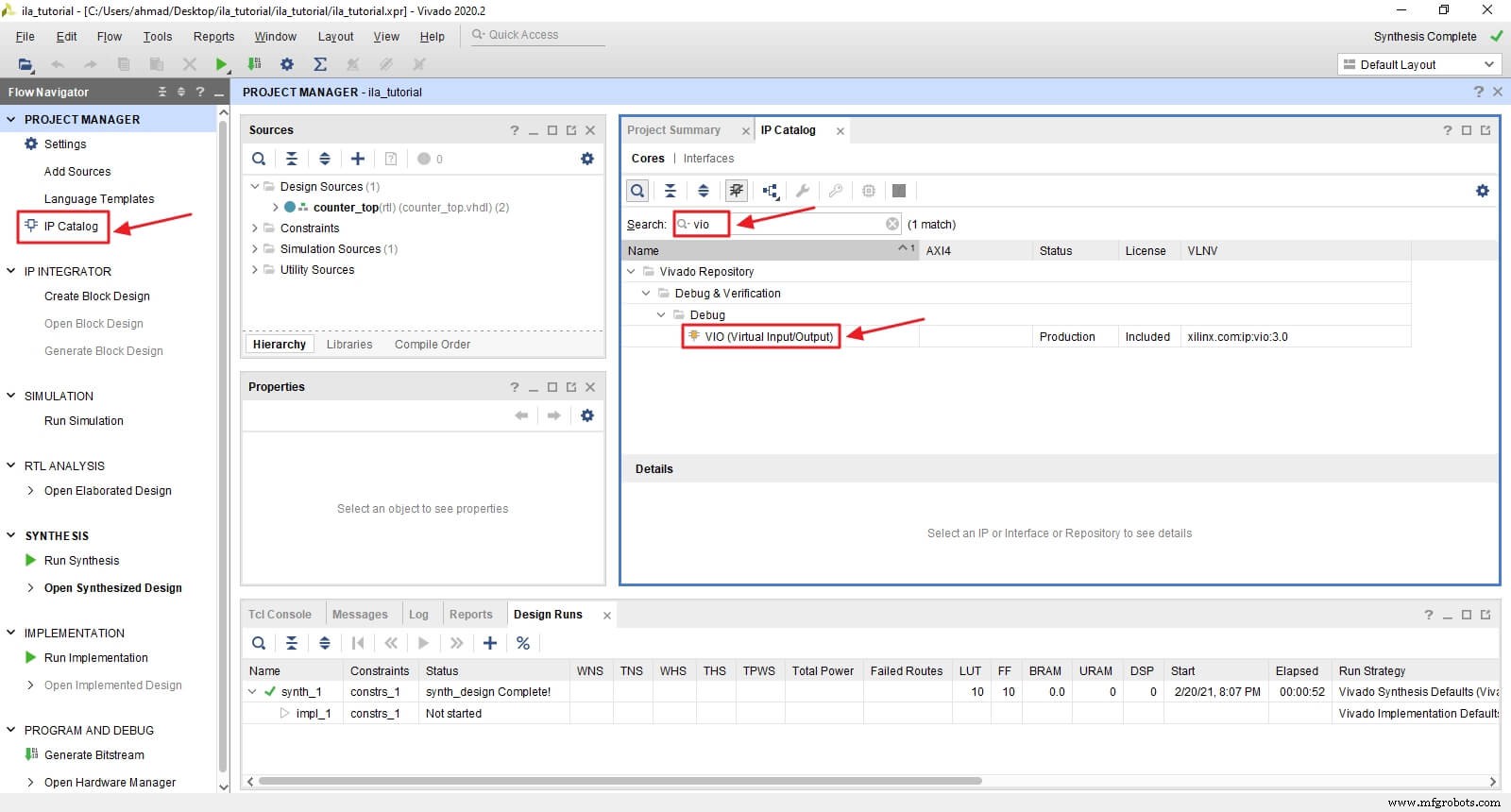

Klicken Sie auf IP-Katalog , und suchen Sie dann nach VIO , und doppelklicken Sie dann auf VIO (Virtual Input/Output) .

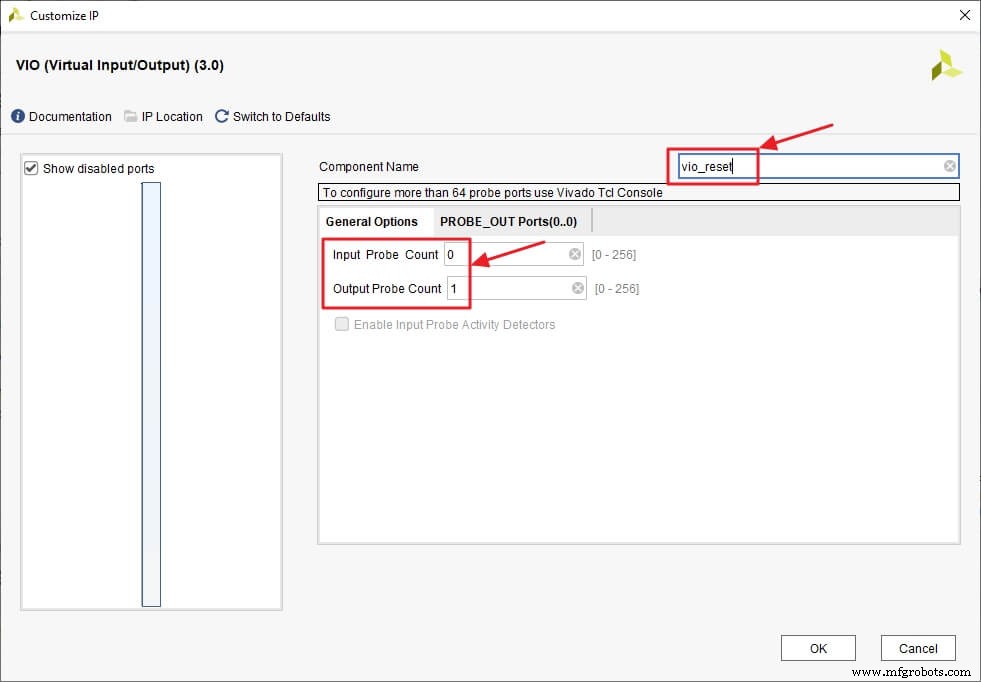

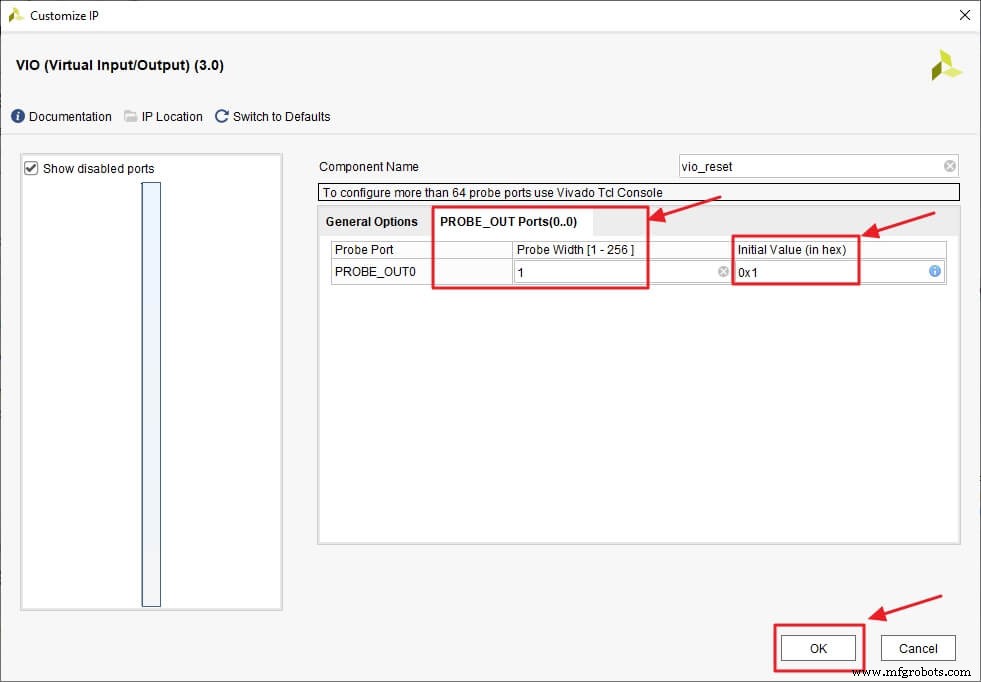

Zuerst ändern wir den Namen in vio_reset .

Zweitens benötigen wir nur einen Ausgangsport für das Zurücksetzen, also geben wir 0 in das Feld für die Anzahl der Eingabeproben ein und wir geben 1 in das Feld für die Anzahl der Ausgabeproben ein .

Klicken Sie auf PROBE_OUT Registerkarte „Port“. Da das Zurücksetzen ein 1-Bit-Signal ist, geben wir 1 in das Feld probe_width ein und wir geben auch 0x1 in das Anfangswertfeld ein es beginnt also mit der hohen „1“. Klicken Sie dann auf OK und Generieren . Vivado beginnt nun mit der Synthese des VIO.

Nachdem Vivado die Synthetisierung des VIO abgeschlossen hat, müssen wir es zu unserem Design hinzufügen, indem wir eine Komponente dafür deklarieren und es in counter_top.vhdl instanziieren Datei wie unten.

Fügen Sie zuerst eine Komponentendeklaration für vio_reset hinzu im Komponentendeklarationsabschnitt in counter_top.vhdl Datei.

-- Declare vio_reset

COMPONENT vio_reset

PORT(

clk : IN STD_LOGIC;

probe_out0 : OUT STD_LOGIC_VECTOR(0 DOWNTO 0)

);

END COMPONENT;

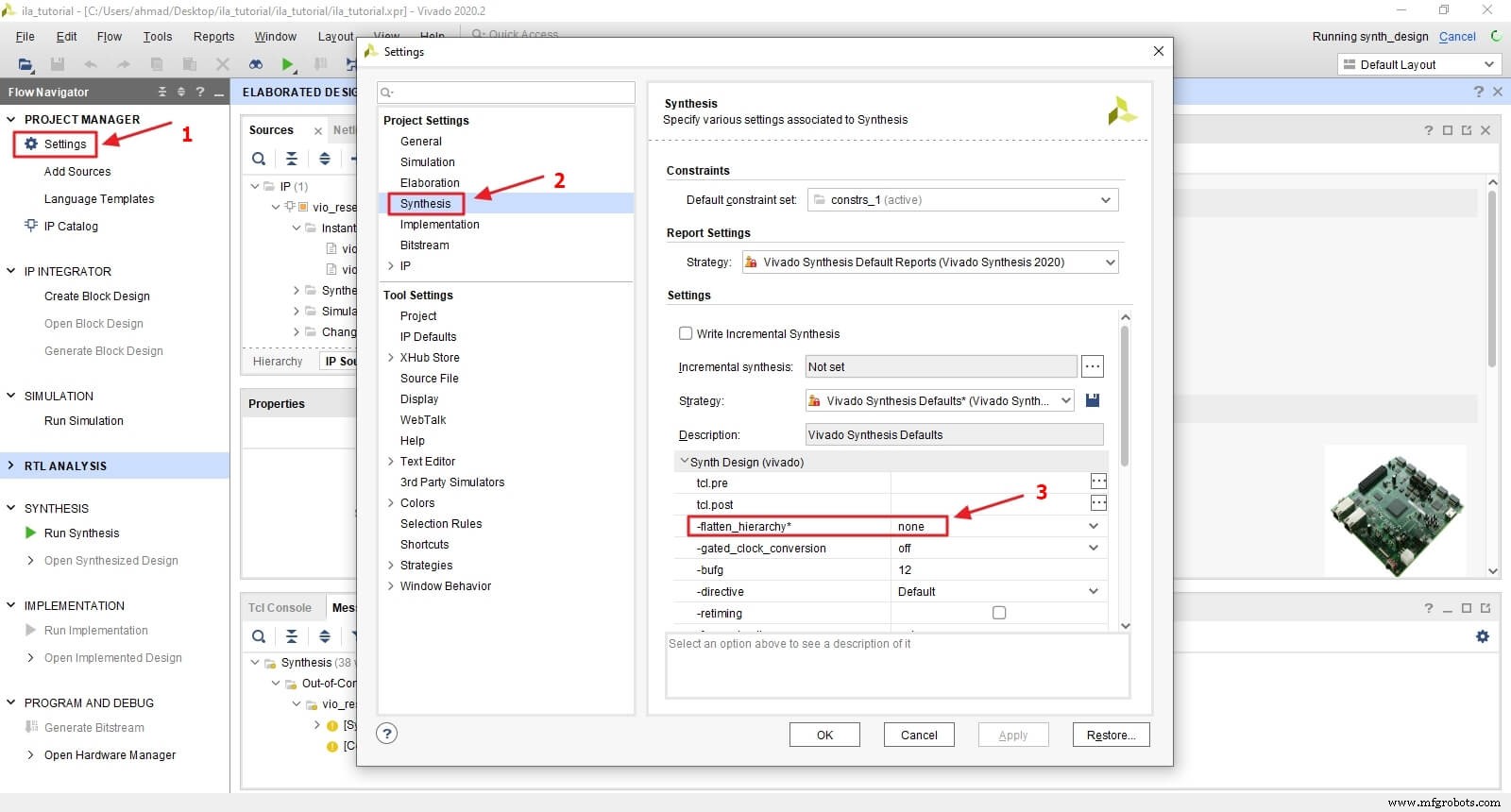

Jetzt ist das VIO fertig und wir sind bereit, das Design zu synthetisieren. Aber vorher müssen wir die Syntheseeinstellung flatten_hierarchy ändern auf Keine .

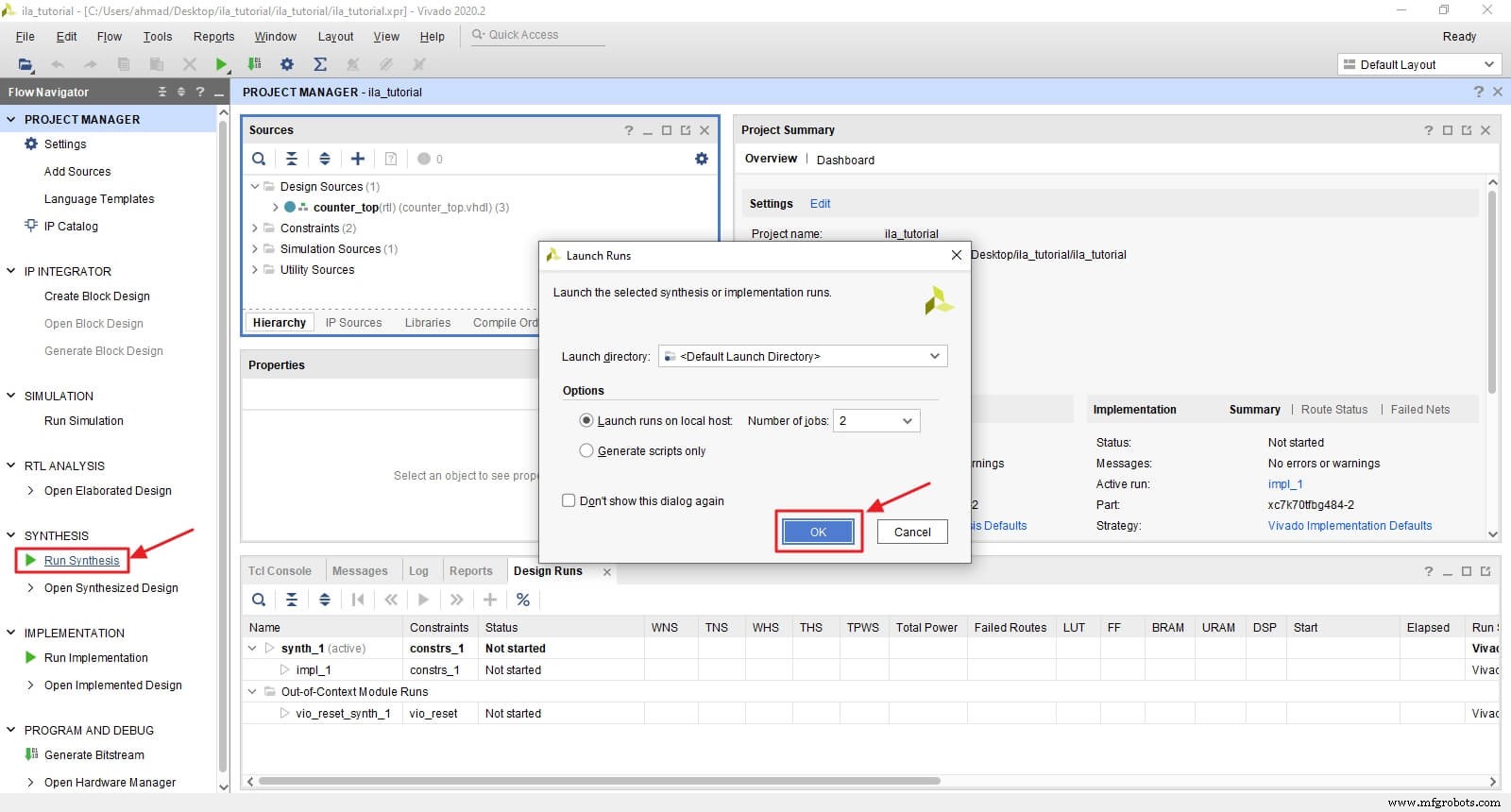

Klicken Sie auf Synthese ausführen und dann auf OK .

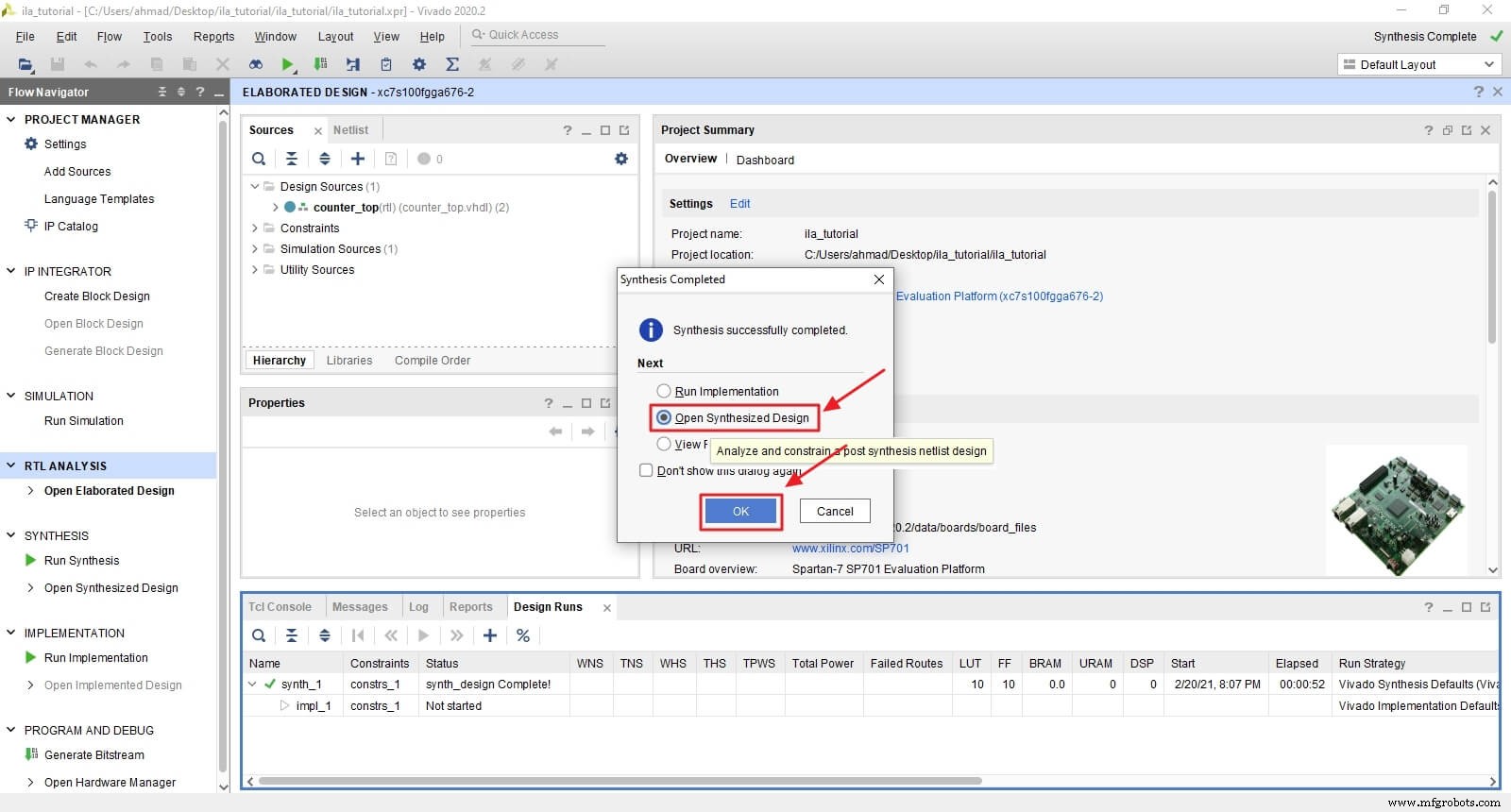

Wenn Vivado die Synthese beendet hat, klicken Sie auf Synthesiertes Design öffnen .

Ändern Sie das Layout in debug indem Sie auf Layout klicken und dann Debuggen .

Debugging-Probe-Flow einfügen

Unser synthetisiertes Design enthält jetzt das vio_reset Beispiel, und es ist an der Zeit, die Signale zu spezifizieren, die wir untersuchen möchten. Dafür gibt es drei Möglichkeiten:

- Einfügen aus VHDL-Datei

- Einfügung aus der Netzliste

- Einfügen aus xdc/tcl-Datei

Wir werden die ersten beiden Methoden verwenden und die dritte für ein späteres Tutorial aufheben.

Einfügen aus VHDL-Datei

Diese Methode ist die einfachste und schnellste Art, eine Sonde einzuführen, insbesondere wenn es sich um einen zusammengesetzten Typ (Array oder Aufzeichnung) handelt. Aber es erfordert das Hinzufügen von Code zu den Designdateien, VHDL-Code, der im echten Produkt redundant ist.

Wir können eine Sonde in die VHDL-Entwurfsdatei einfügen durch:

- Deklaration eines speziellen Attributs namens MARK_DEBUG

- Hängen Sie das Signal an, das wir mit diesem Attribut untersuchen möchten

- Und aktivieren Sie es, indem Sie ihm wie folgt den Wert „true“ geben:

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

Hinweis: Wir müssen das Attribut nur einmal in jeder VHDL-Designdatei deklarieren, sodass wir es an mehrere Signale anhängen können.

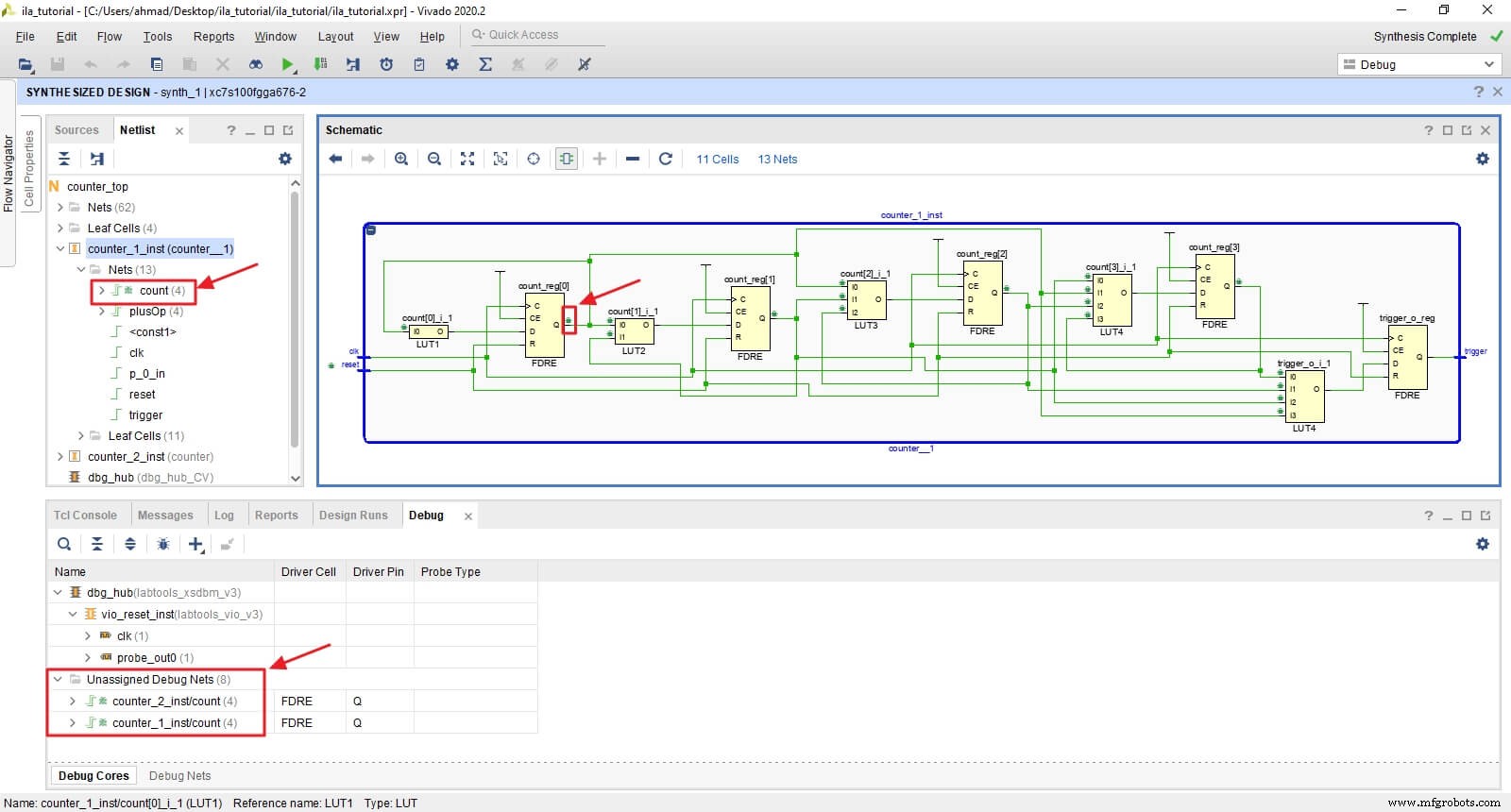

Wir können aus dem synthetisierten Design erkennen, dass das Signal count in beiden counter_1_inst und counter_2_inst sind unter Nicht zugewiesene Debug-Netze aufgeführt und in der Netzliste mit einem Fehlersymbol gekennzeichnet und das Schema .

Einfügung aus der Netzliste

Diese Einfügungsmethode ist ebenfalls einfach, erfordert jedoch, dass Sie zuerst das Design synthetisieren und dann manuell auf jedes Signal klicken, um es zum Debuggen zu markieren. Es könnte anstrengend sein, wenn das Design groß ist und Sie viele Signale überwachen möchten.

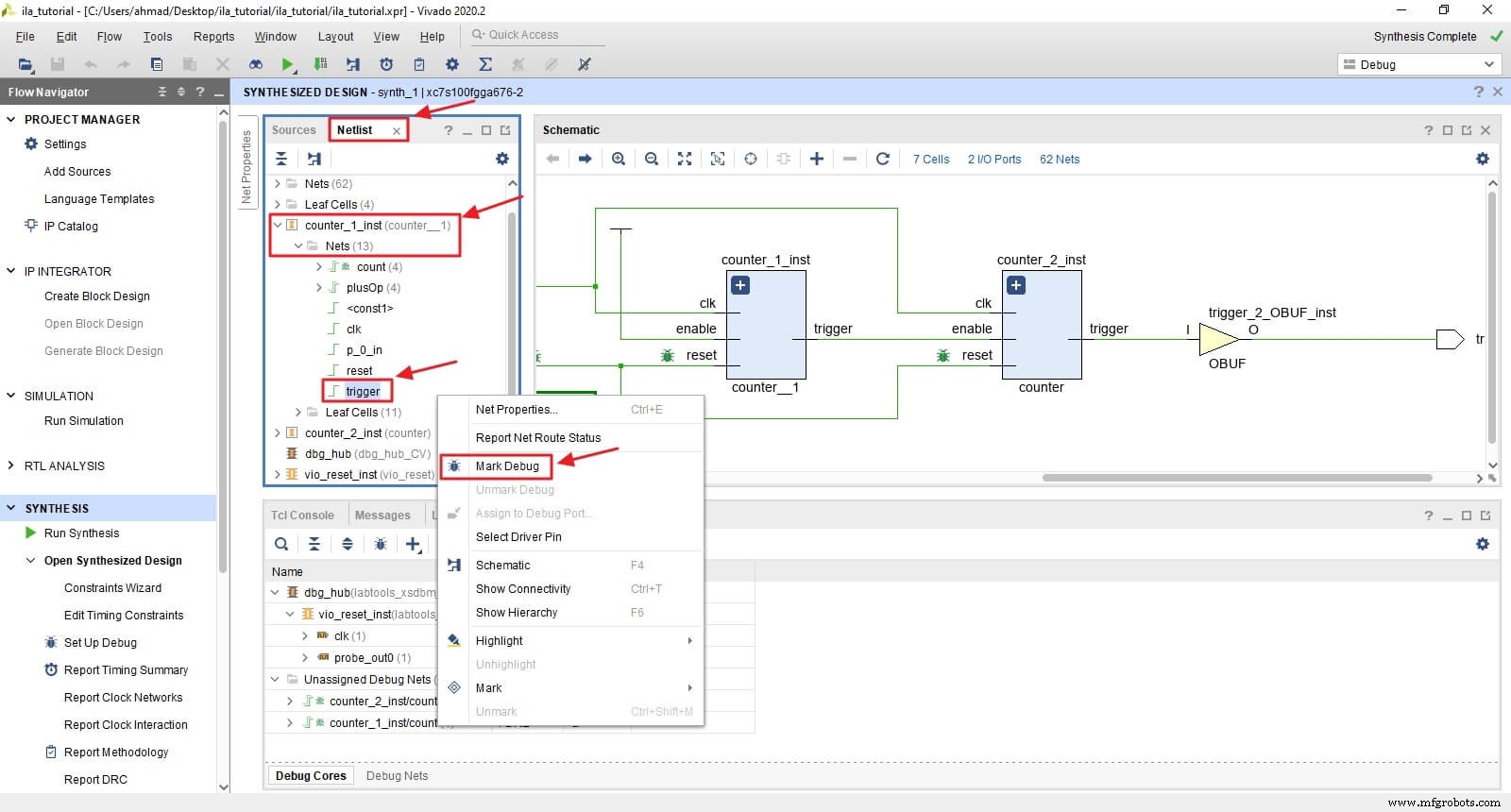

Wir prüfen den Trigger des Ausgangsports in beiden Zählern über die Netzliste . Wir können dies entweder vom Netzlistenfenster aus tun oder das Schema indem Sie das Signalnetz suchen und dann mit der rechten Maustaste klicken darauf und wählen Sie Mark Debug .

Suchen Sie im Netzlistenfenster nach Trigger unter counter_1_inst → Netze → Auslöser . Klicken Sie dann mit der rechten Maustaste darauf und wählen Sie Debug markieren .

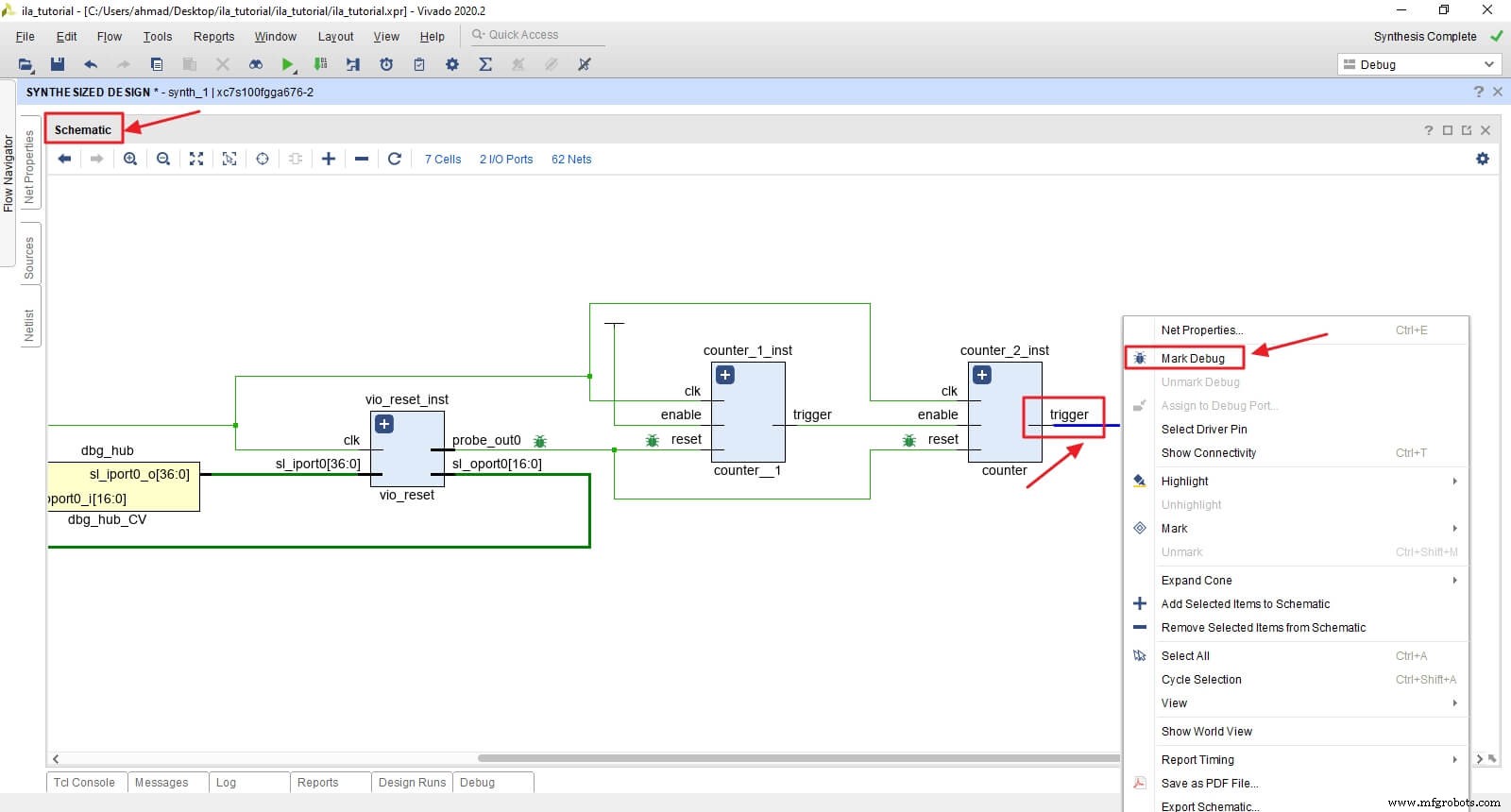

Suchen Sie im Schematic-Fenster nach Trigger Ausgabe von counter_2_inst . Klicken Sie dann mit der rechten Maustaste darauf und wählen Sie Debug markieren .

Wir können sehen, dass sie jetzt unter Nicht zugewiesene Debug-Netze aufgelistet sind .

Erstellen des ILA-Debug-Kerns

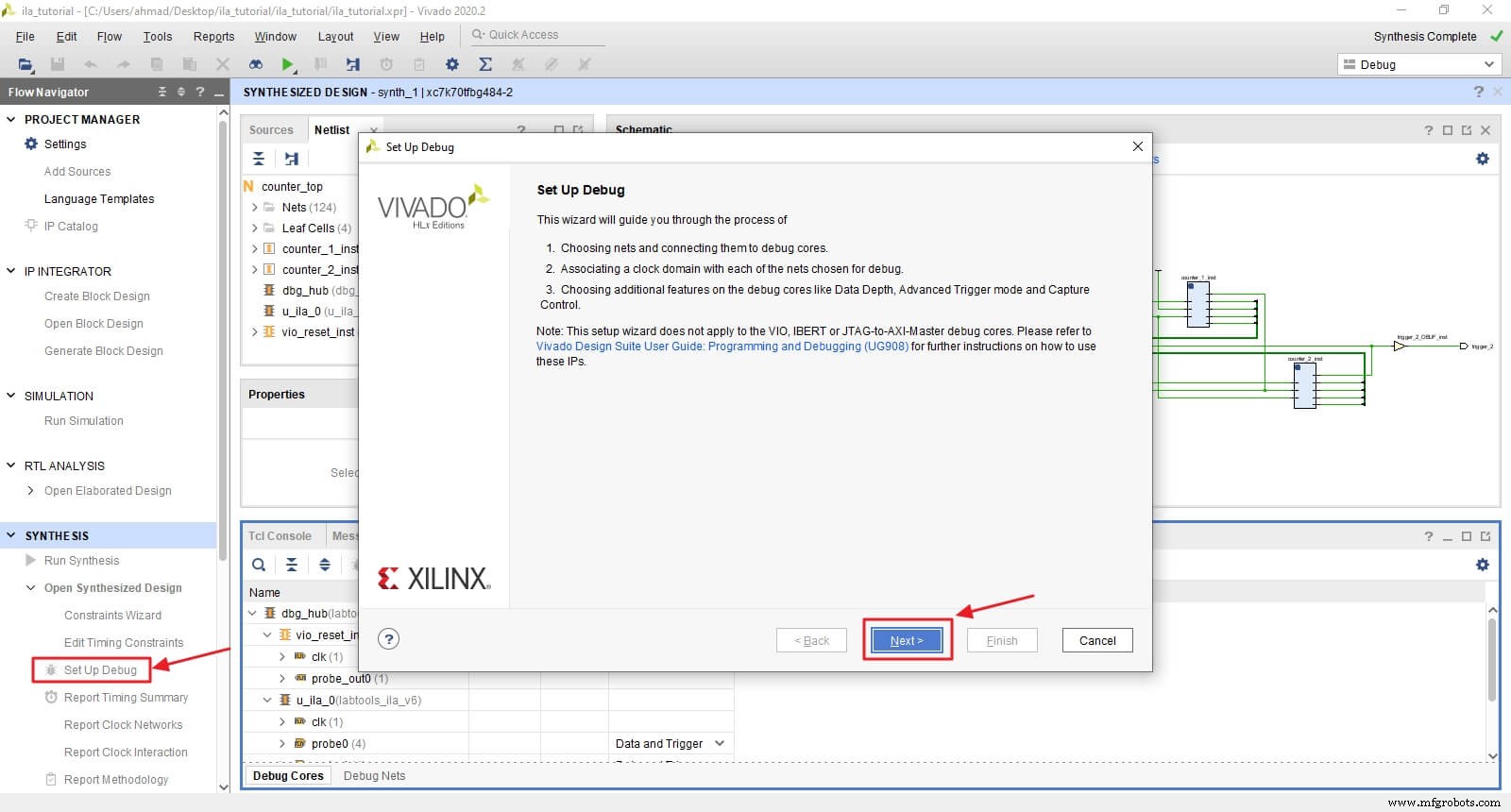

Jetzt ist es an der Zeit, den ILA-Debug-Core zu erstellen. Wir müssen für jedes Signal, das wir analysieren möchten, eine Sonde erstellen. Am einfachsten ist es, den Vivado-Assistenten Debug einrichten zu nutzen .

Klicken Sie auf Debug einrichten und klicken Sie dann auf Weiter .

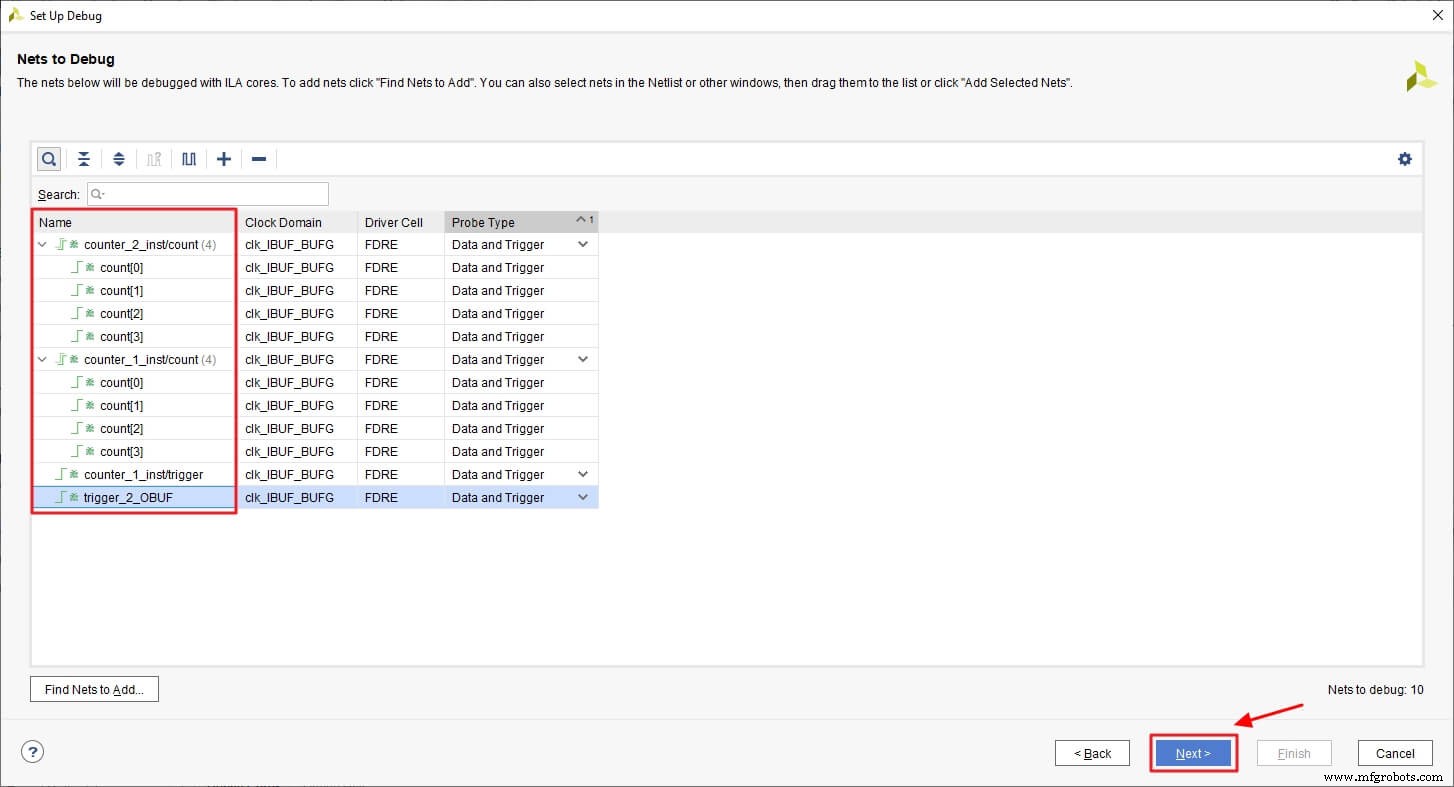

Vivado listet alle Debug-Signale auf und erfasst die Taktdomäne automatisch für Sie. Hier sehen wir, dass unsere vier Signale aufgelistet sind. Sie können die Signale entfernen, die Sie nicht interessieren, oder zusätzliche Signale hinzufügen, aber wir werden alle verwenden.

Hinweis: wir müssen nicht alle Signale verwenden, die wir als Debug markiert haben.

Klicken Sie auf Weiter .

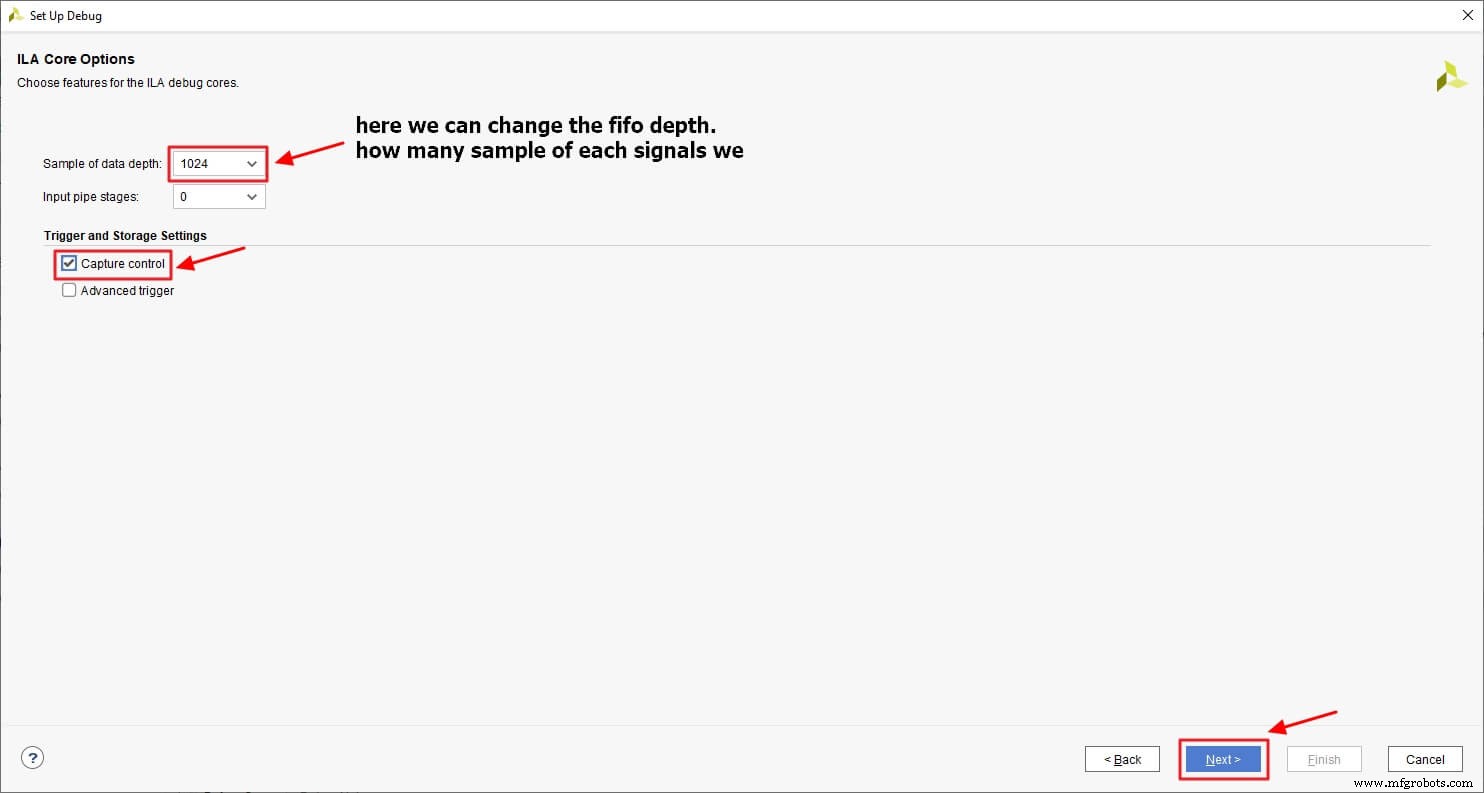

Jetzt konfigurieren wir den ILA, indem wir die FIFO-Tiefe auswählen und aktivieren Sie Aufnahmesteuerung . Wir können den FIFO bei 1024 belassen, da er für unser Beispiel ausreichend tief ist.

Klicken Sie auf Weiter .

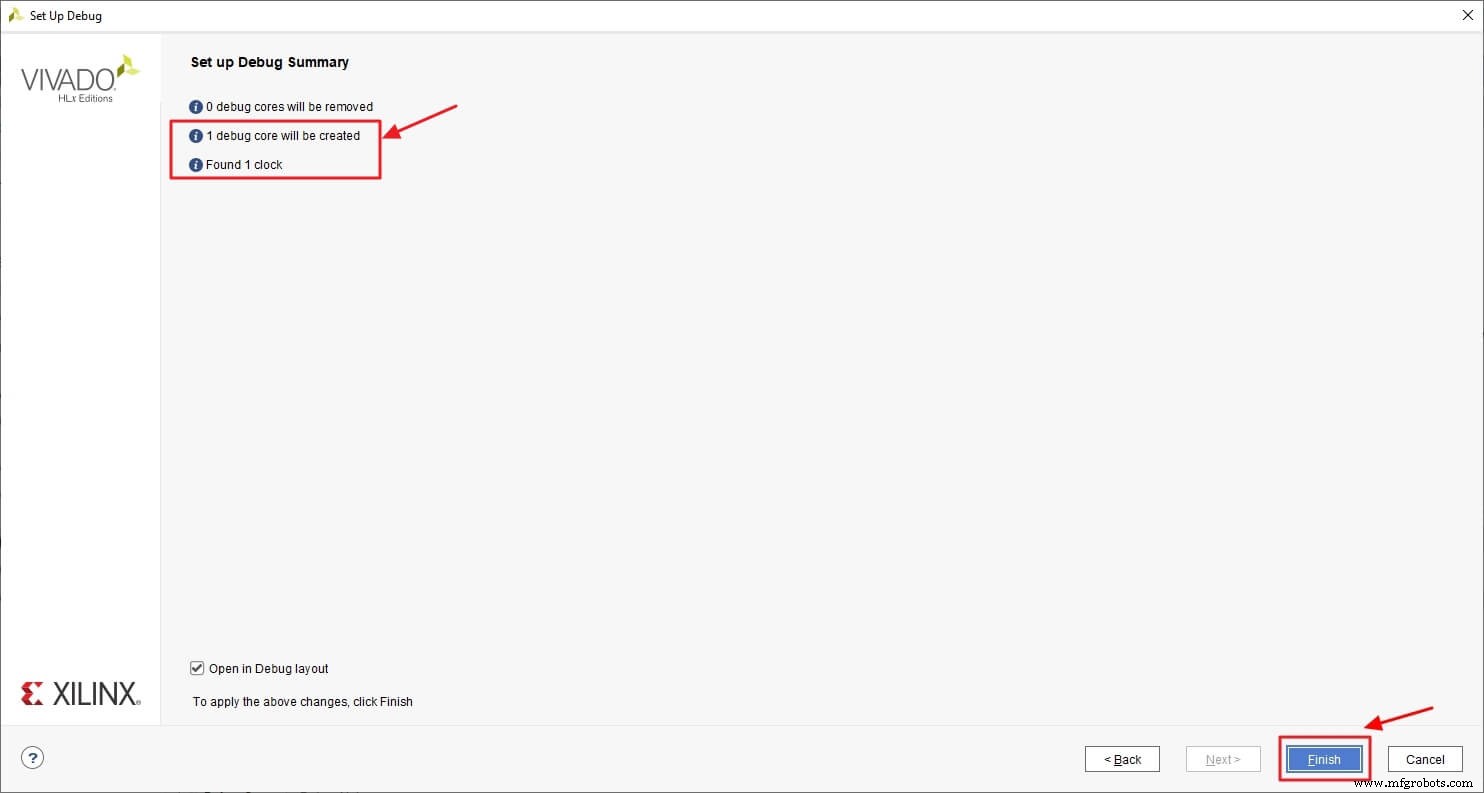

Jetzt sehen wir, dass Vivado eine Uhr gefunden hat und einen Debug-Core erstellen wird.

Klicken Sie auf Fertig stellen .

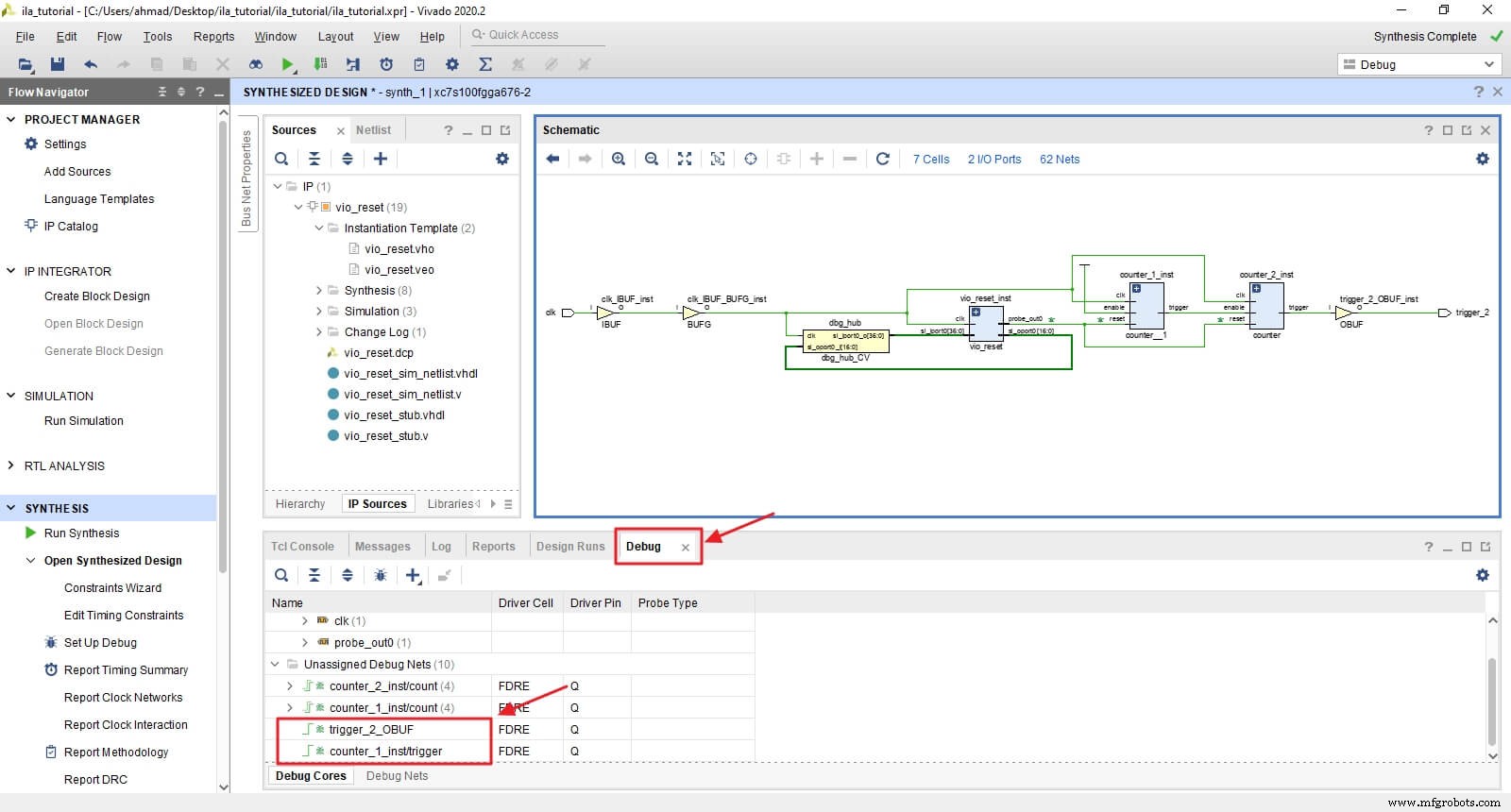

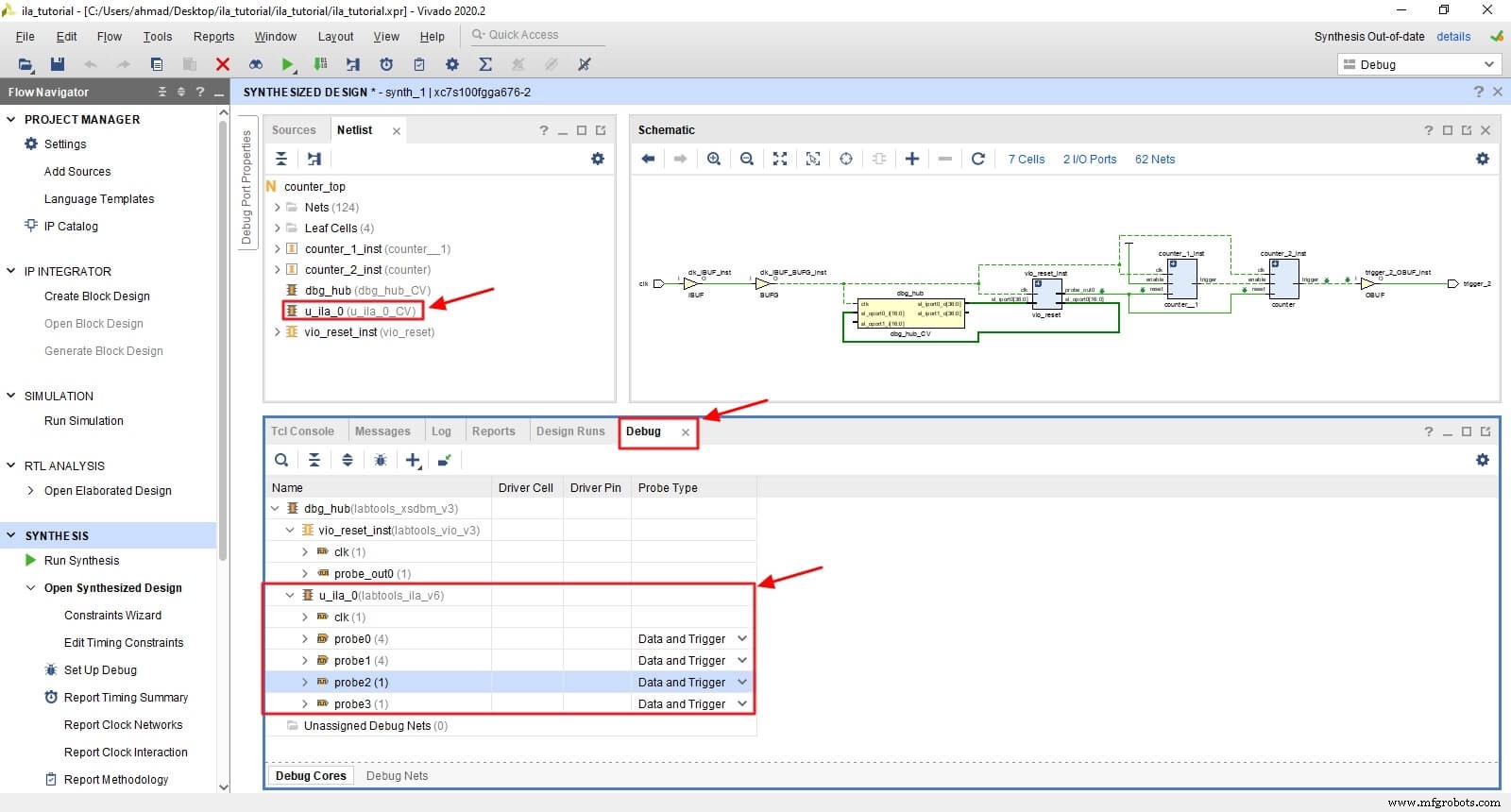

Wir können jetzt einen ILA-Debug-Core mit vier Sonden sehen, die dem Debug-Tab hinzugefügt wurden und das Netzlistenfenster .

WICHTIG: Es ist sehr wichtig, die Beschränkung in dieser Phase zu speichern, damit sie dem Design hinzugefügt werden kann. Andernfalls riskieren wir, unseren ILA-Kern zu verlieren.

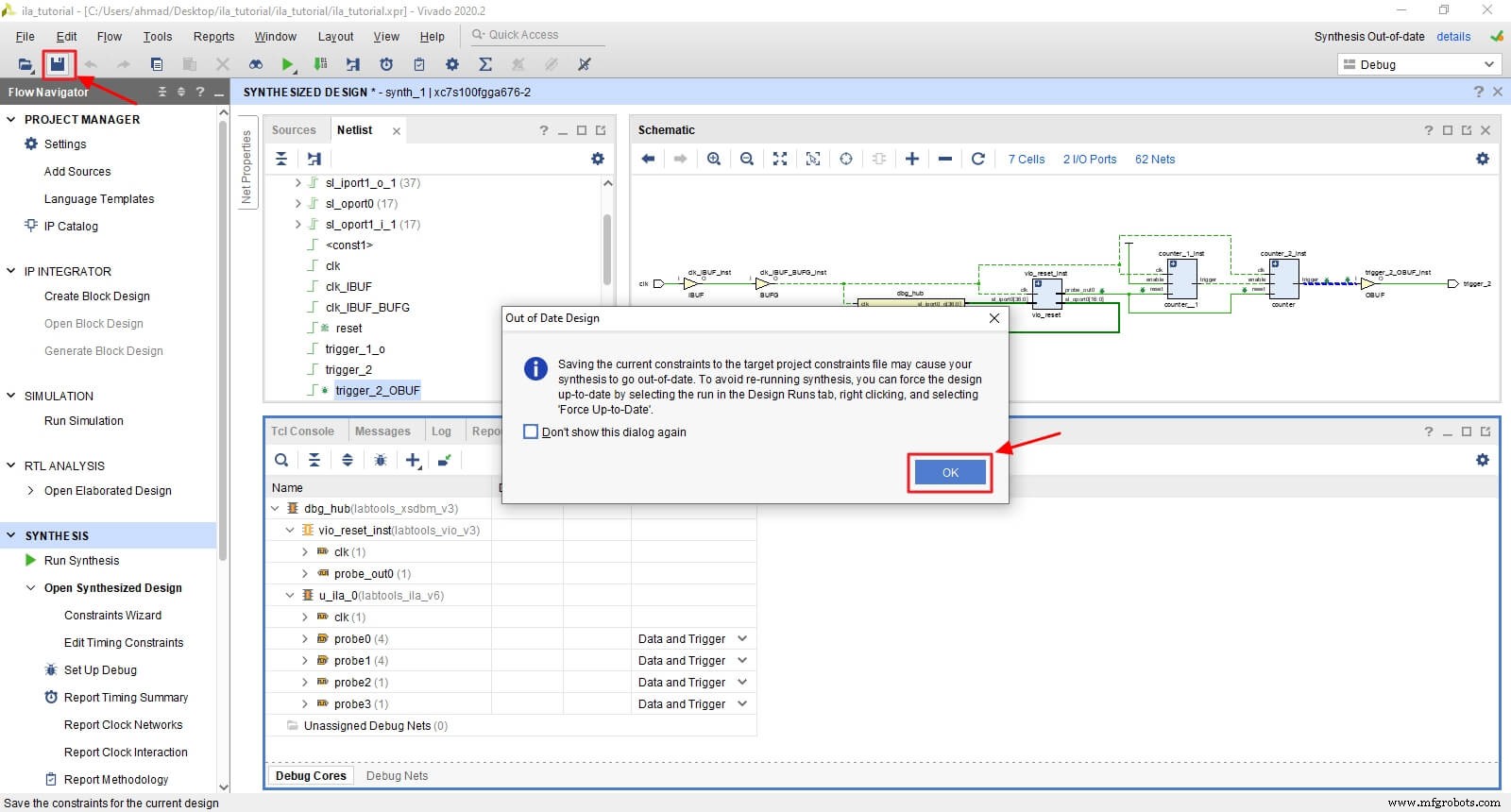

Klicken Sie auf Speichern Symbol oder drücken Sie Strg+S.

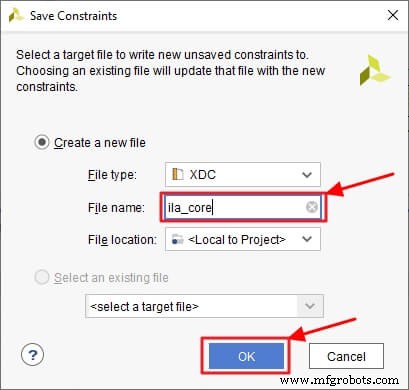

Benennen Sie die Datei ila_core und klicken Sie auf OK .

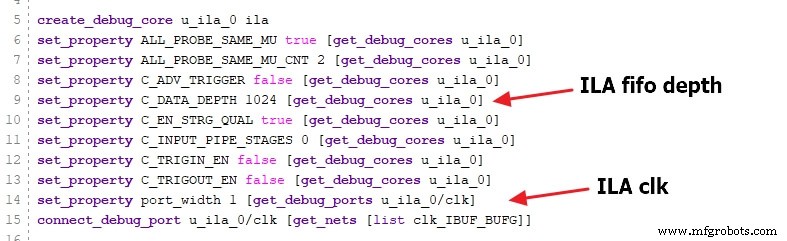

Die ila_core.xdc Datei wird der Einschränkung hinzugefügt und enthält den Code und die Einstellungen für die ILA.

Werfen wir einen Blick auf den Dateiinhalt. Sie können die Datei öffnen, indem Sie zum Quellfenster gehen → Constraint-Ordner erweitern → constr_1 erweitern .

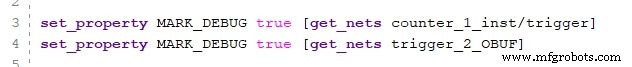

Zuerst sehen wir, dass die Datei den Signalen, die wir mit der Netzlisteneinfügung als debug markiert haben, ein debug-Attribut hinzufügt.

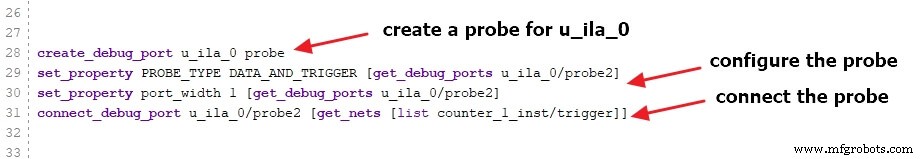

Als nächstes sehen wir die Erstellung und Konfiguration eines ILA-Kerns.

Als Nächstes sehen wir die Erstellung, Konfiguration und Verbindung für jede Probe.

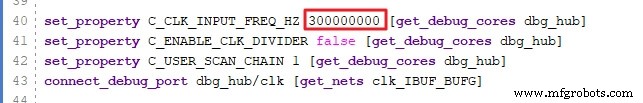

Als nächstes sehen wir die Erstellung eines Debug-Hubs (dbg_hub ).

Der Debug-Hub ist für die Kommunikation zwischen Vivado IDE und den Debug-Kernen (ILA und VIO) zuständig. Wir sehen, dass es eine Taktfrequenz definiert (Standard ist 300 MHz). Sie müssen diese Uhr an Ihre Taktfrequenz anpassen und die Datei speichern.

Hinweis: die mit ILA und Debug_hub verbundene Uhr muss eine freilaufende Uhr sein.

Nun ist der ILA fertig und gespeichert. Wir müssen die Synthese erneut ausführen, damit die ILA dem synthetisierten Design hinzugefügt werden kann.

Klicken Sie auf Synthese ausführen und dann auf OK .

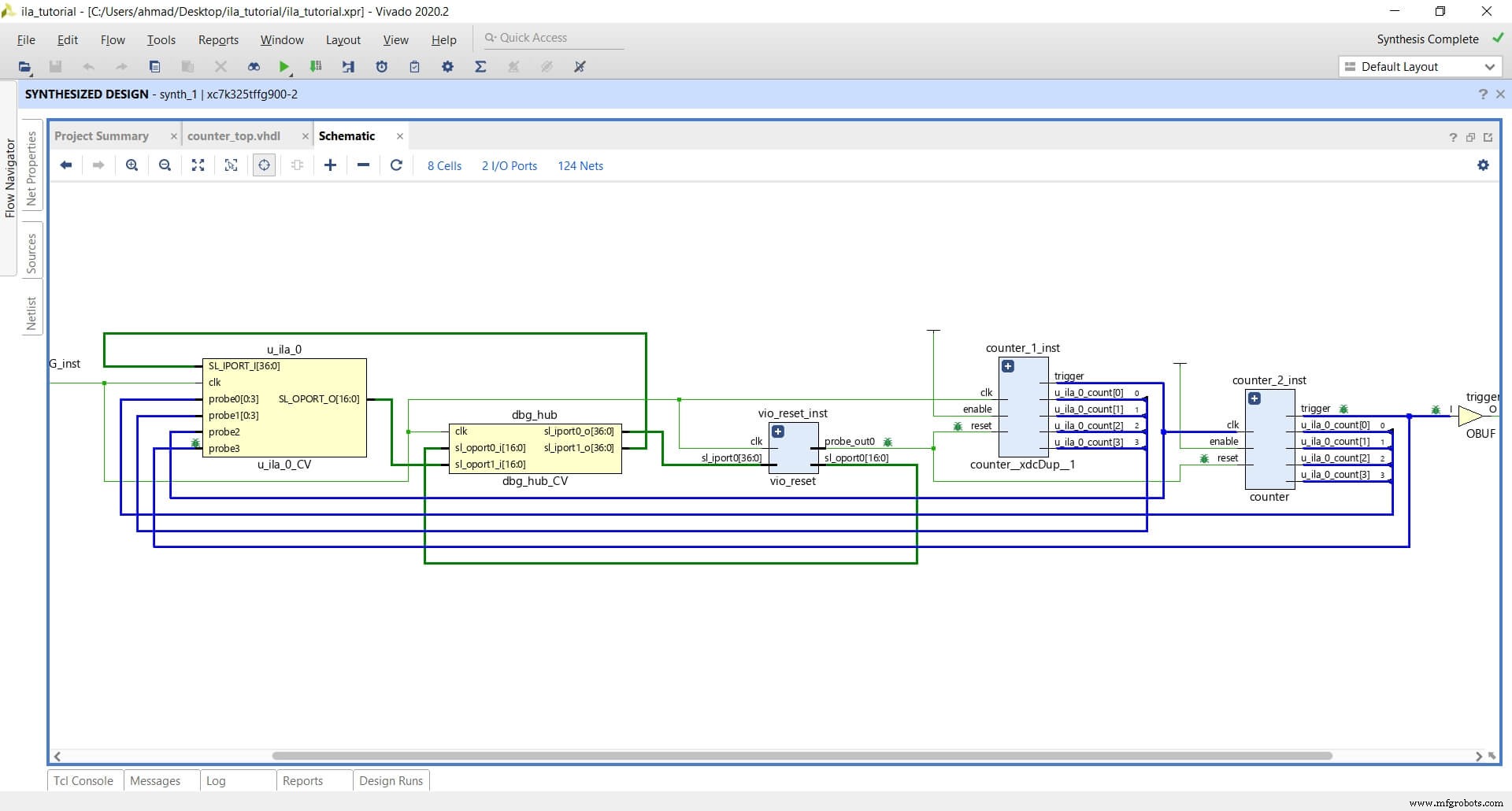

Wenn Vivado die Synthese beendet hat, klicken Sie auf Synthesiertes Design öffnen und dann auf Schema .

Wir können jetzt sehen, dass Vivado den ILA und den Debug_Hub zu unserem Design hinzugefügt und die Debug-Signale mit den ILA-Sonden verbunden hat.

Jetzt sind wir bereit, unser Design zu implementieren und den Bitstream zu generieren, damit wir unser Design testen können.

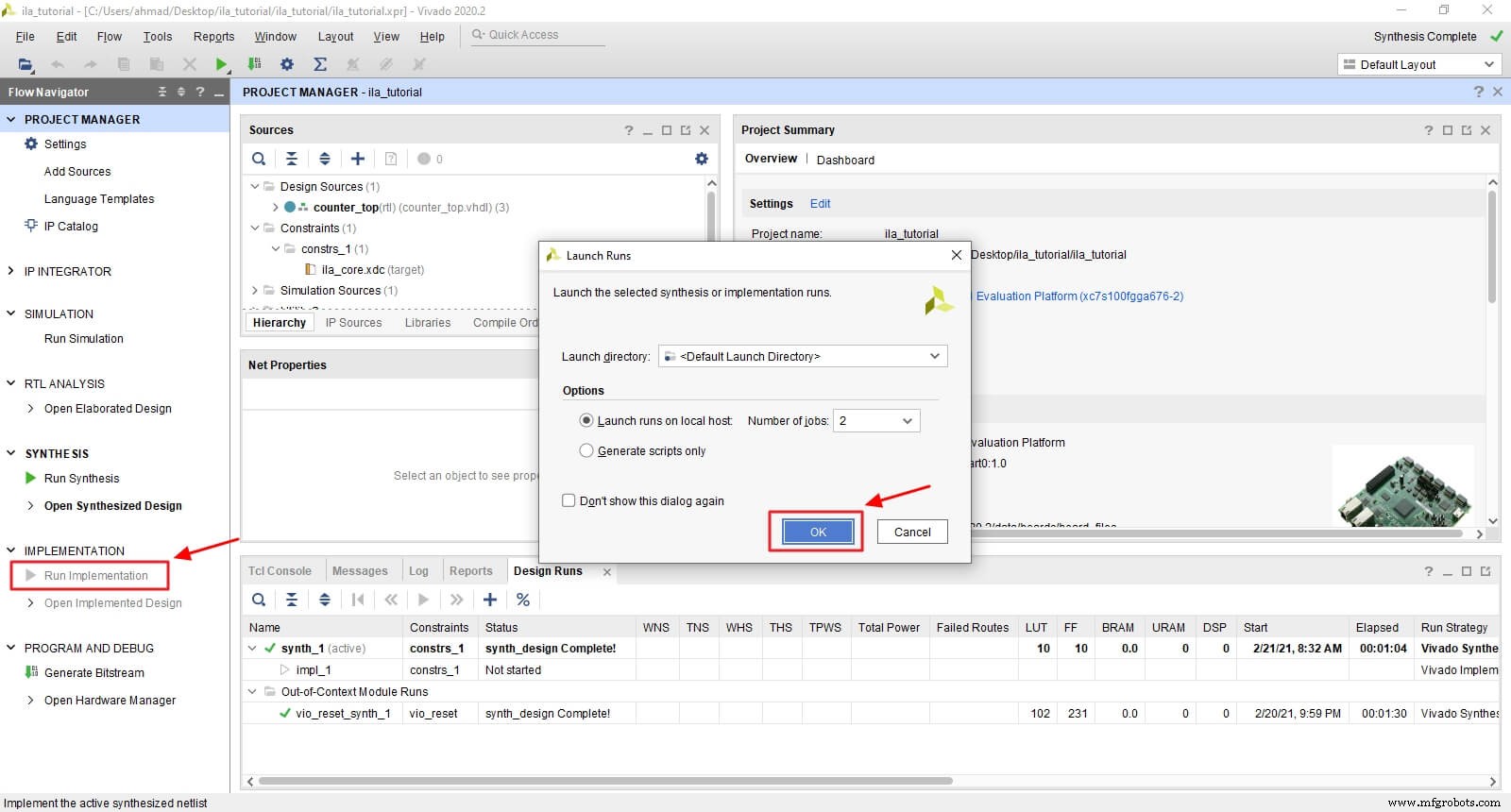

Klicken Sie auf Implementierung ausführen und dann auf OK .

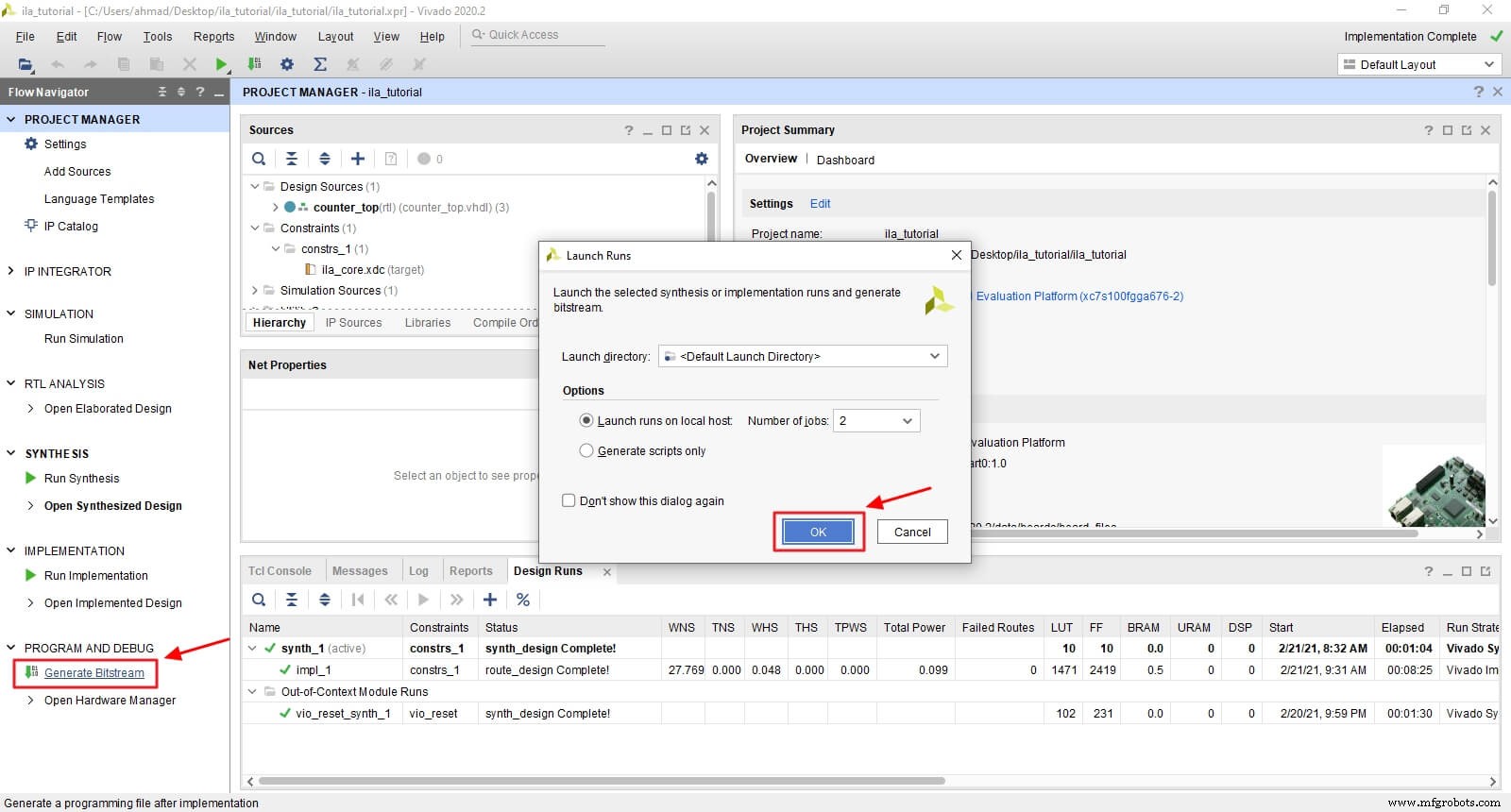

Nachdem Vivado die Implementierung abgeschlossen hat, klicken Sie auf Generate Bitstream und dann auf OK .

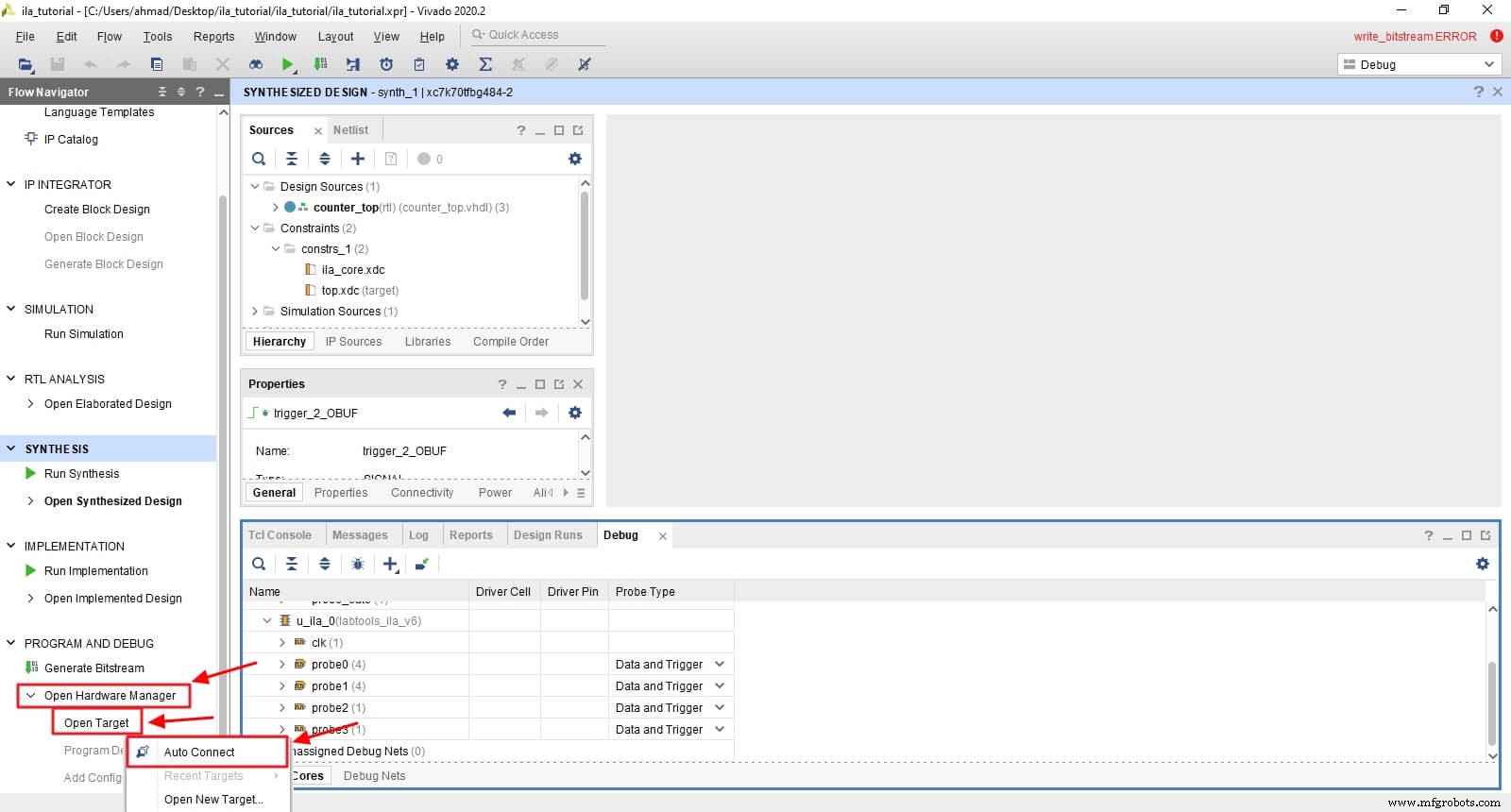

Nachdem Vivado den Bitstream generiert hat, klicken Sie auf Hardware-Manager öffnen und dann auf Open Target, und schließlich auf Automatisch verbinden .

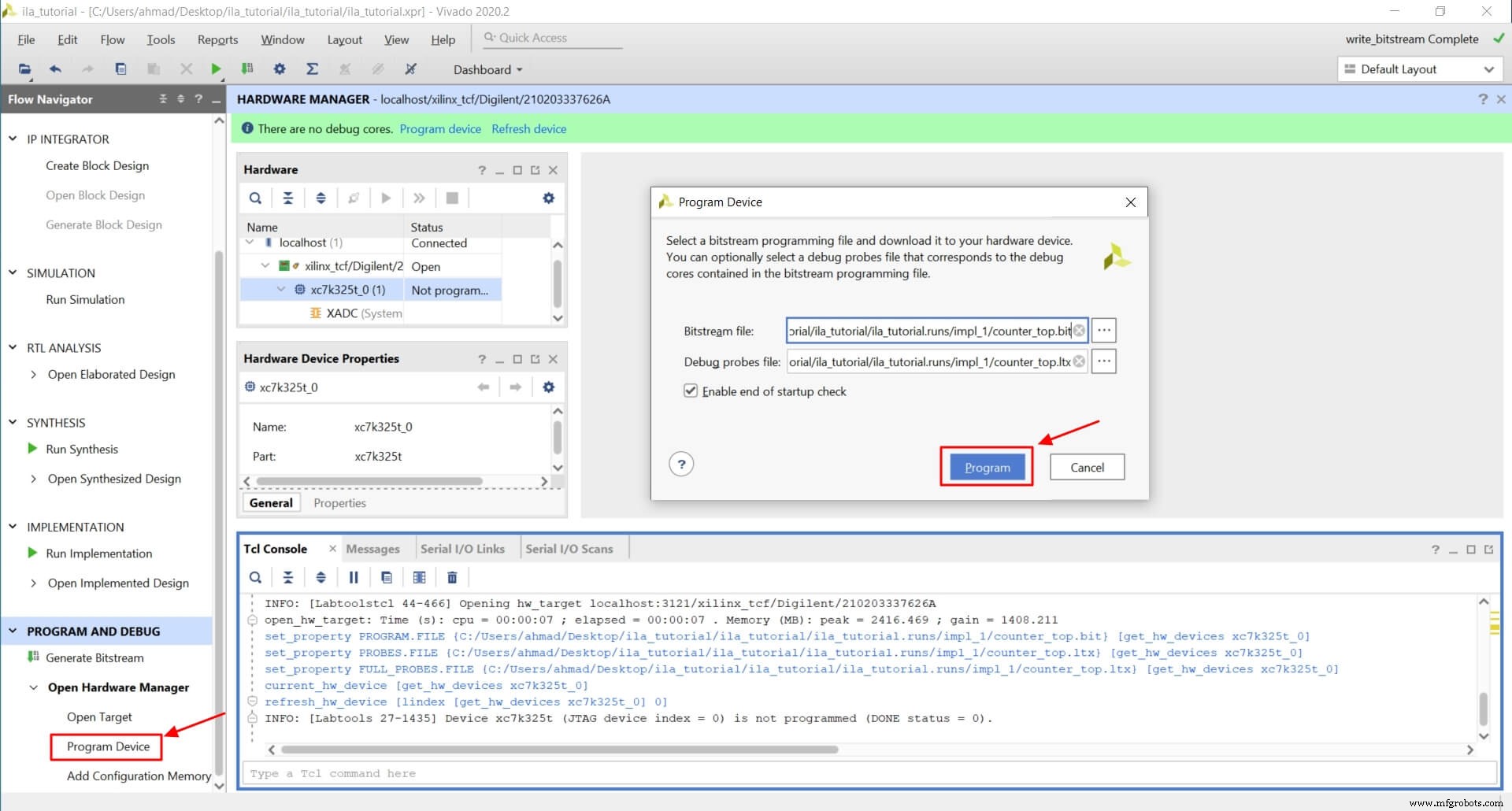

Als nächstes müssen wir das FPGA mit der Bitdatei (*.bit) und der Debug-Probe-Datei (*.ltx) programmieren. Vivado findet sie automatisch für Sie.

Klicken Sie auf Gerät programmieren und dann auf Programm .

Konfigurieren der ILA-Trigger

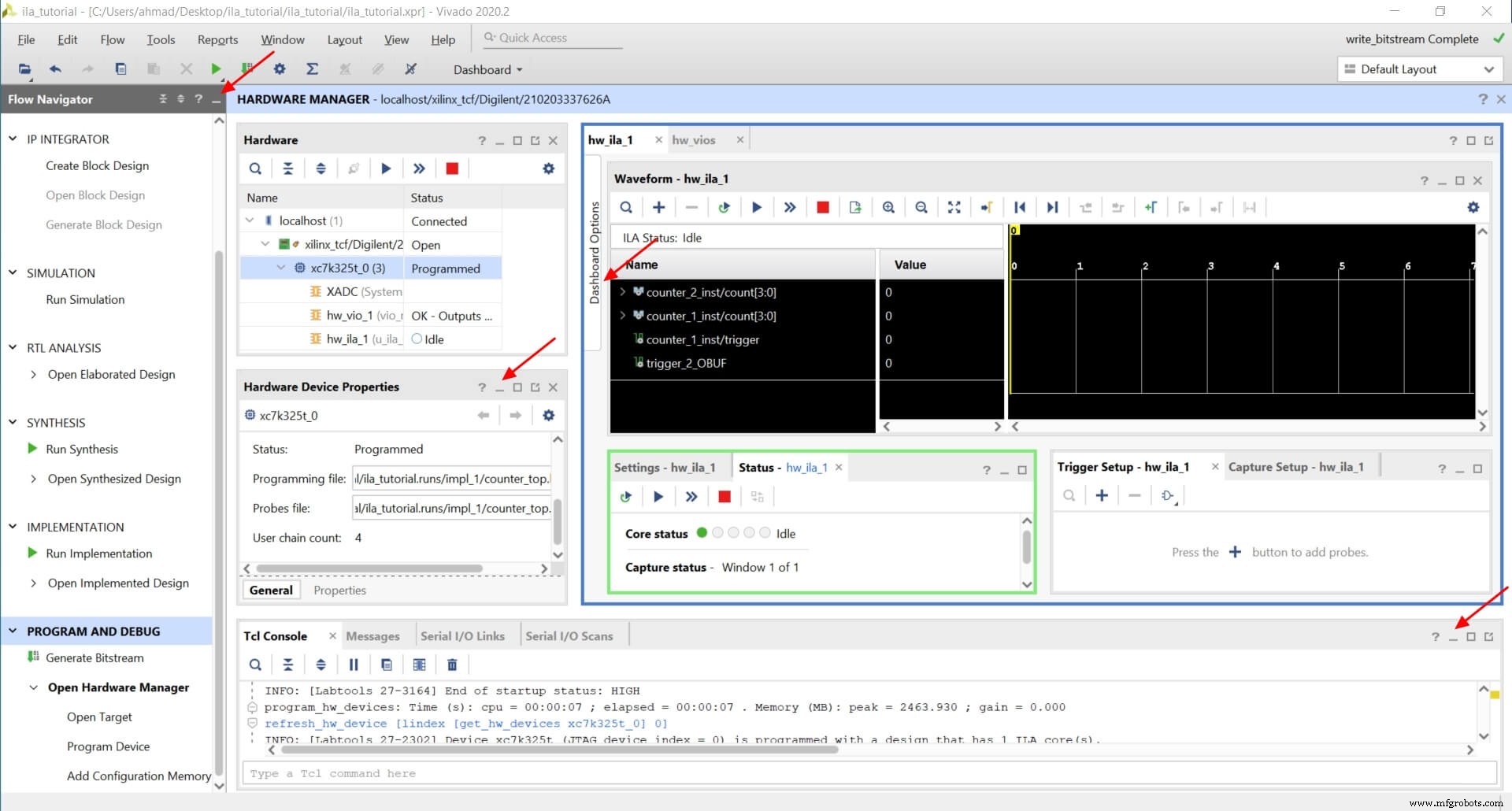

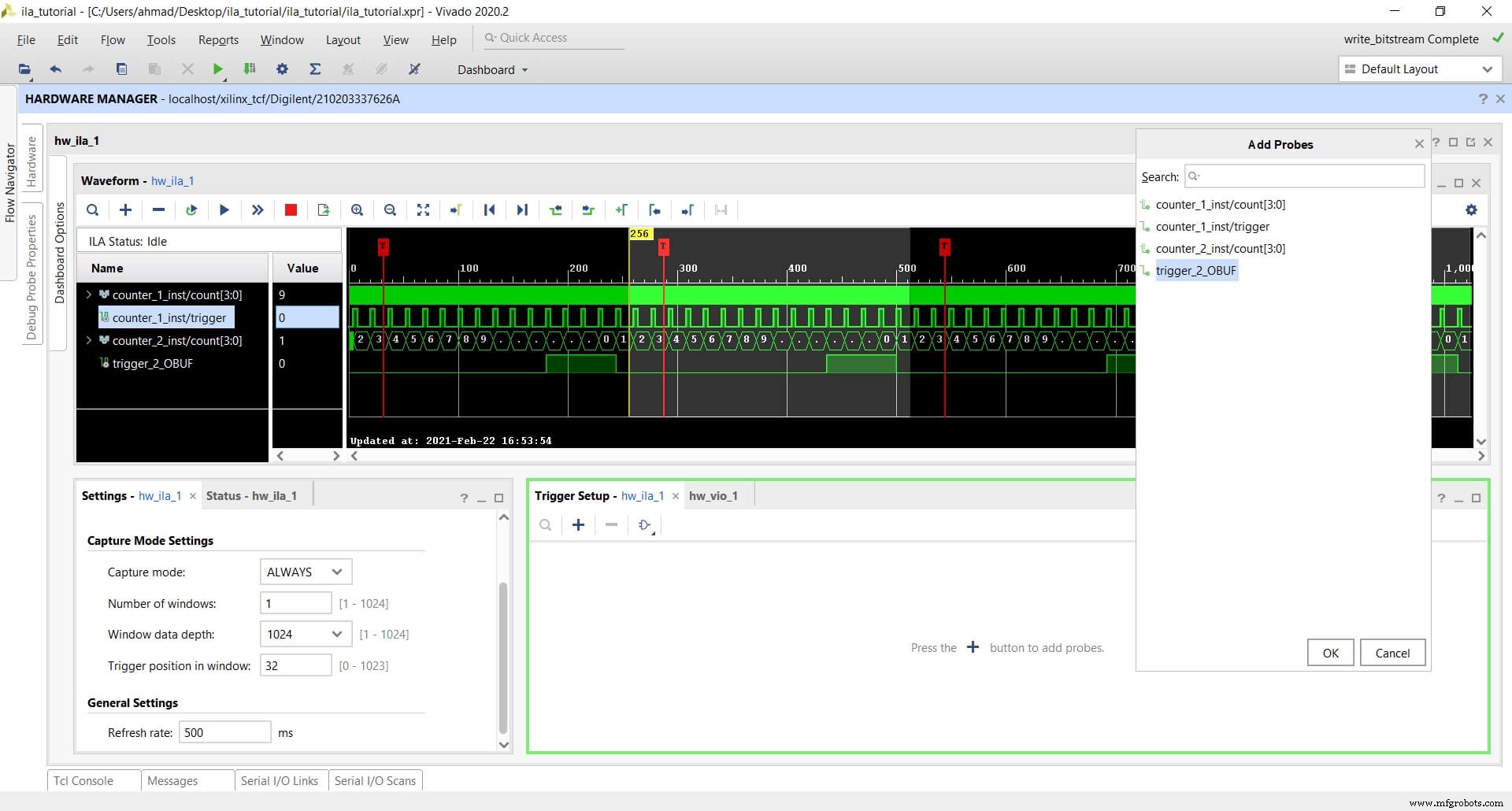

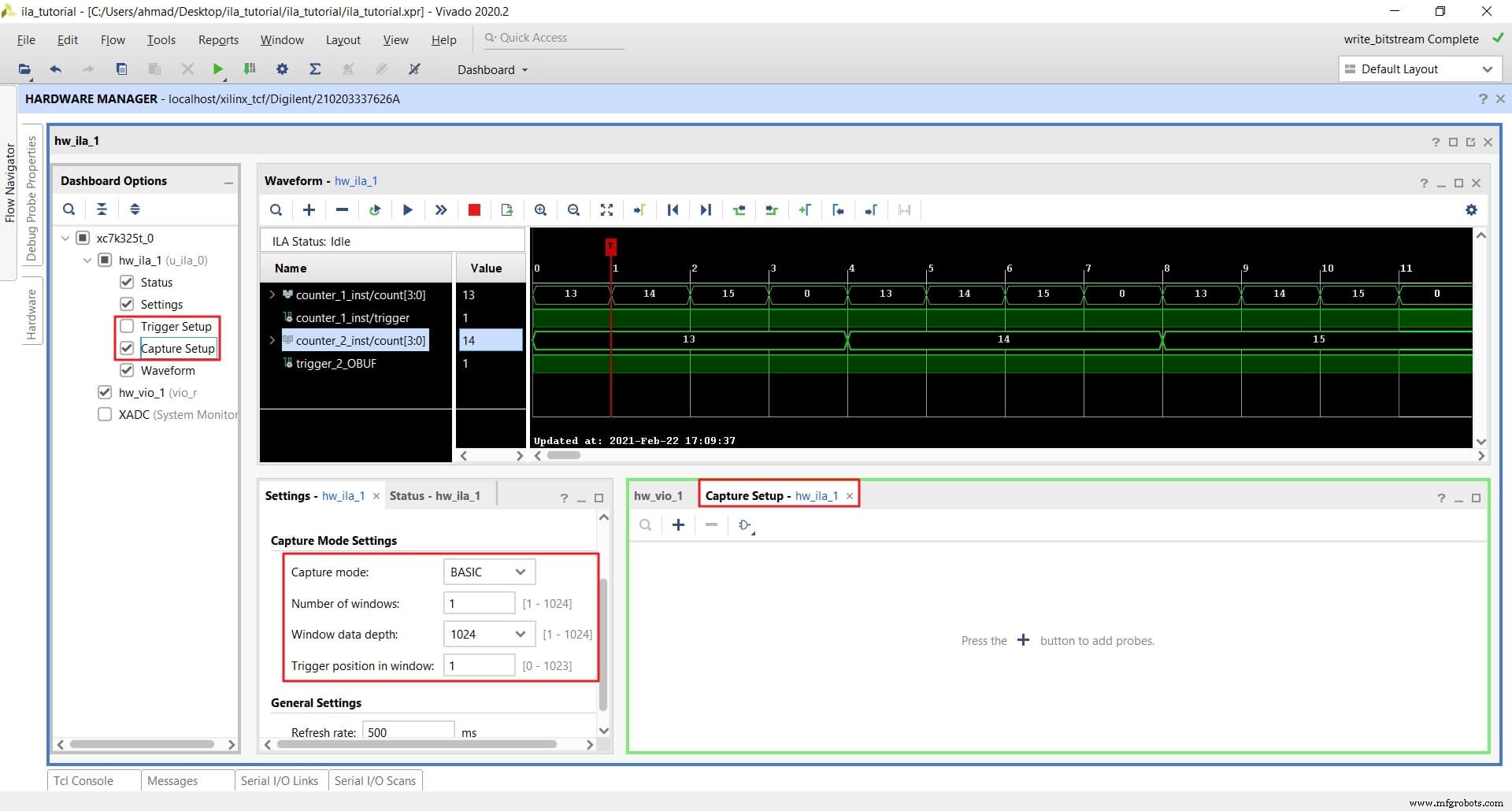

Nach der Programmierung des Geräts können wir sehen, dass sich das GUI-Layout von Vivado geändert hat, und ein neues hw_ila_1 Dashboard wurde geöffnet und enthält mehrere Fenster.

Wir minimieren einige Fenster, die wir nicht benötigen, damit wir bequem arbeiten können.

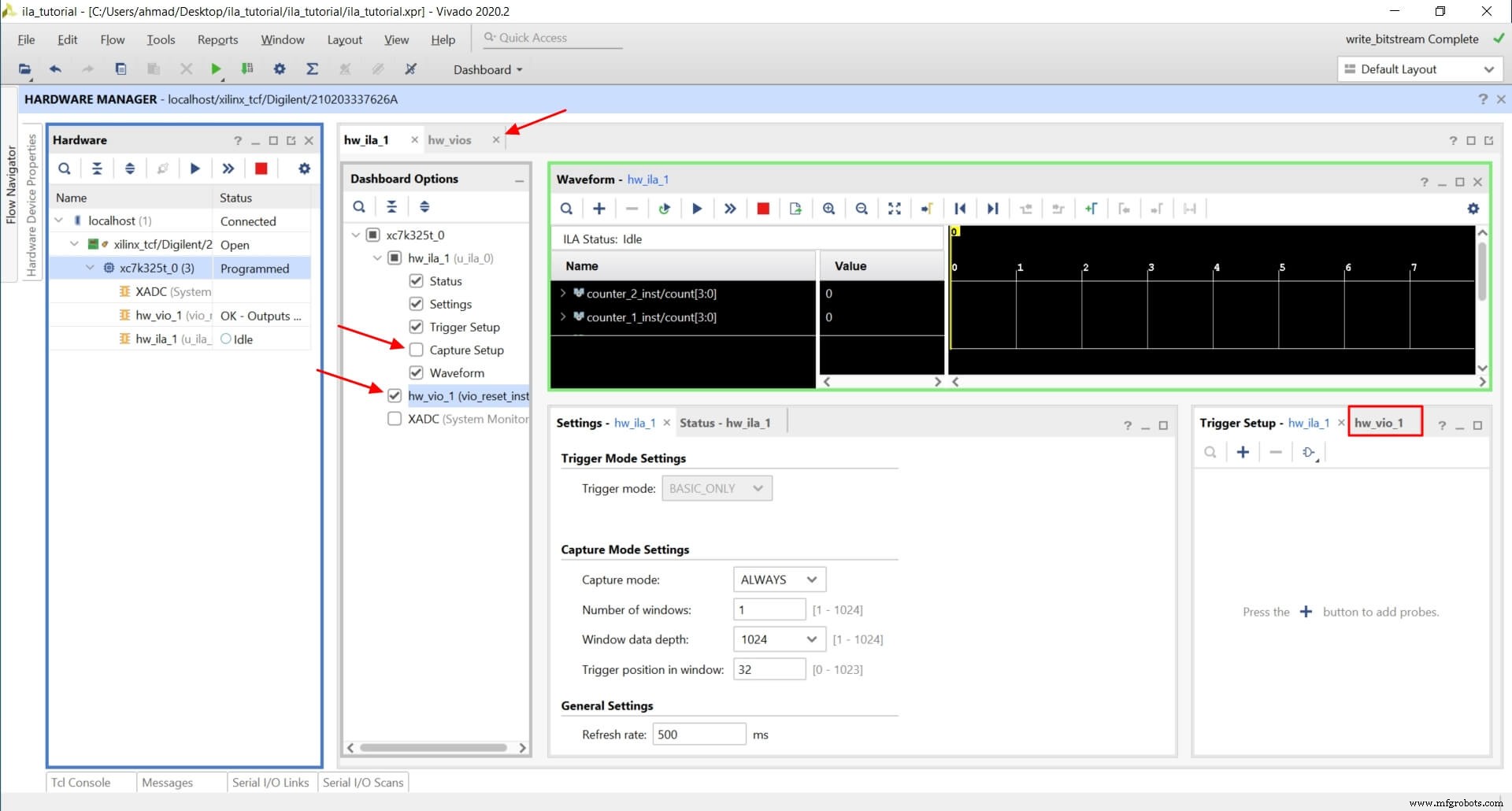

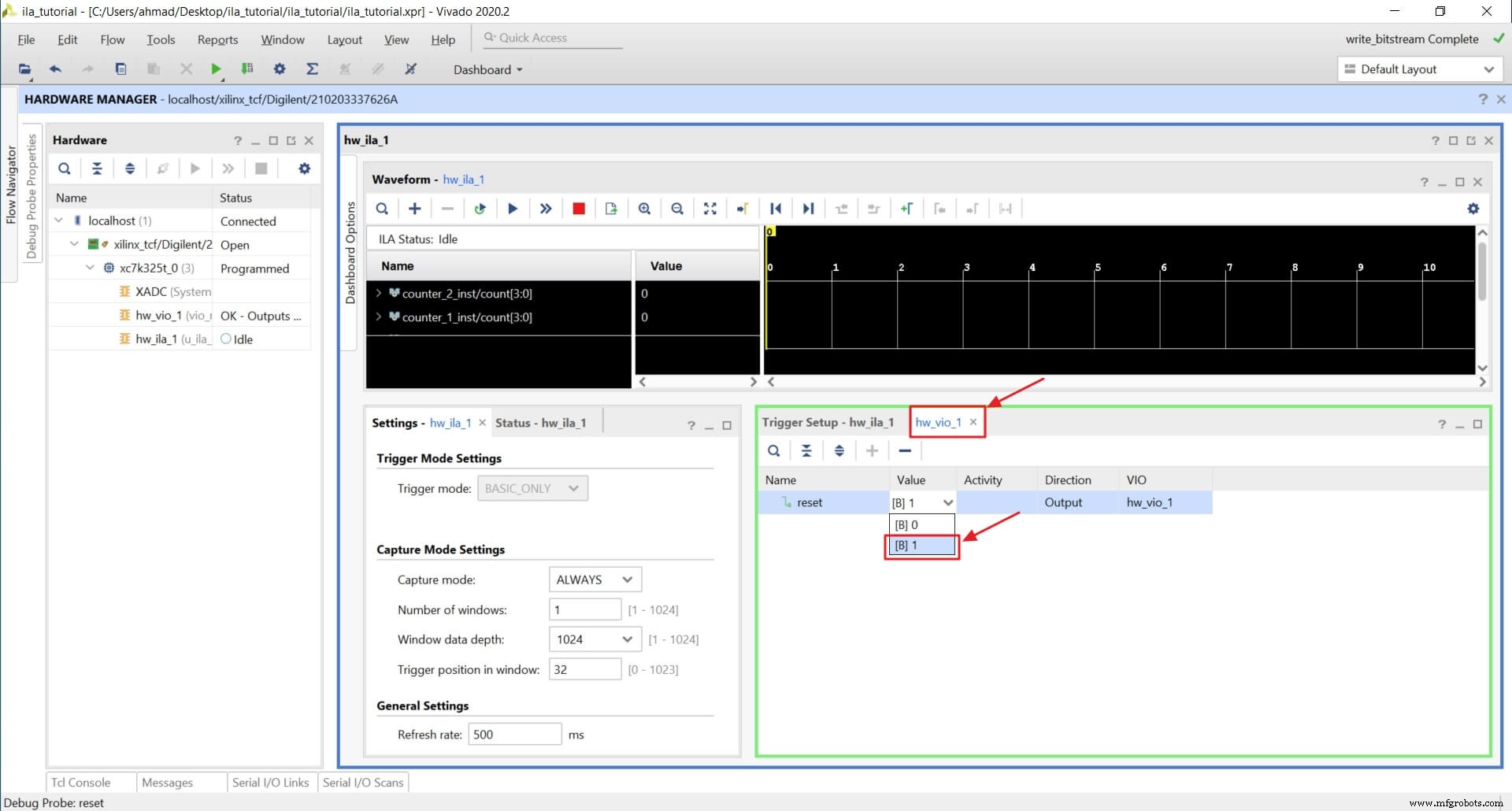

Aktivieren Sie in den Dashboard-Optionen hw_vio_1 und deaktivieren Sie Aufnahmeeinrichtung .

Schließen Sie außerdem hw_vios Tab, denn als wir hw_vio_1 überprüft haben , es wurde zum Trigger-Setup hinzugefügt Fenster.

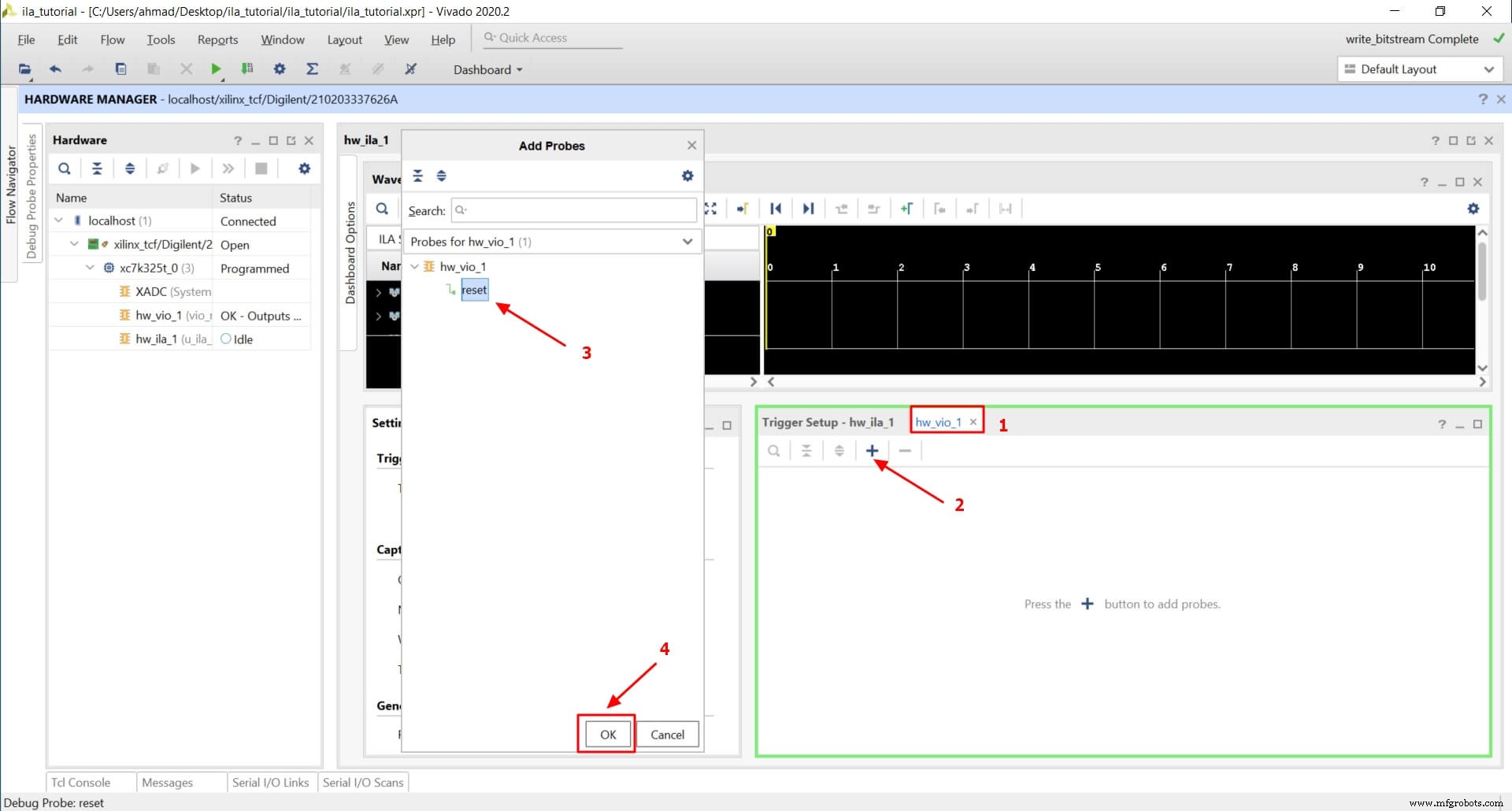

Jetzt müssen wir den reset hinzufügen Taste an das VIO, damit wir das Zurücksetzen steuern können .

Klicken Sie auf hw_vio_1 und fügen Sie dann zurücksetzen hinzu wie im Bild unten gezeigt.

Wir können das hw_vio_1 sehen enthält jetzt den Zurücksetzen prüfen.

Ändern Sie den Wert des Zurücksetzens in vio_reset auf 1, wenn es nicht 1 ist.

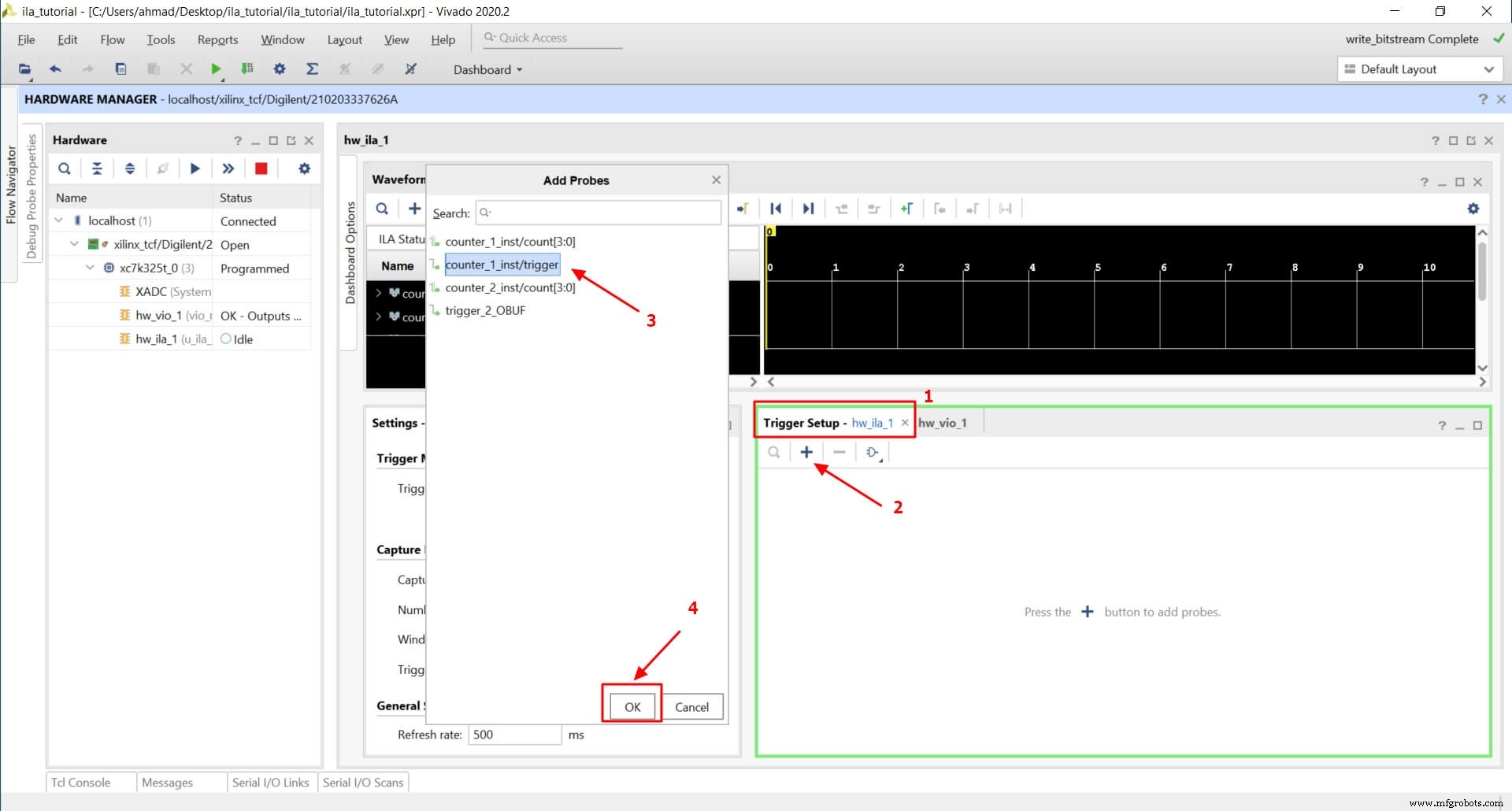

Jetzt fügen wir die Trigger hinzu, die wir verwenden werden. Eine Wertänderung eines Triggersignals veranlasst den ILA, mit der Aufzeichnung der geprüften Signale zu beginnen.

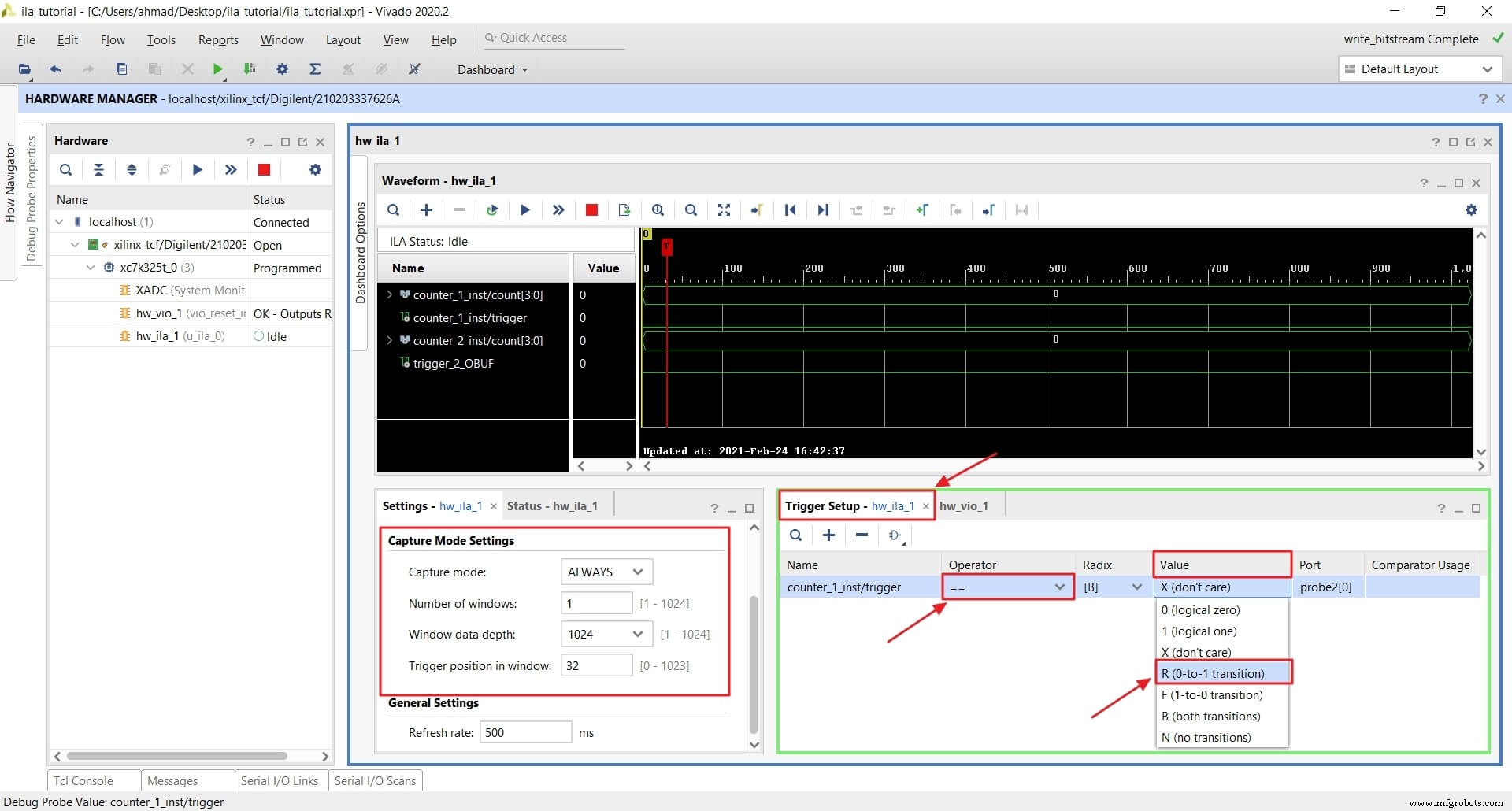

Nehmen wir an, wir wollen auf die steigende Flanke des Ausgangsports Trigger triggern (Aufzeichnung starten). von counter_1_inst . Gehen Sie dazu folgendermaßen vor:

- Gehen Sie zum Trigger-Setup – hw_ila_1 Fenster

- Klicken Sie auf das + Symbol, um einen neuen Trigger hinzuzufügen, und wählen Sie counter_1_inst/trigger und klicken Sie auf OK.

- Wir können sehen, dass der Auslöser hinzugefügt wurde, und jetzt müssen wir die Bedingung einrichten. Klicken Sie auf das Feld Wert und wählen Sie R(Übergang von 0 zu 1) . Klicken Sie auf das Feld Operator und wählen Sie ==(gleich)

Wir ändern auch die Triggerposition auf 32, was bedeutet, dass 32 Samples vor dem Triggerereignis aufgezeichnet werden, zusätzlich zu dem, was danach kommt.

Jetzt ist der Auslöser eingerichtet und bereit zum Scharfschalten.

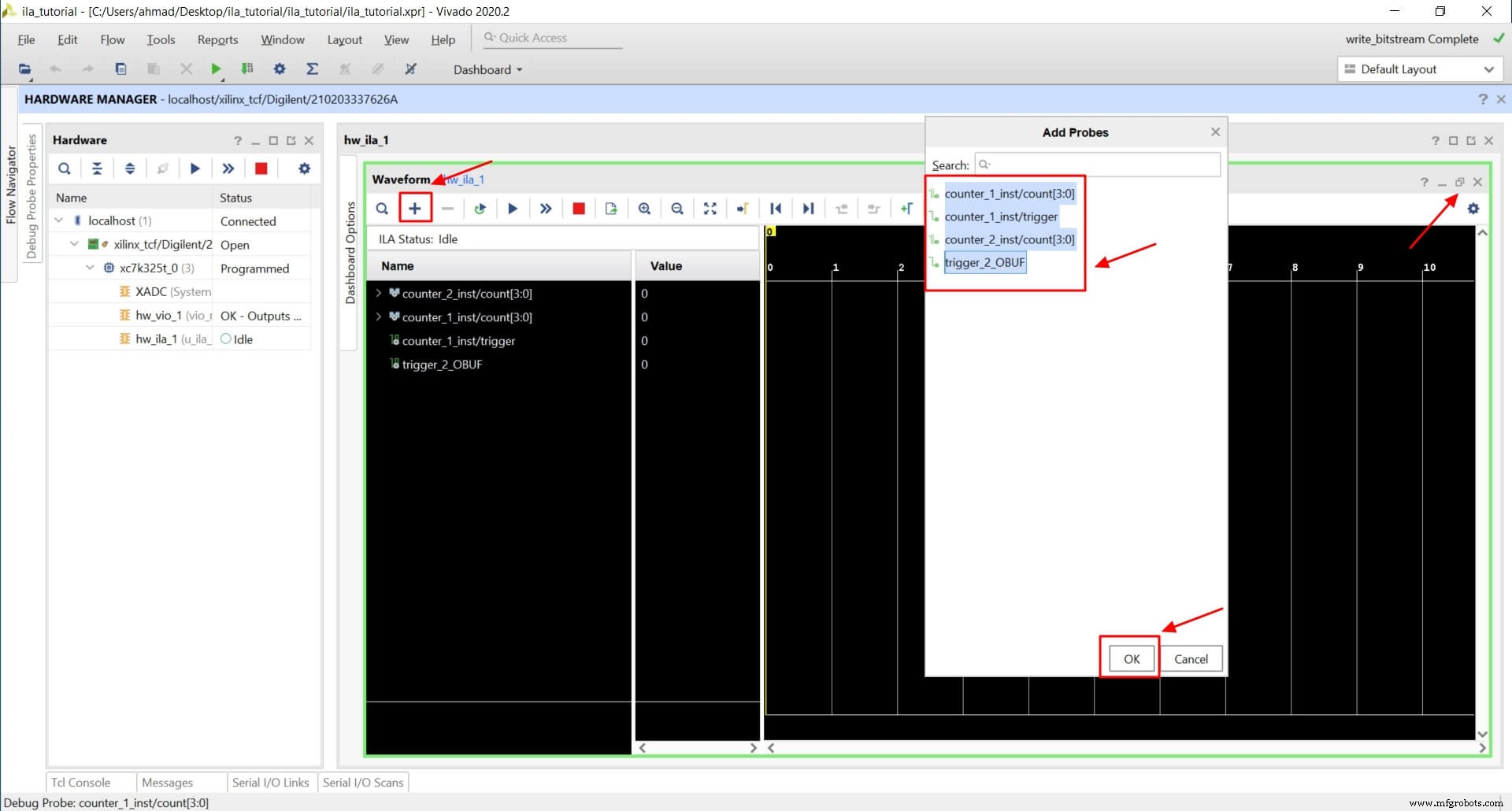

Jetzt bewegen wir uns zum Wellenformfenster um die Signale hinzuzufügen, die wir anzeigen möchten. Lassen Sie uns zuerst das innere Fenster maximieren, um eine bessere Ansicht zu erhalten.

Zweitens müssen wir der Sonde einige fehlende Signale hinzufügen. Vivado fügt normalerweise alle zugewiesenen Signale automatisch hinzu, in diesem Fall jedoch nicht.

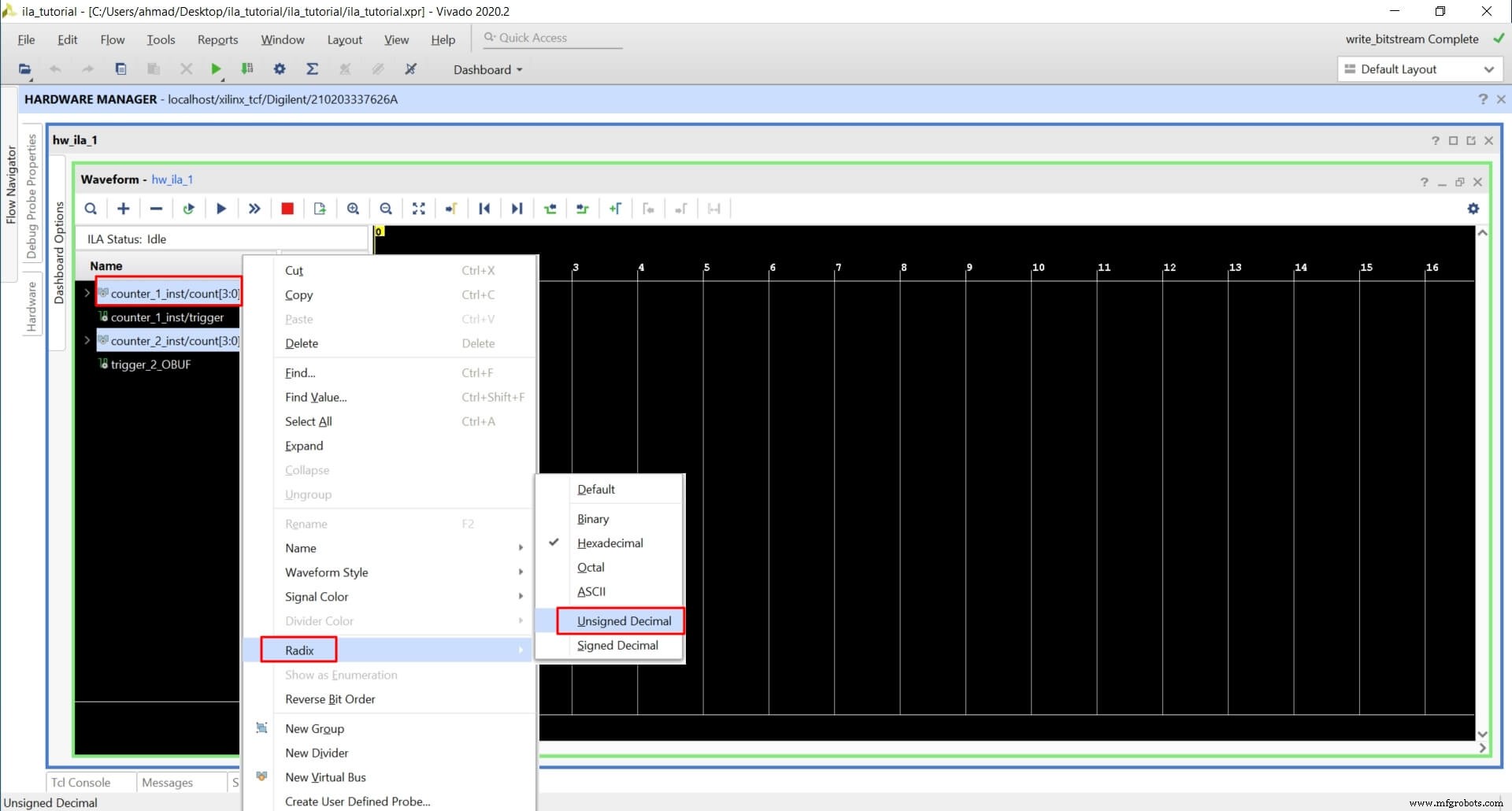

Jetzt ändern wir die Basis der Anzahl Signal an Unsigned, da es einfacher zu folgen ist.

Klicken Sie mit der rechten Maustaste auf den Zähler Signalname und wählen Sie dann Radix und dann Unsigned .

Laufen von ILA und VIO

Jetzt haben wir die Konfiguration und Anpassung des ILA abgeschlossen und können ihn ausführen.

ILA hat zwei Ausführungsmodi:Sofort und Auslöser .

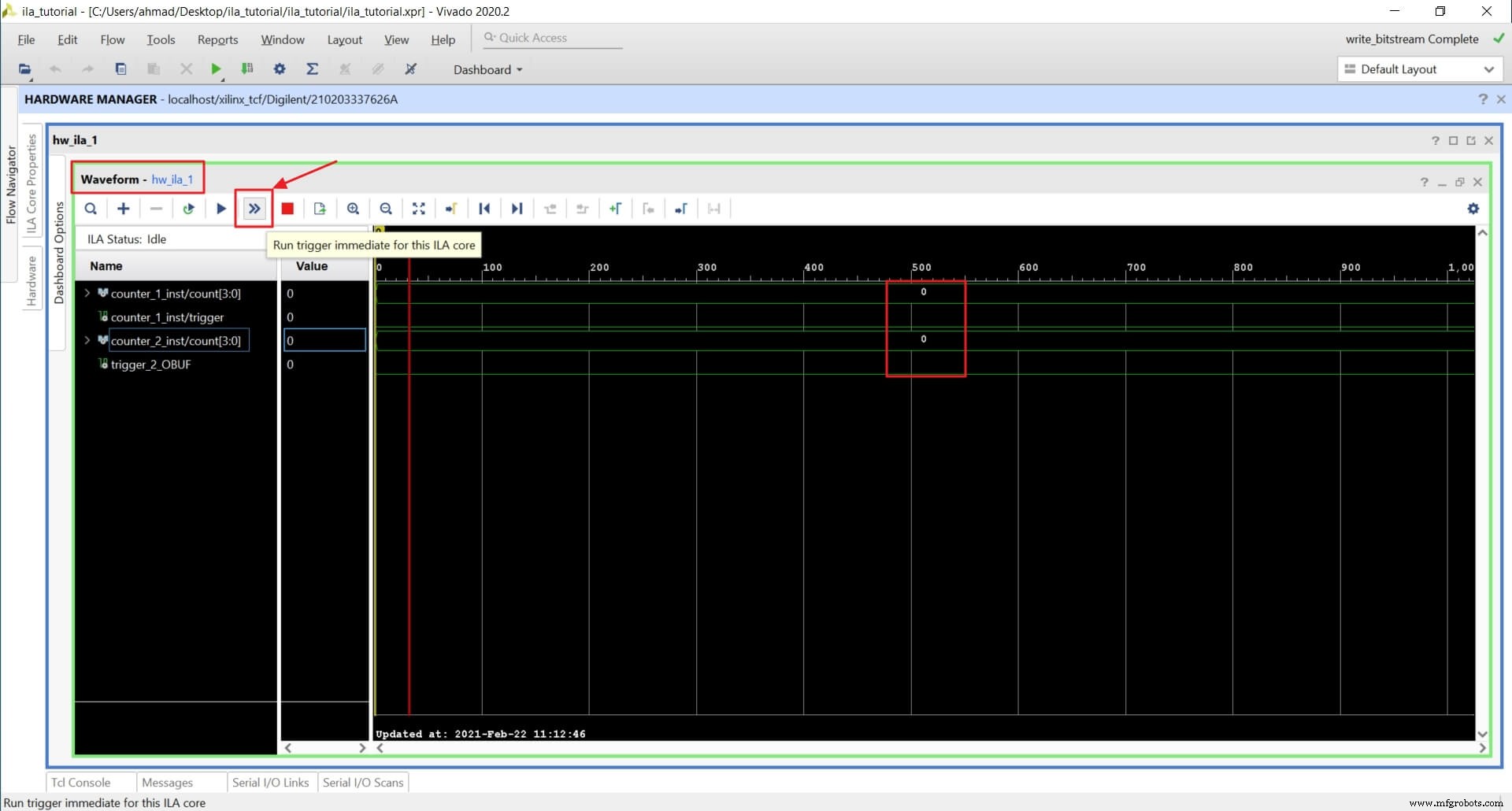

Sofortmodus

Der Immediate-Modus triggert den ILA sofort und beginnt direkt mit der Aufzeichnung der Samples, bis der FIFO voll ist.

Klicken Sie auf Trigger sofort ausführen Schaltfläche.

Wir können jetzt die aufgezeichneten Samples im Wellenformfenster sehen. Wir sehen, dass beide zählen Signale sind 0, und beide triggern Signale sind low ‘0’ weil der Zurücksetzen ist aktiv.

Trigger-Modus

Der Trigger-Modus erfordert, dass wir eine Bedingung für mindestens einen Trigger einrichten und ihn aktivieren. Der ILA wartet weiter darauf, dass die Bedingung des aktivierten Triggers wahr wird, und beginnt dann direkt mit der Aufzeichnung der Samples, bis der FIFO voll ist.

Wir haben den Trigger bereits hinzugefügt und ihn auf R(0-zu-1-Übergang) eingestellt .

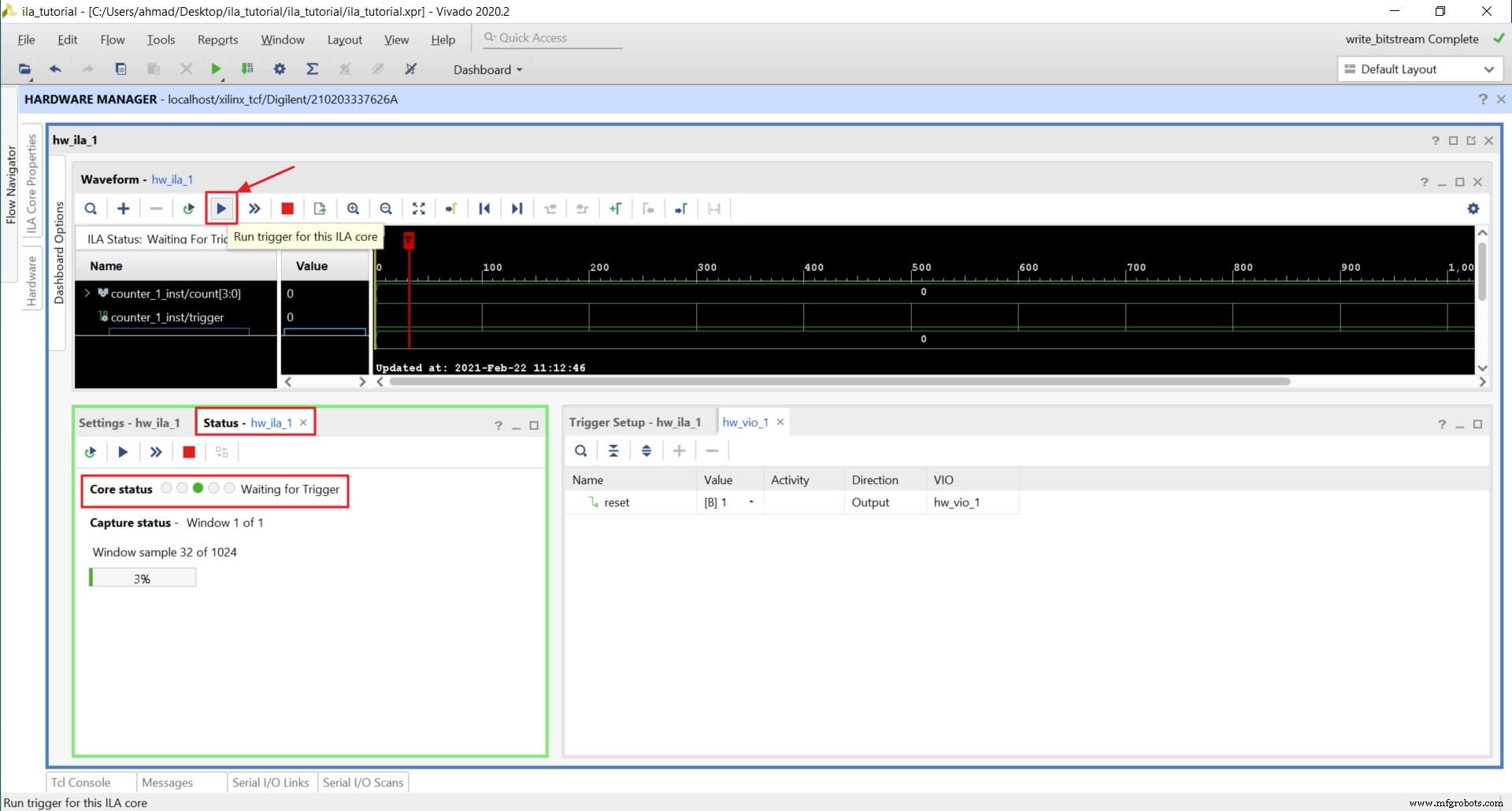

ILA mit einem Trigger ausführen

Ändern Sie Zurücksetzen zurück zu 1 von vio_reset .

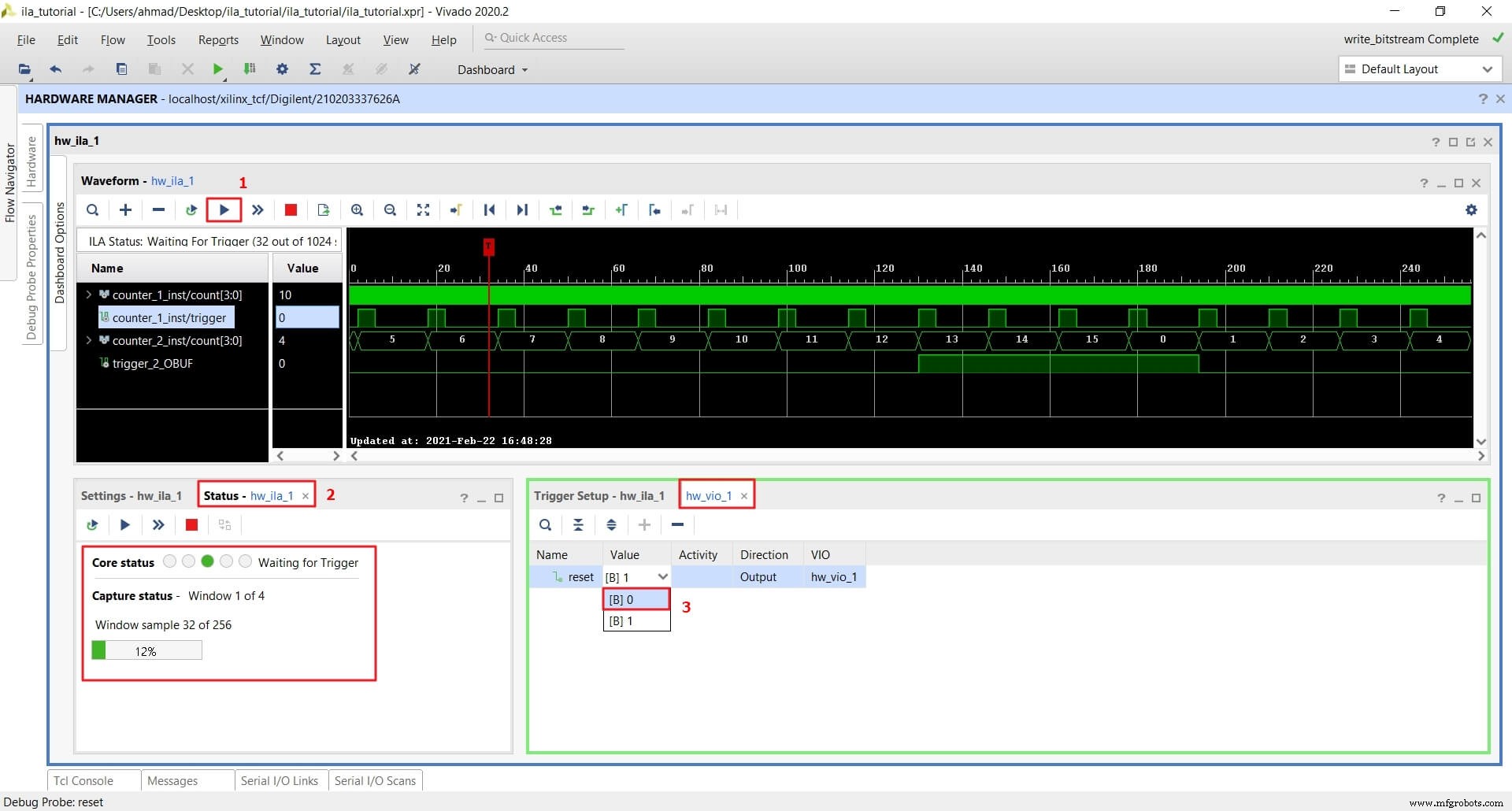

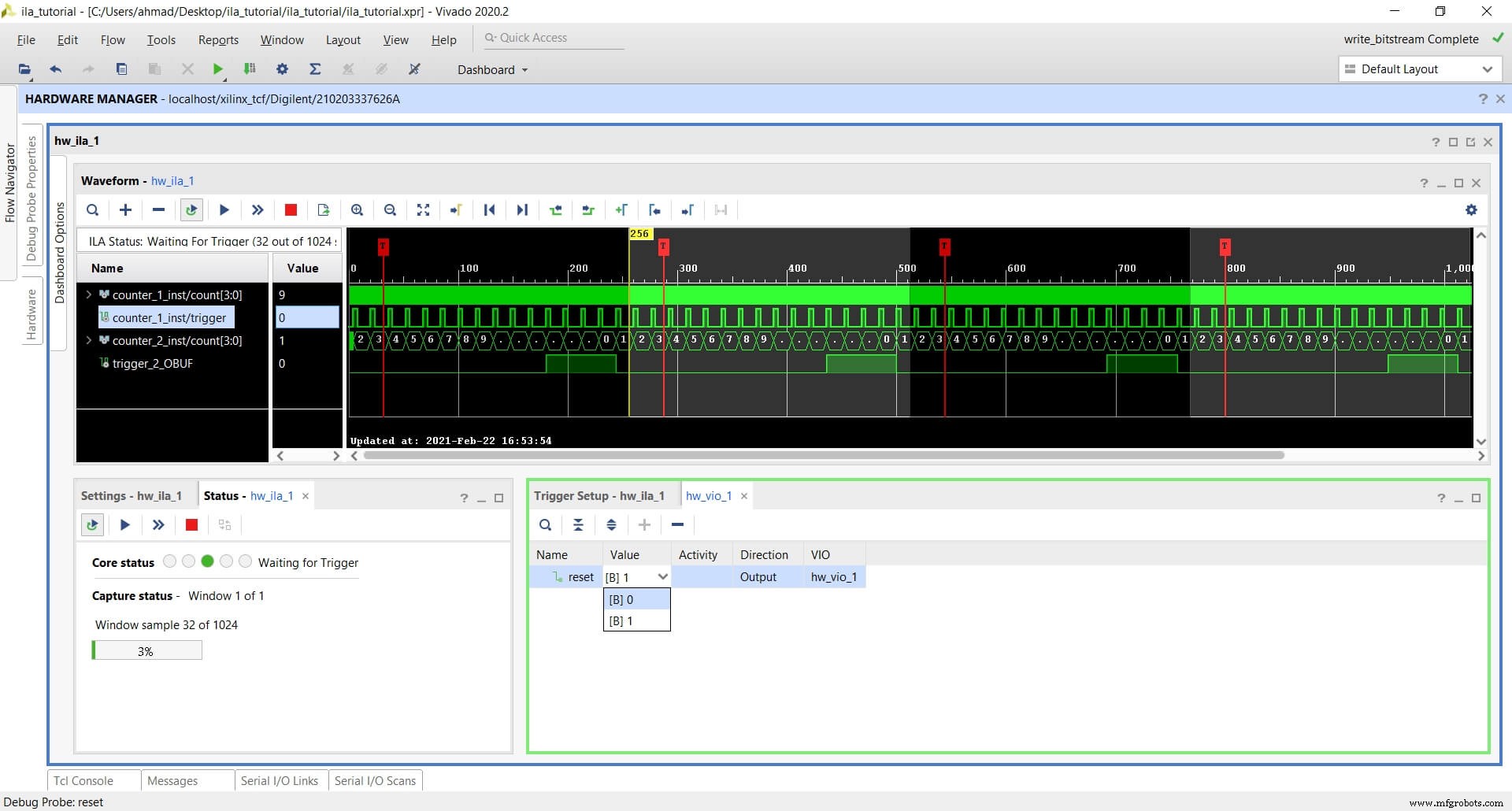

Klicken Sie auf das Fenster Status hw_ila_1 . Wir sehen, dass der Core-Status Idle ist da keine Auslöser aktiviert sind. Klicken Sie auf den Auslöser ausführen Taste, und das wird den Abzug aktivieren.

Wir sehen jetzt, dass sich der Core-Status zu Warten auf Trigger geändert hat . Als Zurücksetzen hoch ist, gibt es keine Aktivität auf unserem Triggersignal (Port trigger von counter_1_inst ), und ILA wartet.

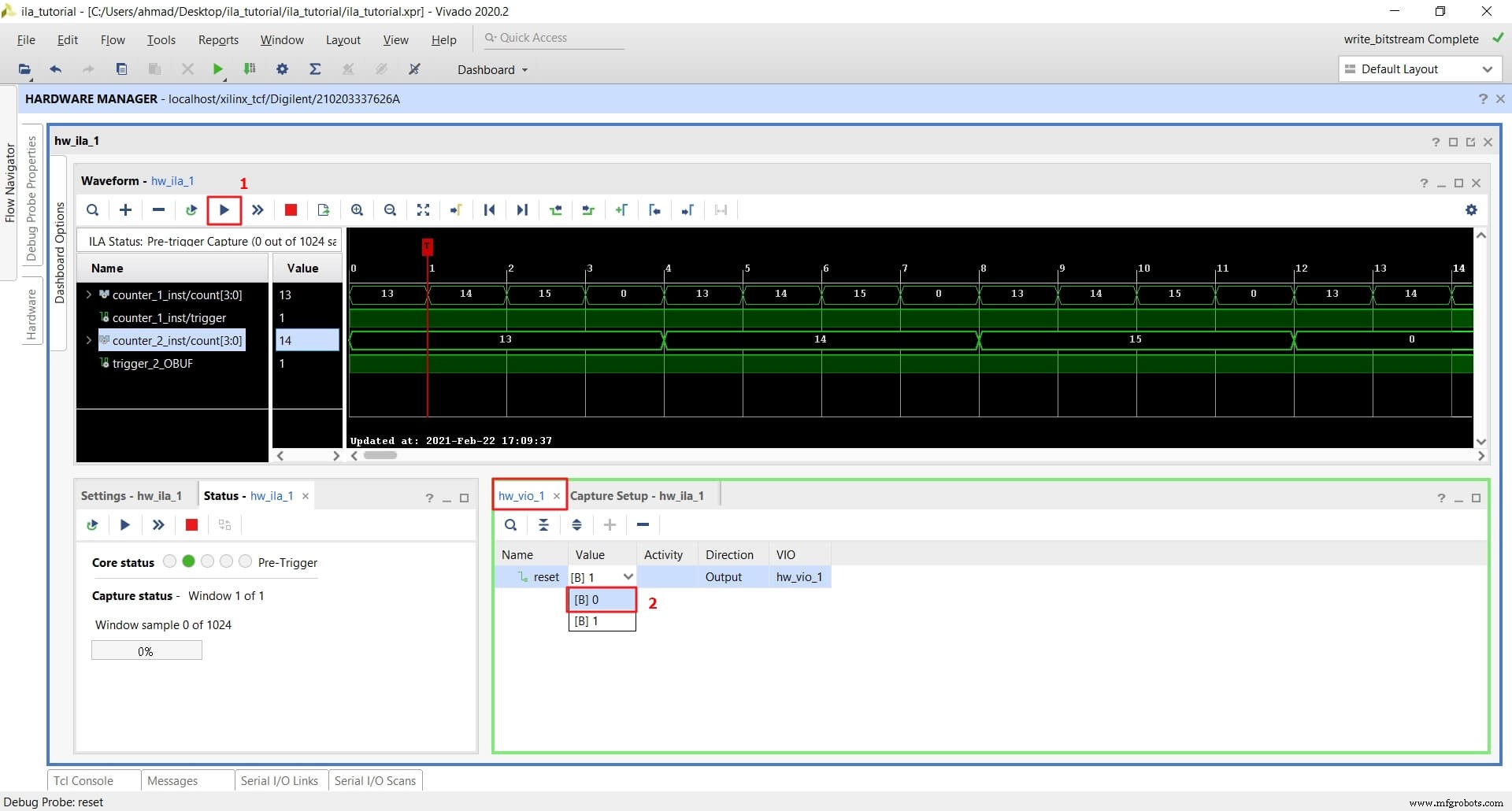

Lassen Sie uns nun den Zurücksetzen ändern auf 0 damit die Zähler anfangen zu arbeiten.

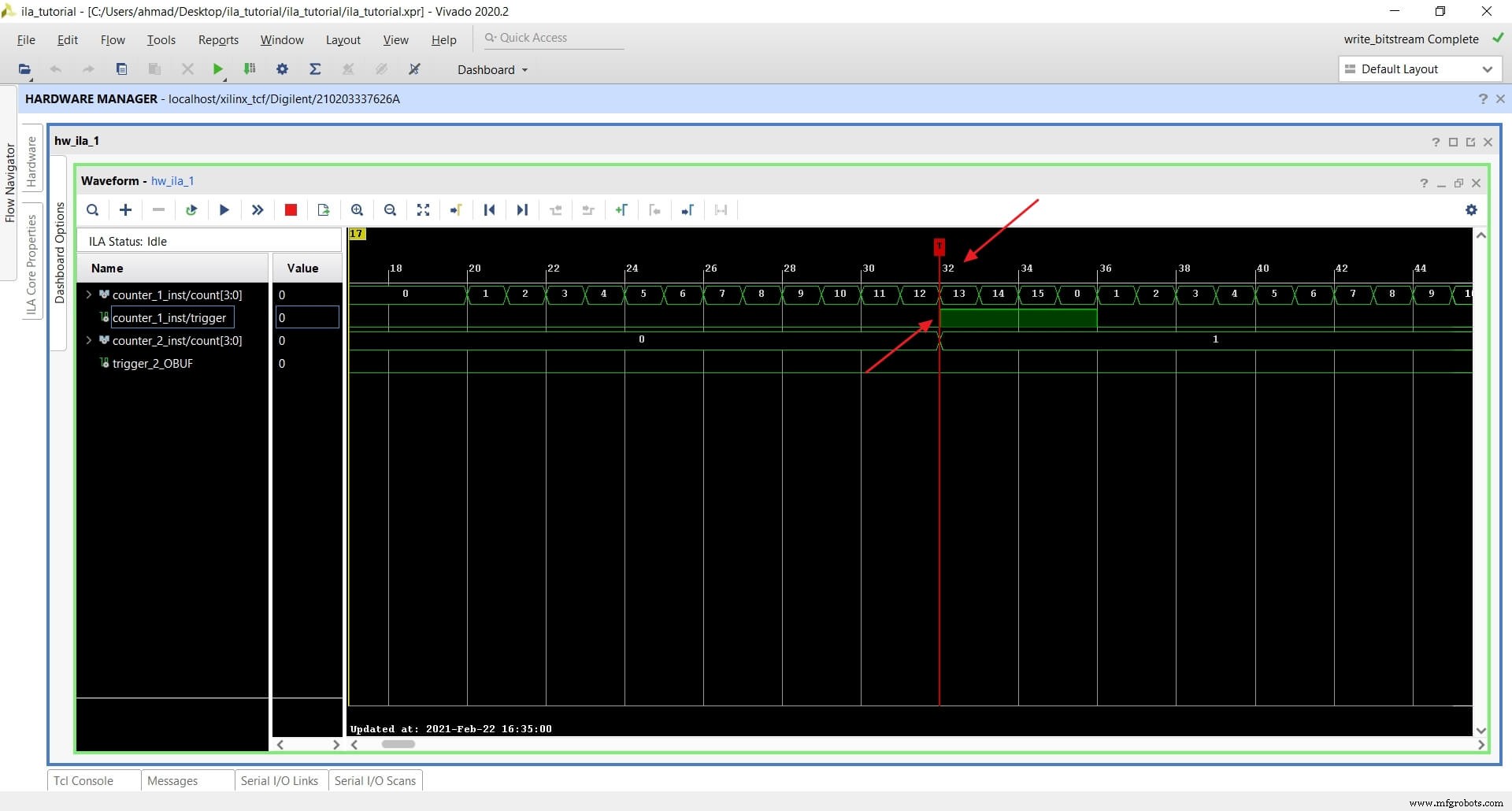

Wir sehen jetzt, dass der ILA getriggert wurde und die Samples aufgezeichnet hat und der Core-Status wieder auf Idle geändert wurde .

Wir sehen die rote vertikale Linie (Marker) auf der steigenden Flanke unseres Triggersignals (Port Trigger von counter_1_inst ) und befindet sich auf Position 32 . Wir können auch überprüfen, ob das Signal count ist korrekt verhält und das Signal counter_1_inst/trigger ist für vier Taktzyklen zwischen 12 und 15 hoch (die Ausgabe wird um einen Taktzyklus verzögert).

Wenn wir etwas herauszoomen, können wir auch das Verhalten von count überprüfen und Auslöser Signale für counter_2_inst .

ILA mit mehreren Auslösern ausführen

Wir können eine Kombination von Auslösern für komplexe oder fortgeschrittene Bedingungen verwenden. Um mehrere disjunkte Zeitrahmen in derselben Wellenform zu erfassen, können wir mehrere Trigger verwenden, die wiederholt ausgelöst werden.

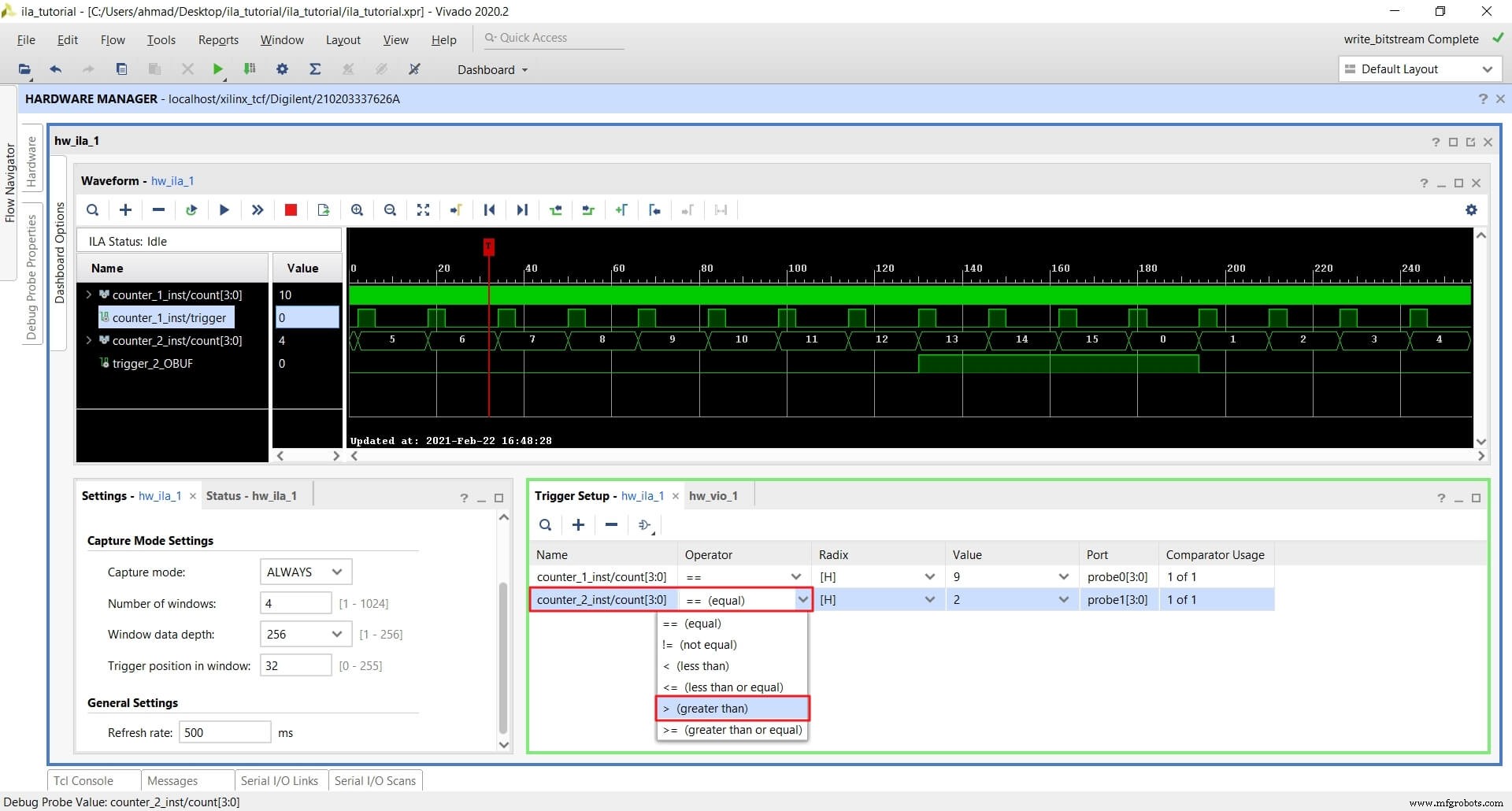

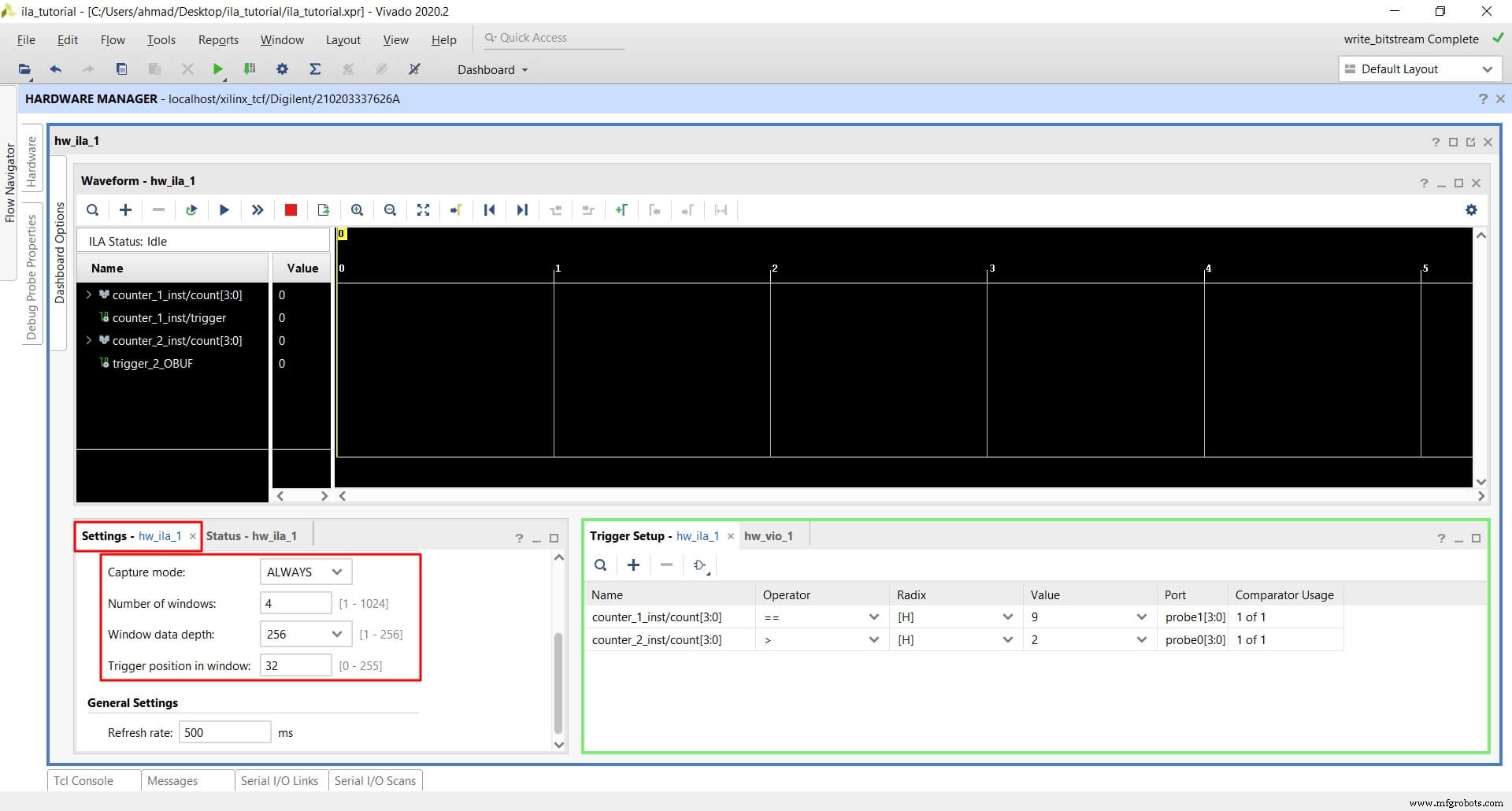

Nehmen wir beispielsweise an, wir möchten auslösen, wenn count Signal von counter_1_inst gleich 9 ist (count ==9) und wenn count Signal von counter_2_inst größer als 2 ist (Anzahl> 2). Um dies zu tun und den FIFO in vier Zeitfenster aufzuteilen, folgen Sie diesen Schritten:

- Ändern Sie Zurücksetzen zurück zu 1 von vio_reset

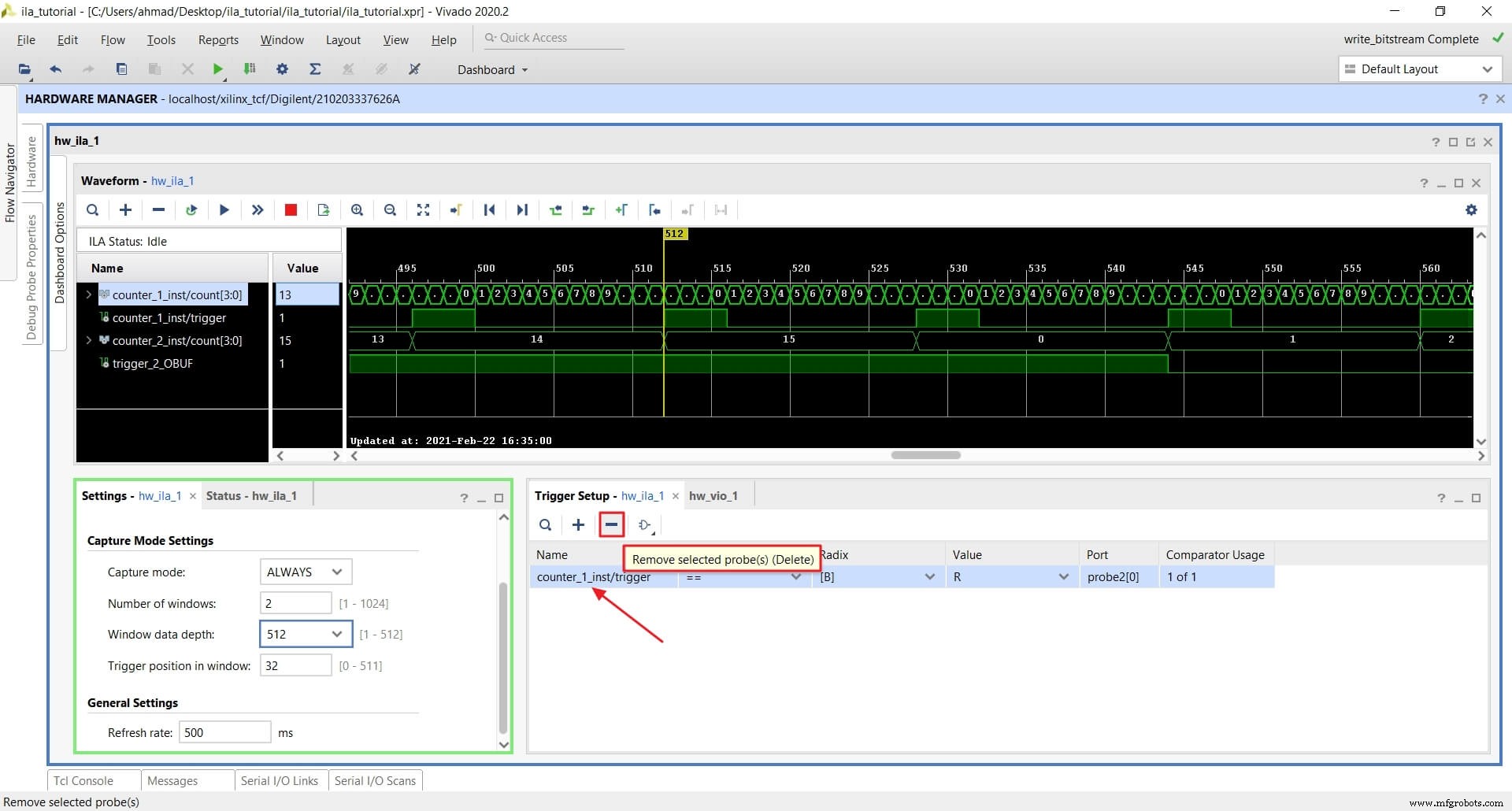

- Entfernen Sie die vorherige Triggersonde:

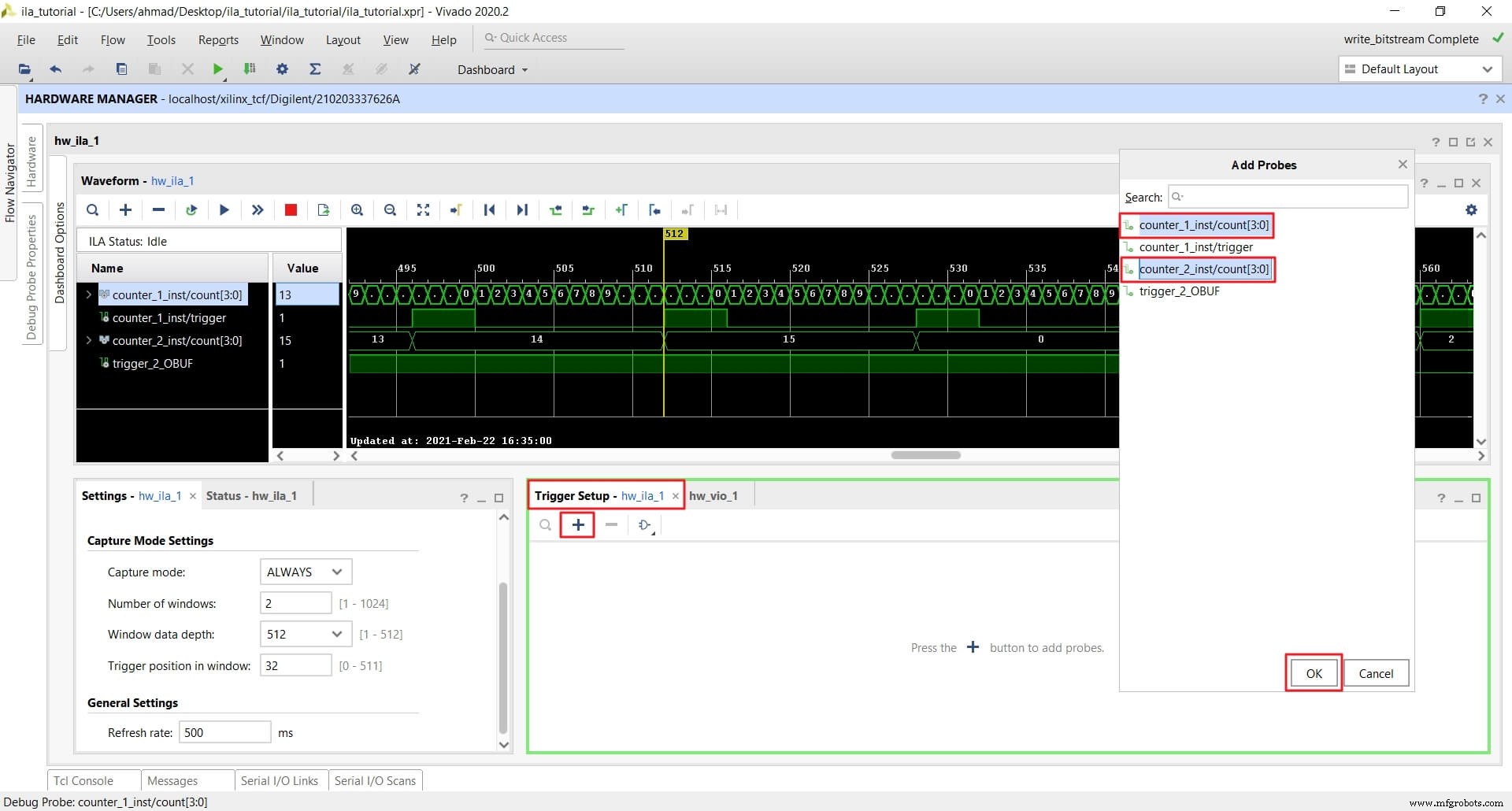

- Fügen Sie beide Anzahl hinzu Signale als Auslöser:

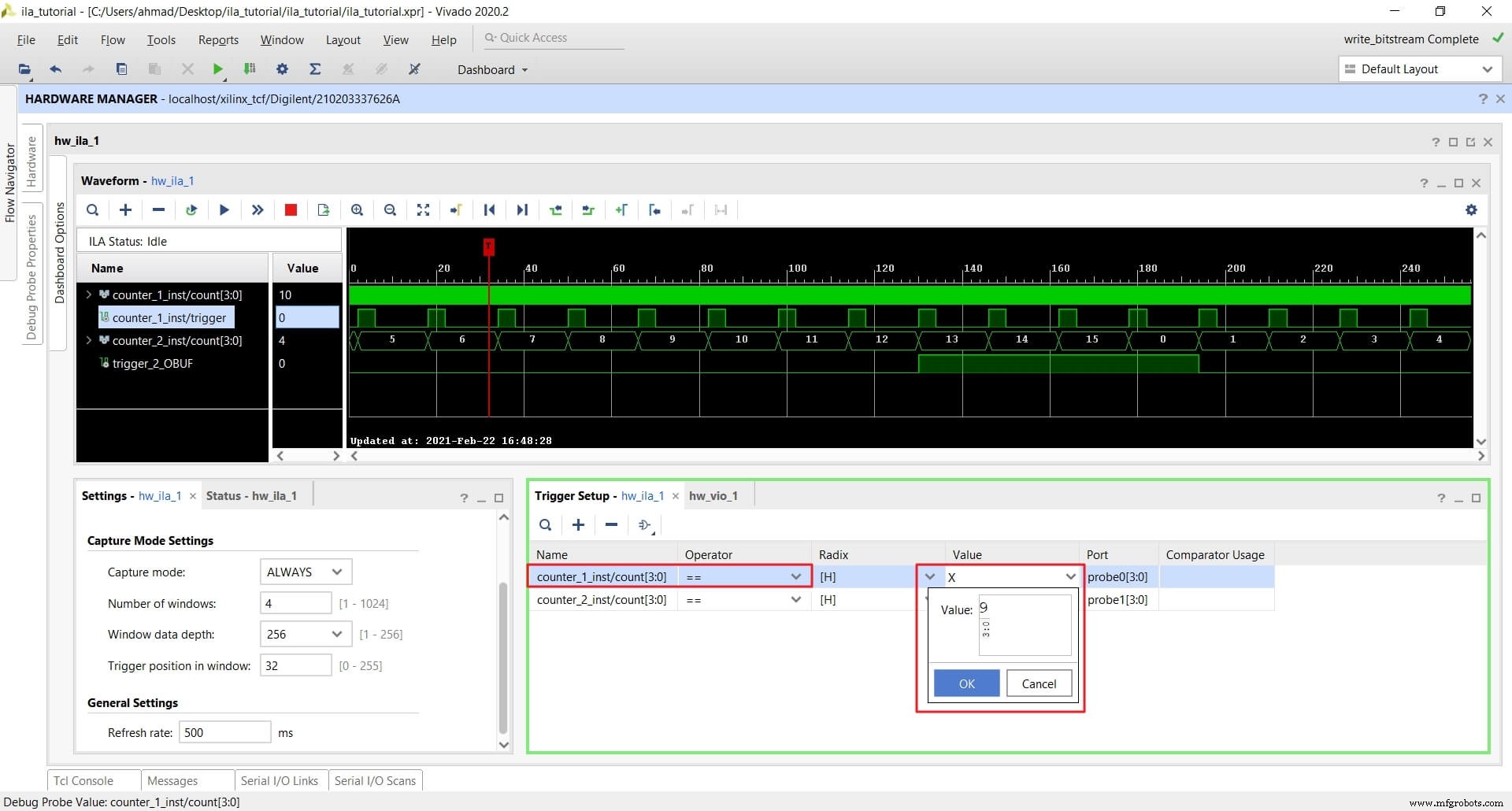

- Konfigurieren Sie die Anzahl des Signals für counter_1_inst bis (count ==9):

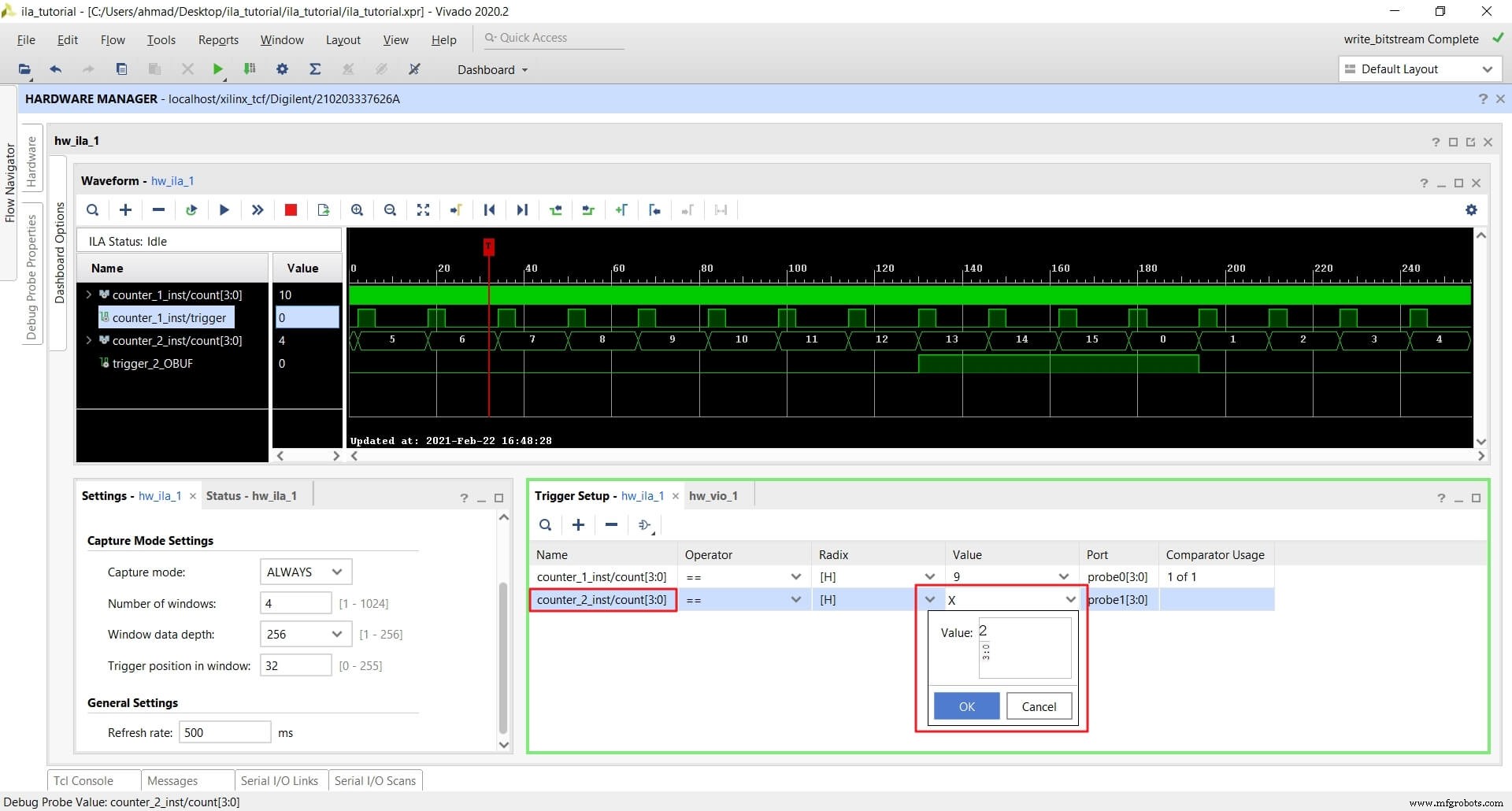

- Konfigurieren Sie die Anzahl des Signals für counter_2_inst bis (count> 2):

- Stellen Sie die Anzahl der Fenster auf 4 ein und FIFO-Tiefe auf 256, und Position auf 32 .

- Klicken Sie auf den Auslöser ausführen Taste, und das wird den Abzug aktivieren. Beachten Sie das im Fenster Status hw_ila_1 , ist der Erfassungsstatus jetzt Fenster 1 von 4 weil wir vier Fenster haben.

Ändern Sie Zurücksetzen zurück auf 0 von vio_reset .

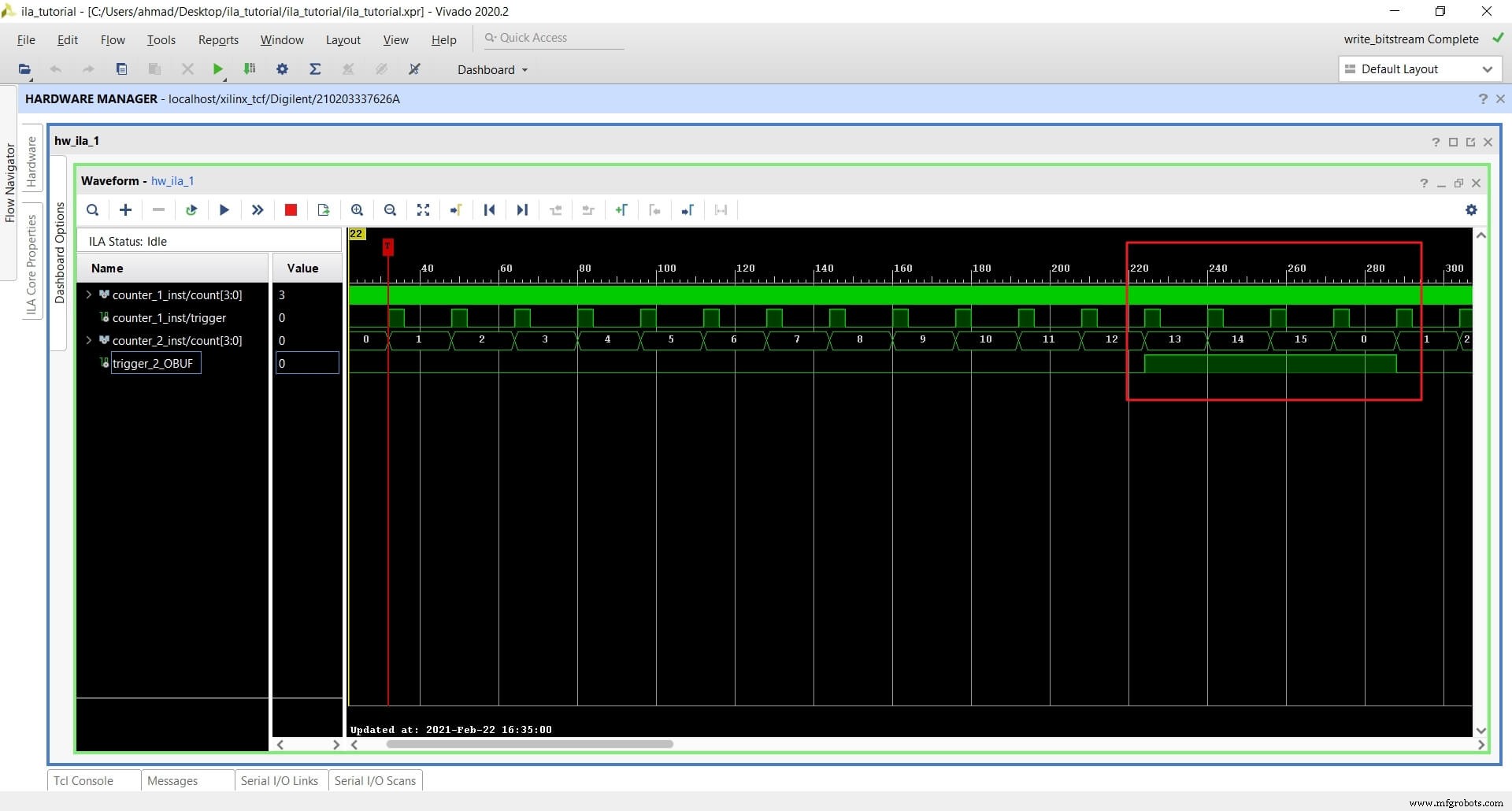

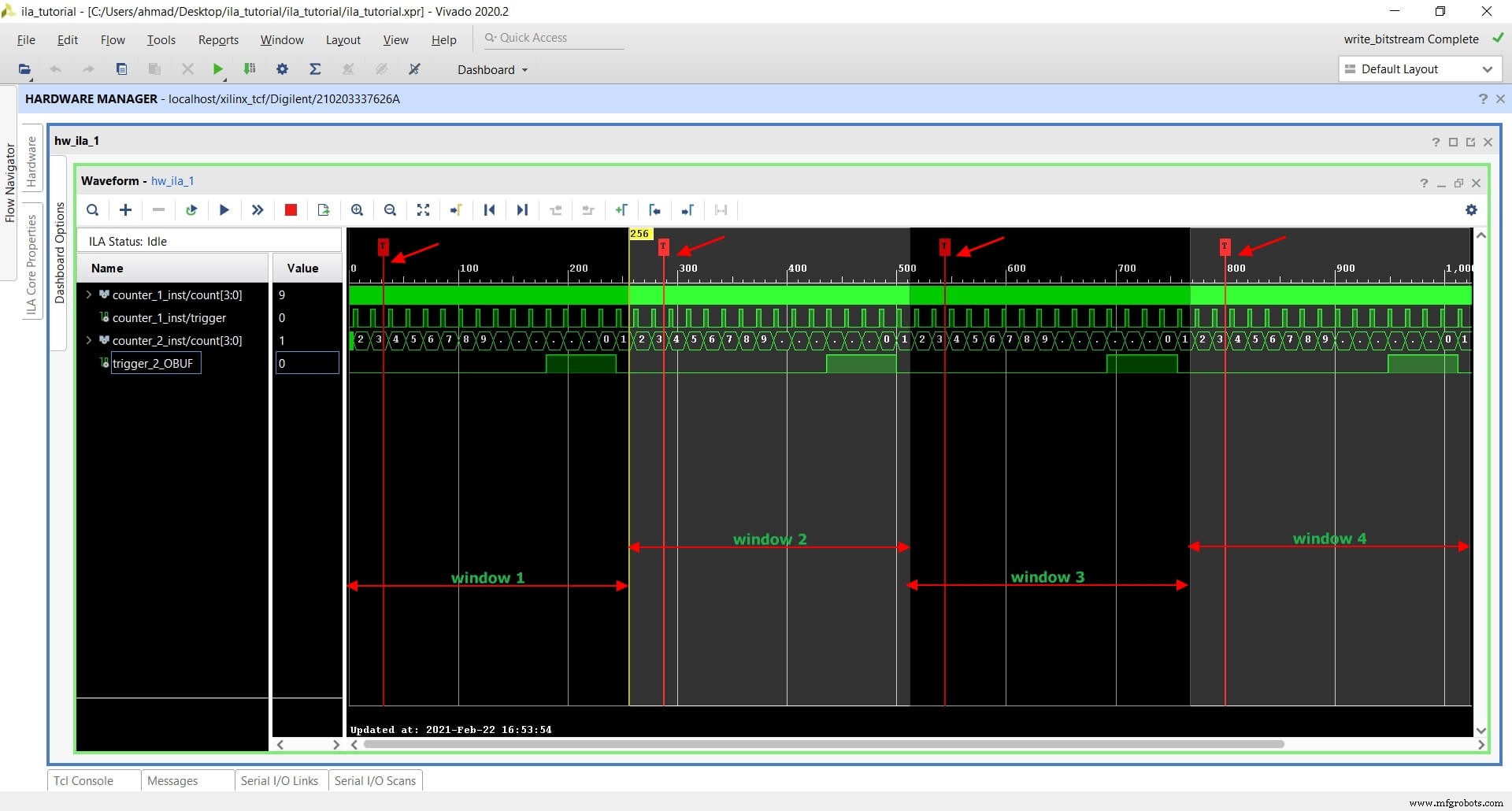

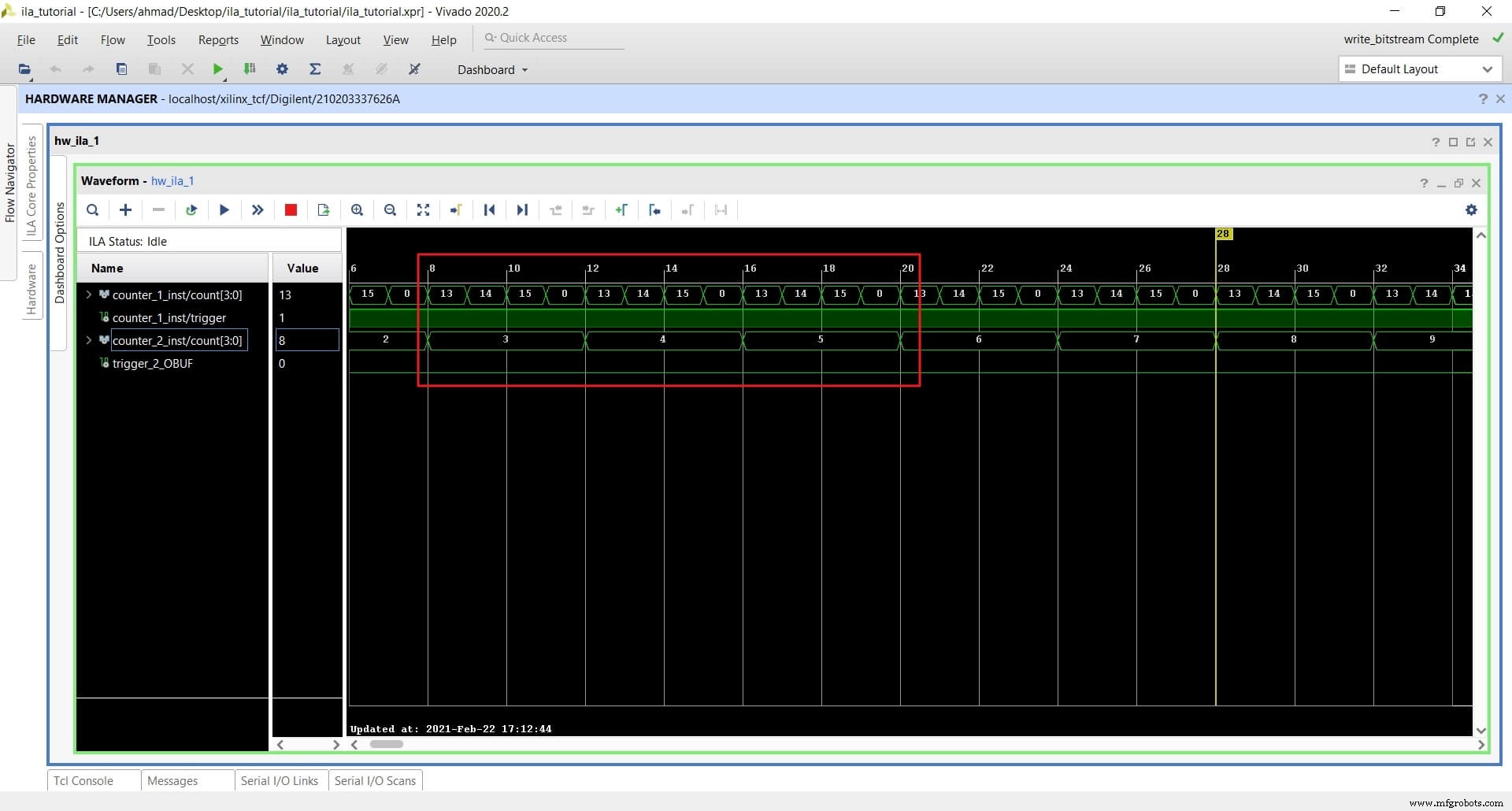

Maximieren Sie das Wellenformfenster. Wir sehen jetzt, dass wir vier Fenster und einen Trigger haben, der jedem Fenster zugeordnet ist. Beachten Sie, dass diese Fenster unabhängig und nicht fortlaufend sind.

Der ILA wartet auf das Auslöseereignis, und wenn dies der Fall ist, verwendet der ILA das erste Fenster, um 256 Abtastungen aufzuzeichnen. It then immediately waits for the next trigger until all the windows are full.

Running ILA with Auto re-trigger mode

ILA has a nice feature called Auto re-trigger that will automatically arm the trigger after it gets triggered. It is useful when monitoring events that occur seldom and you want to run a test overnight. Or you can use it when the trigger happens so often and fast that you cannot arm the trigger manually to capture the samples repeatedly.

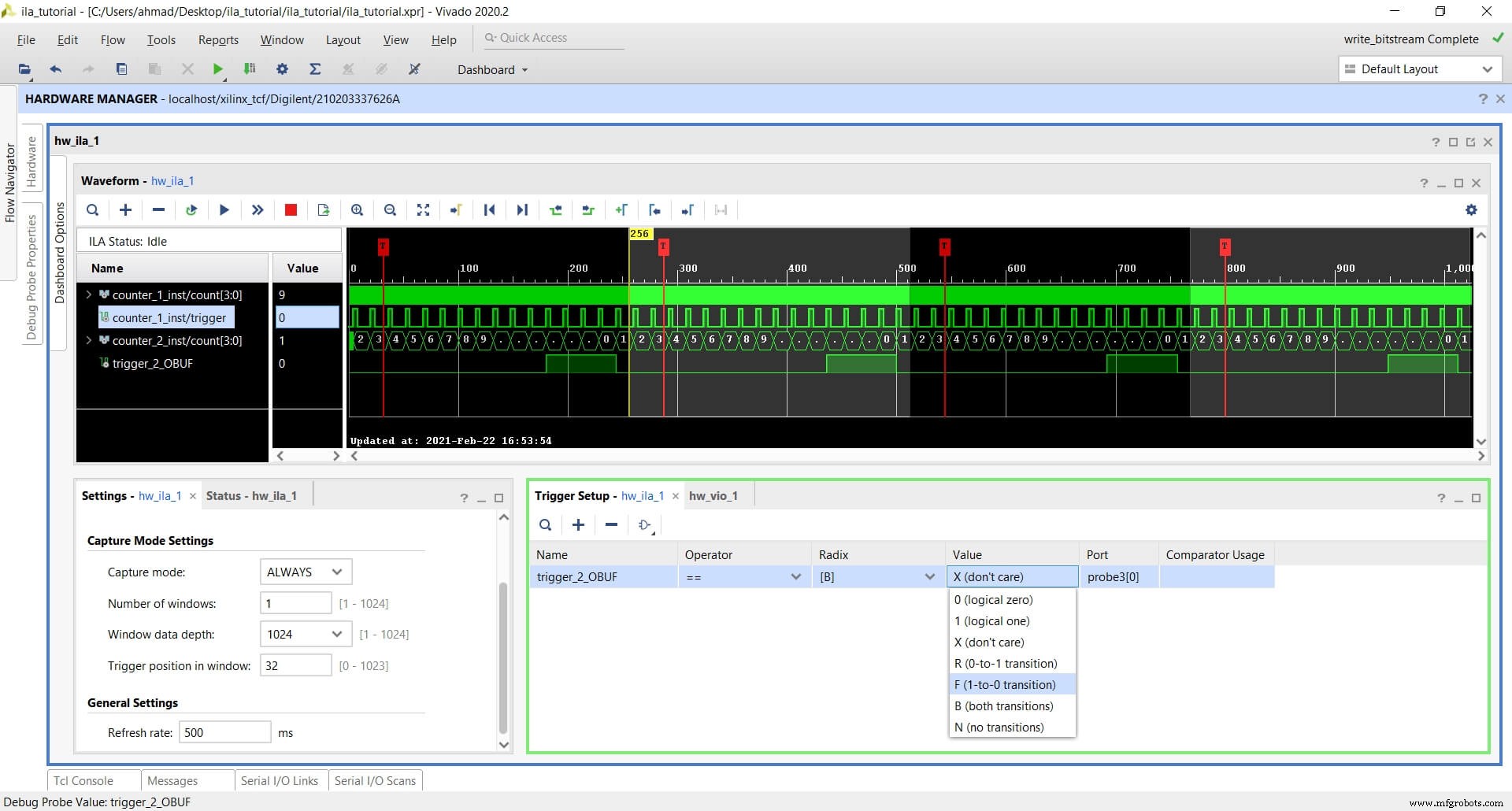

Let us assume that the output port trigger of counter_2_inst gets asserted every 3 hours, and you want to record the data each time it happens. To use the Auto trigger, follow these steps:

- Change reset back to 1 from vio_reset

- Remove the previous trigger probe

- Add trigger_2_OBUF signal as trigger:

- Configure the trigger to the condition to equal (==) and falling edge F(1-to-0 transition)

- Configure the number of windows to 1 and FIFO depth to 1024, and position to 32:

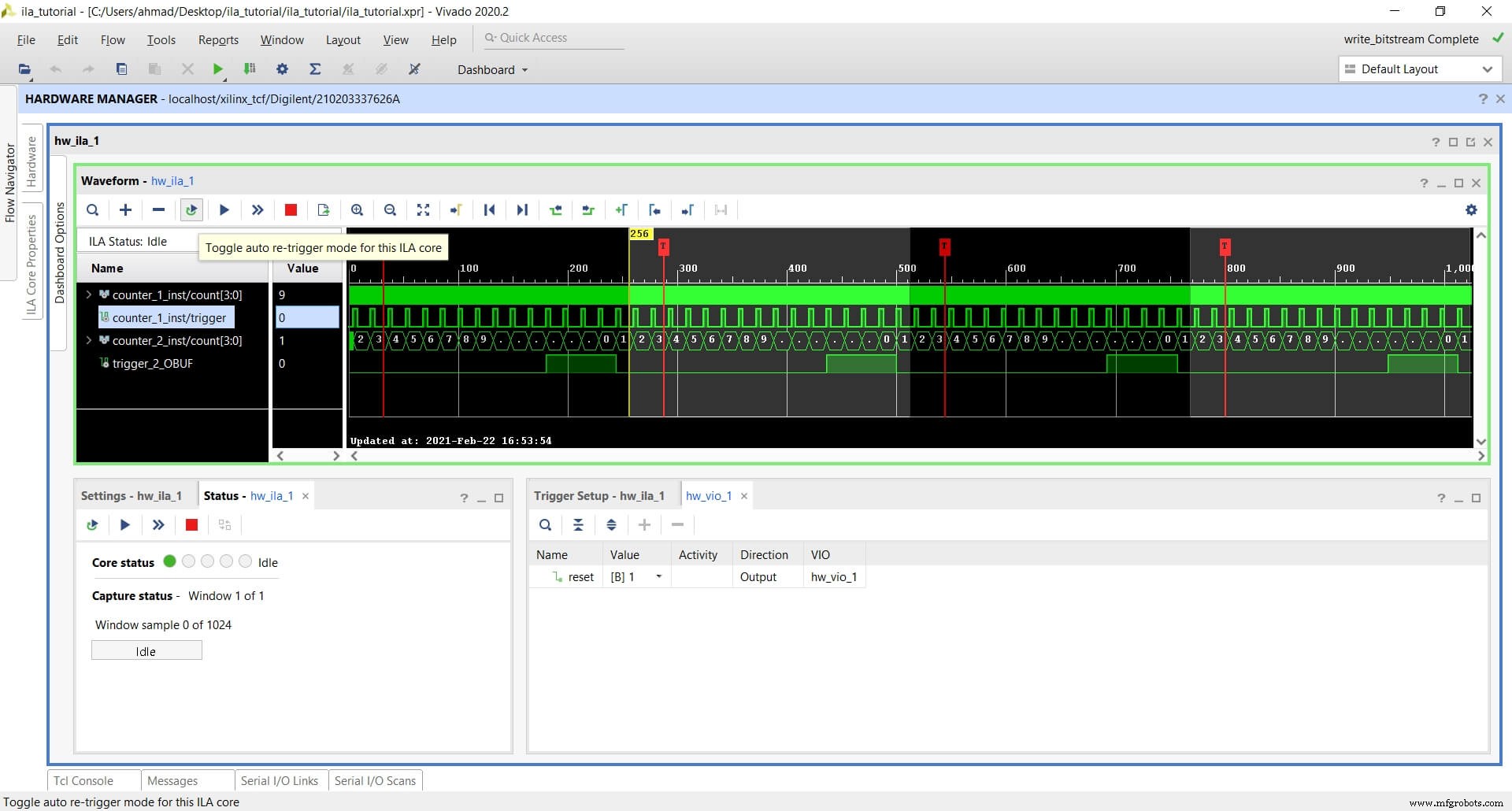

- Click on Auto re-trigger button:

- Finally, change reset back to 0 from vio_reset:

We can see now that the waveform window is getting refreshed and updated as the trigger happen. It is fast, but the behavior is noticeable.

Click on Stop trigger and toggle Auto re-trigger .

Running ILA with Capture mode

Another feature of ILA is the Capture mode . In some cases, you are not interested in recording all the data but rather capture a specific sample. Capture mode helps you filter out data and record only the samples you are interested in.

Let’s say we are only interested in sampling when the output port trigger of counter_1_inst is ‘1’ AND the output port trigger of counter_2_inst is ‘0’.

To use Capture mode to achieve this, follow these steps:

- Change reset back to 1 from vio_reset

- Remove the previous trigger probe

- From the dashboard, Uncheck Trigger Setup and check Capture Setup . Notice that a Capture Setup window will appear. From the Settings – hw_ila_1 window, Change Capture mode to BASIC , the window to 1, the FIFO depth to 1024, and position to 1:

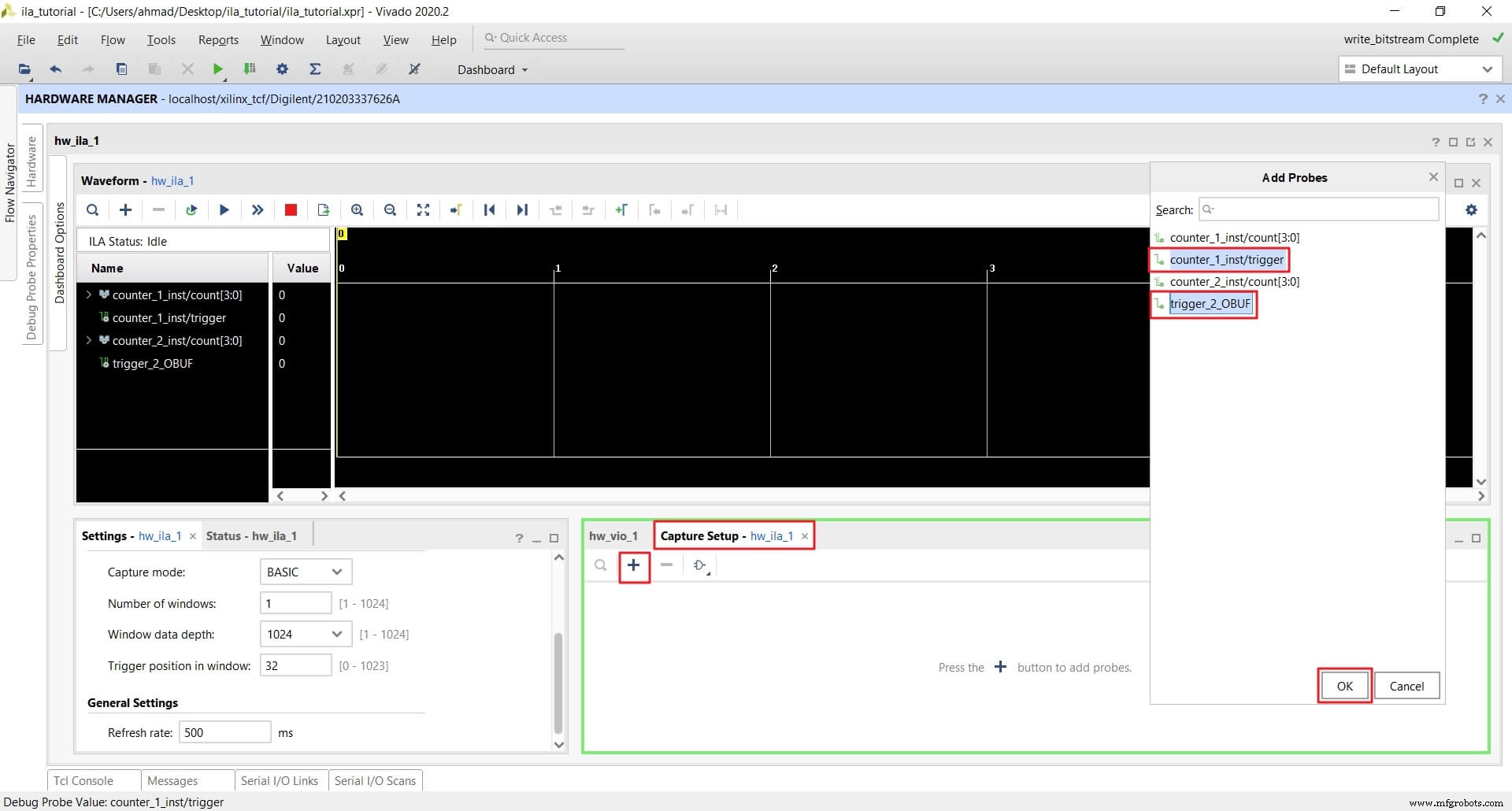

- Add trigger_2_OBUF , and counter_1_inst/trigger from the Capture Setup window:

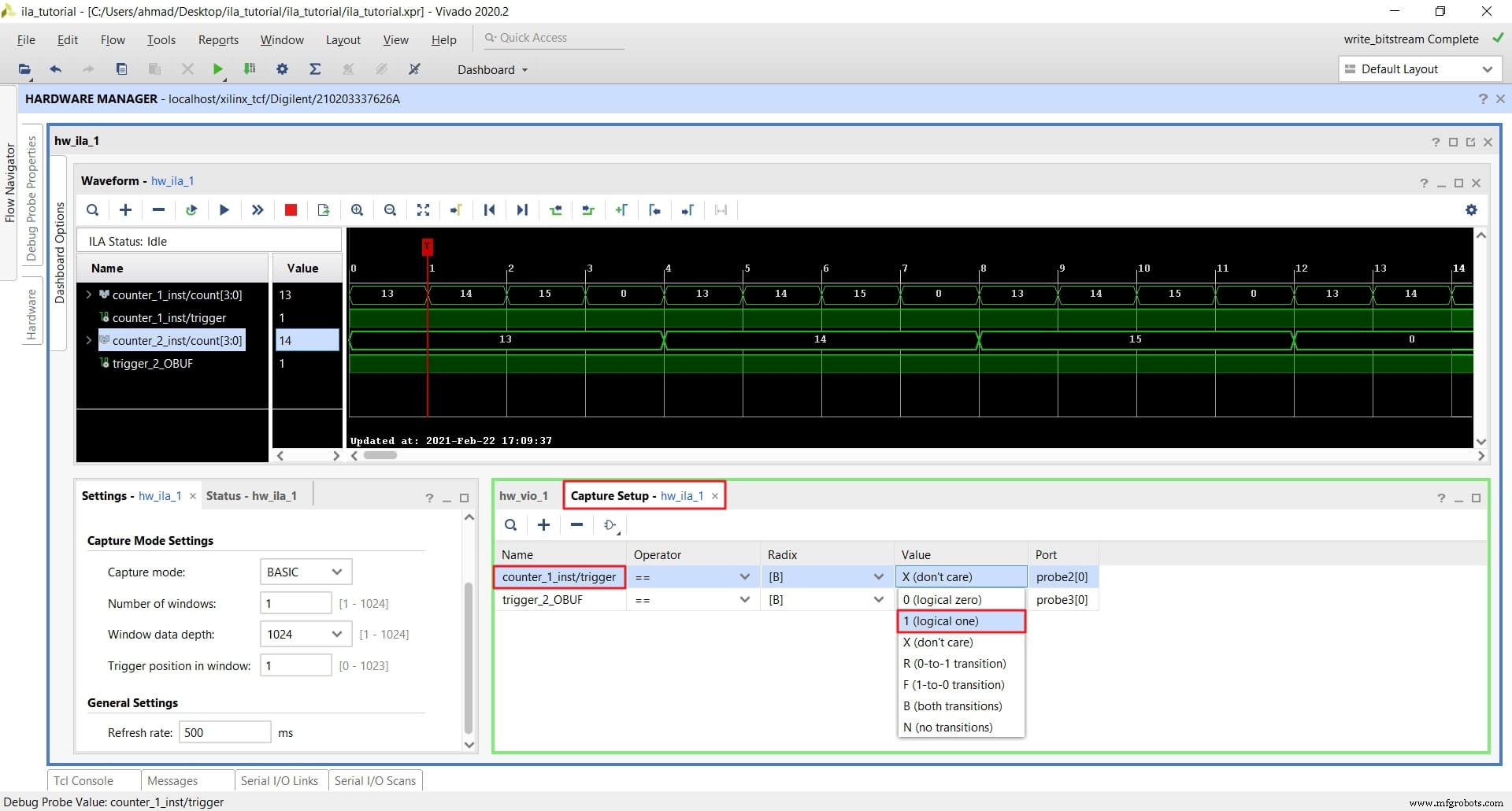

- Configure counter_1_inst/trigger to the condition equal (==) and 1 (logical one) :

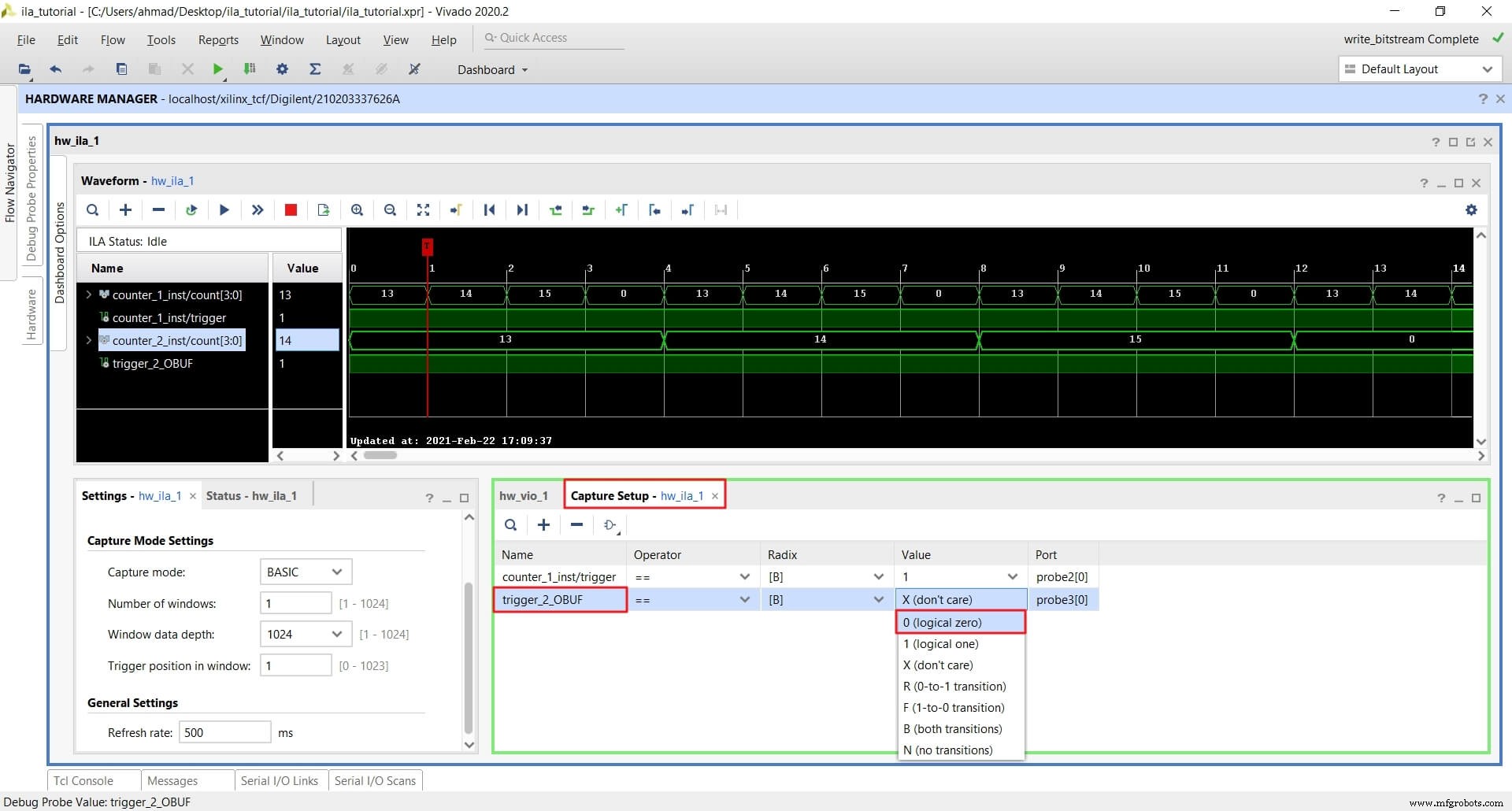

- Configure trigger_2_OBUF to the condition equal (==) and 0 (logical zero) :

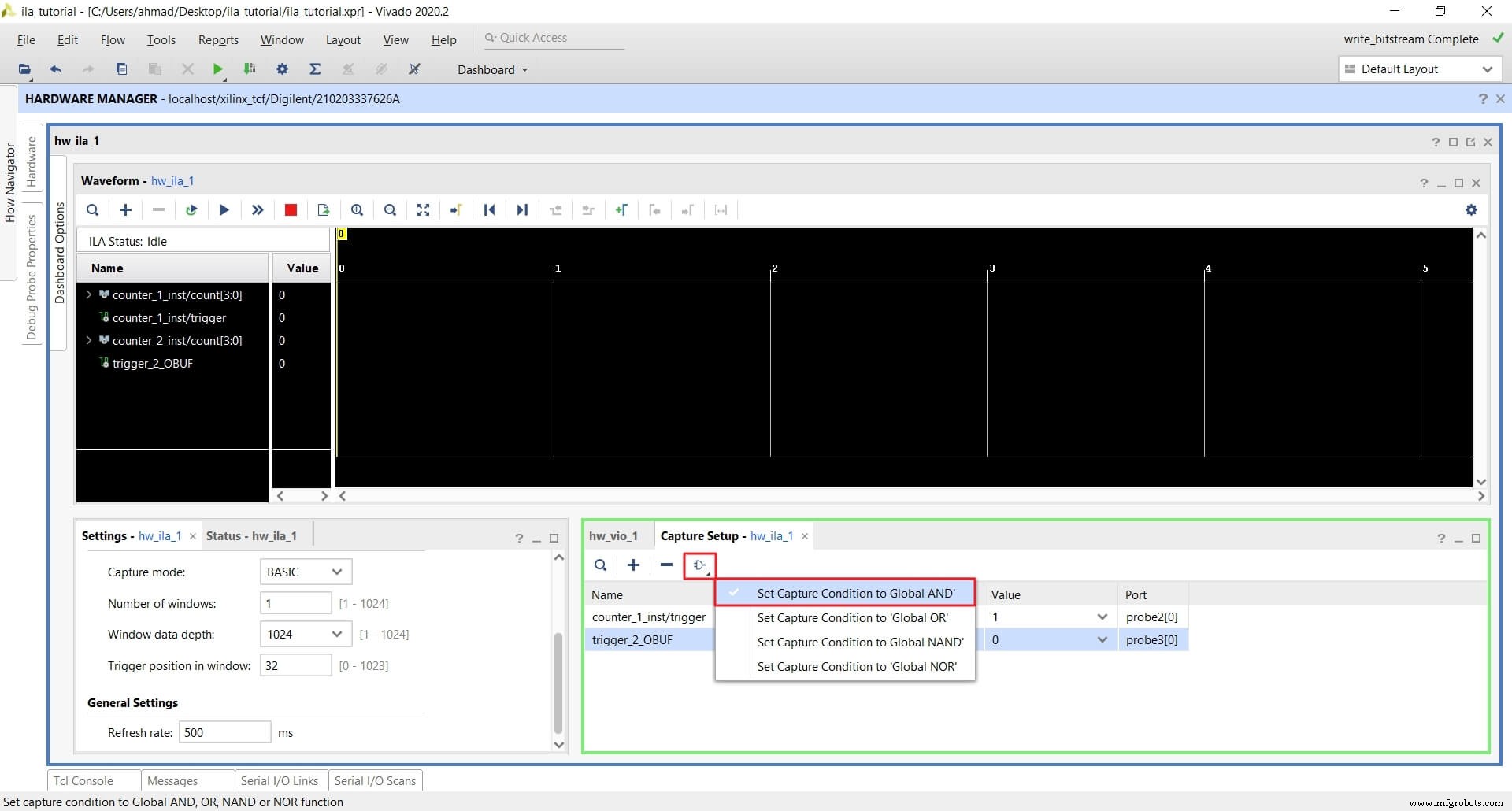

- Change the Capture Condition to Global AND :

- Click on the Run trigger button and then change reset to 0 from vio_reset :

As we can see from the image below, the waveform has only recorded data when counter_1_inst’s count signal is 13, 14, 15, or 0. Any other counts are filtered out because counter_1_inst/trigger is high on these counts only.

Conclusion

In this tutorial, we learned about ILA and VIO and different use-cases for them. ILA and VIO are excellent options for on-chip debugging. They are free, easy to use, flexible, scalable, and simple yet offer advanced features. The use of multiple triggers and Capture mode helps you achieve a complex debugging scheme.

VHDL

- Tutorial - Schreiben von kombinatorischem und sequentiellem Code

- Zu Cloud Infinity und darüber hinaus

- C# Grundlegende Ein- und Ausgabe

- C++ Basic Input/Output

- C Eingang Ausgang (E/A)

- Python-Eingabe, -Ausgabe und -Import

- Java Basic Input und Output

- D Verriegelung

- C - Eingang und Ausgang

- RightHand Robotics und Element Logic bringen eine integrierte Roboterlösung für die Stückauswahl auf den Markt