Kostengünstiger Crossover-Prozessor unterstützt Endpunktinferenz

BRISTOL, Großbritannien – XMOS hat seinen Xcore-Prozessorkern für maschinelles Lernen angepasst und einen Crossover-Prozessor für AIoT-Anwendungen geschaffen. Die Xcore.ai wird ab $1 erhältlich sein.

Xcore.ai, die dritte Produktgeneration, die auf dem proprietären Kerndesign des Unternehmens basiert, wurde für Echtzeit-KI-Inferenz und -Entscheidungsfindung in Endgeräten entwickelt und kann auch Signalverarbeitungs-, Steuerungs- und Kommunikationsfunktionen verarbeiten.

Neu bei diesem Chip der dritten Generation ist eine Vektor-Pipeline-Funktion für Anwendungen des maschinellen Lernens. Es ist der einzige Crossover-Prozessor seiner Art, der binarisierte (1-Bit) neuronale Netze unterstützt, die für KI mit extrem geringem Stromverbrauch in Endpunktanwendungen immer wichtiger werden, da sie eine größenordnungsmäßige Verbesserung der Leistung und der Speicherdichte bieten für eine bescheidene Verringerung der Genauigkeit (die Xcore.ai unterstützt auch 32-Bit-, 16-Bit- und 8-Bit-Zahlen).

Der Xcore.ai schließt sich einer neuen Klasse von KI-fähigen System-on-Chips für Endpunktanwendungen an, dem Crossover-Prozessor (Bild:XMOS)

Xcore.ai schließt sich einer aufstrebenden Klasse von Endpunktprozessoren mit KI-Fähigkeit an, dem Crossover-Prozessor. Dieser von NXP geprägte Begriff beschreibt eine wichtige neue Kategorie von Geräten mit der Leistung eines Anwendungsprozessors in Kombination mit der Benutzerfreundlichkeit, dem geringen Stromverbrauch und dem Echtzeitbetrieb eines Mikrocontrollers.

„Wenn Sie mit Kunden über ‚Mikrocontroller‘ sprechen, denken sie an Cortex-M0-, M3- oder M4-Geräte, die 75 Cent oder weniger kosten, bei relativ geringer Leistung, etwa 100 MIPS. Dann könnten „SoCs“ etwas mit Quad-A53-Kernen sein, die mit einem Gigahertz laufen. Es gibt eine große Lücke für Dinge in der Mitte, wie Prozessoren für Sprache, was ein besonders schwieriges mathematisches Problem ist und Tausende von MIPS erfordert. Es gibt also diese große Lücke mit einem wirklich großen und wichtigen Anwendungsbereich, der mittendrin sitzt und einen Namen verdient“, sagte Mark Lippett, CEO von XMOS, in einem exklusiven Interview mit EETimes.

Sprachschnittstellen

Das zuvor angekündigte Produkt der zweiten Generation des Unternehmens, der XVF3510, wurde im Juli 2019 als ASIC für Sprachschnittstellen auf den Markt gebracht, aber das Silizium unter der Haube basiert auch auf dem proprietären Xcore-Design des Unternehmens, das mit Firmware geliefert wird. Referenzdesigns für Fernfeld-Sprachlösungen auf Basis des XVF3510 sind für Amazons Alexa Voice Service qualifiziert.

Angesichts der Geschichte von XMOS im Sprachsektor ist es nicht verwunderlich, dass der Xcore.ai-Chip zunächst auf Sprachschnittstellenanwendungen ausgerichtet ist, die KI für die Schlüsselworterkennung oder Wörterbuchfunktionen benötigen.

„Lasst uns ganz klar sagen, Sprache ist die wichtigste KI-Arbeitslast am Endpunkt und wird es wahrscheinlich noch lange bleiben. Aber um die Sprachschnittstellen zu verbessern, werden Sie feststellen, dass die Geräte multimodaler werden“, sagte Lippett und beschrieb einen Trend zur Verwendung verschiedener Arten von Sensoren, um Anwendungen kontextbewusster zu machen, sei es bei der Erkennung der Anwesenheit einer Person oder der Erkennung des Ortes sie sprechen von.

Mark Lippett (Bild:XMOS)

„Es gibt viele Möglichkeiten, die Benutzererfahrung zu verbessern, indem man nicht nur Audio anhört, sondern mehr als nur das tut“, sagte er.

Viele Anwendungen für KI in IoT-Geräten hängen von einer Kombination aus Datenschutz, Sicherheit und Schutz ab, die eine Verarbeitung am Endpunkt erfordert. Lippett beschrieb Sicherheitsfeatures an Geräten, die den Backofen per Sprache und Radar ausschalten, wenn sich beispielsweise nur Kinder in der Küche aufhalten.

Xcore.ai wird daher mit Bibliotheken auf den Markt kommen, die für die Erstellung von Sprachschnittstellen bereitgestellt werden, aber Lippett sagte, dass es über freie Kapazitäten für Kunden verfügt, um ihre eigenen Systeme zu bauen. Für die Kameraeingabe ist eine MIPI-Schnittstelle enthalten.

Xcore-Architektur

Der Xcore.ai-Chip liefert bis zu 3200 MIPS, 51,2 GMACCs und 1600 MFLOPS. Es verfügt über 1 MByte eingebetteten SRAM sowie eine stromsparende DDR-Schnittstelle zur Erweiterung.

Im Vergleich zu einem Cortex-M7-Gerät, das ungefähr den gleichen Integrationsgrad wie Xcore.ai bietet und mit einer ähnlichen Betriebsfrequenz läuft, geben die eigenen Zahlen von XMOS ihren Anteil an der 32-fachen KI-Verarbeitungsleistung und der 15-fachen DSP-Leistung an.

„In der Endpoint-Welt muss das Preis-Leistungs-Verhältnis stimmen, es macht keinen Sinn, über das eine ohne das andere zu sprechen“, sagte Lippett. „Wir waren sehr preisaggressiv, wir können für diesen Teil [in Volumen] auf 1 US-Dollar sinken. Im Großen und Ganzen sind wir ungefähr halb so teuer [des vergleichbaren Cortex-M7-Geräts] und wir blasen es in Bezug auf die Leistung aus dem Wasser.“

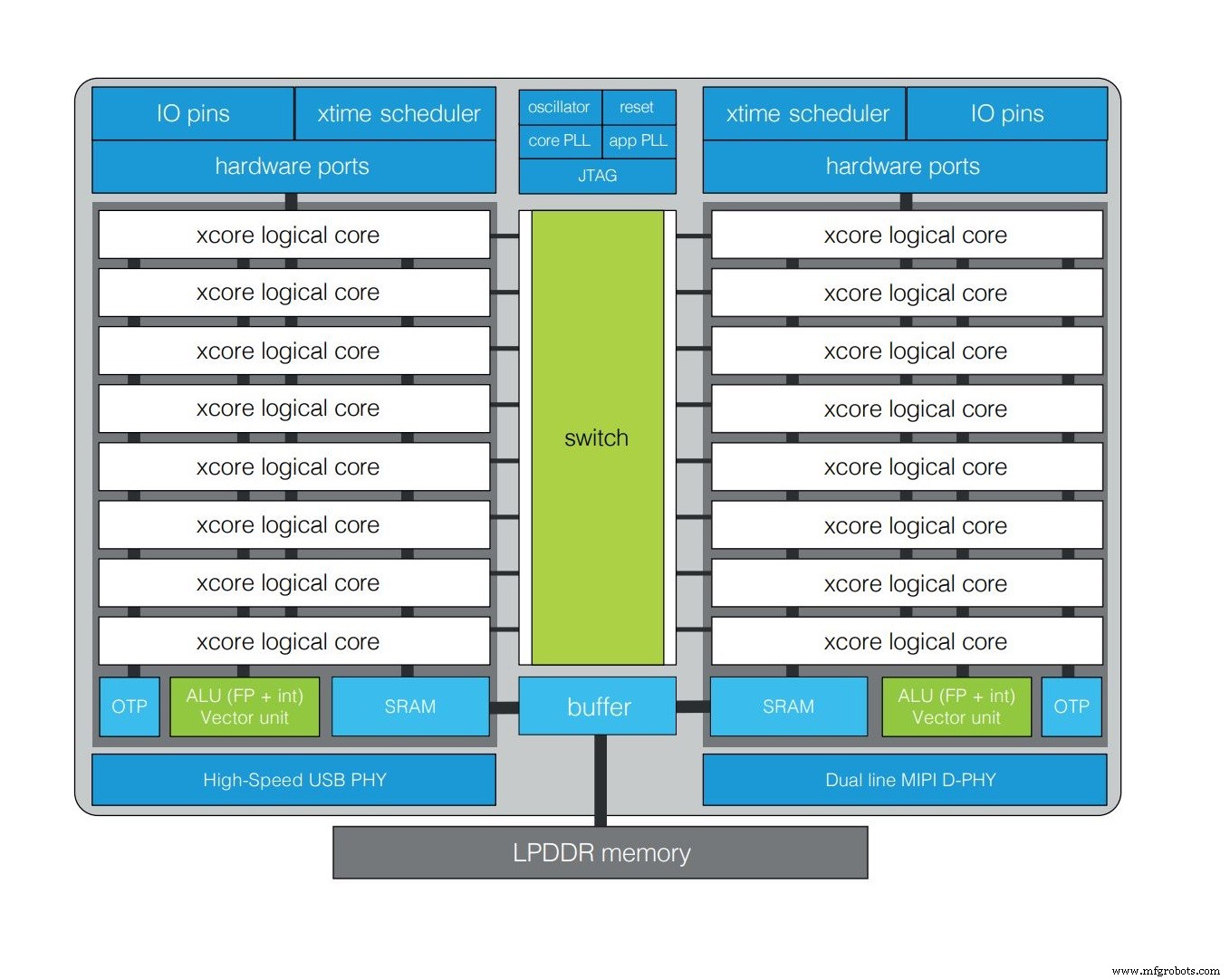

Der Xcore basiert auf logischen Kernen, die in Kacheln mit Speicher angeordnet sind,

ALUs und Vektoreinheiten (Bild:XMOS)

Xcore.ai basiert auf der proprietären Xcore-Architektur von XMOS. Der Xcore selbst basiert auf Bausteinen, die als logische Kerne bezeichnet werden und entweder für I/O, DSP, Steuerfunktionen oder KI-Beschleunigung verwendet werden können. Es gibt acht logische Kerne auf jeder Kachel, mit zwei Kacheln in jedem Xcore.ai-Chip, und Designer können wählen, wie viele Kerne jeder Funktion zugewiesen werden. Jede Kachel enthält außerdem Speicher, ALUs und eine Vektoreinheit, auf die die logischen Kerne gemeinsam zugreifen.

„Entscheidend ist, dass sie [den Zugang] auf sehr vorhersehbare Weise teilen“, sagte Lippett. „Das ist das Besondere am Xcore. Ursprünglich wollten wir Software-Ingenieuren I/O-Flexibilität bieten, und Hardware ist nicht sehr tolerant, wenn Sie Fristen verpassen. Xcore ist also Multi-Core, nicht weil wir Workloads auslagern und Dinge sehr schnell erledigen wollen – das können wir –, sondern wirklich Multi-Core, weil wir bestimmten Teilen der Anwendung ihre eigenen Ressourcen geben wollen, damit wenn es wird gebraucht, es ist fertig. Es wurde von Grund auf entwickelt, um diese Art von Timing-Genauigkeit zu liefern.“

Die Abbildung verschiedener Funktionen (I/O, DSP, Steuerung, KI) auf die logischen Kerne in der Firmware ermöglicht die Erstellung eines „virtuellen SoC“, der vollständig in Software geschrieben ist. Im folgenden Beispiel führt ein Kern Aufgaben aus, die normalerweise in Hardware ausgeführt werden würden, wie z. B. I 2 S, I 2 C- und LED-Treiber und einige Kerne verarbeiten das neuronale Netzwerk, während andere Aufgaben erledigen, die normalerweise in Software erledigt werden. All dies in Software zu definieren ist schneller, um den vorübergehenden Anforderungen von IoT-Geräten gerecht zu werden. Auch die Entwicklung sei billiger, so Lippett, so dass Unternehmen auch in kleineren Marktsegmenten wirtschaftliche Lösungen entwickeln könnten.

Eine Beispielanwendung, die einem Xcore.ai-Gerät zugeordnet ist (Bild:XMOS)

„Wir sehen die Marktentwicklung so, dass der Markt vielfältigere Funktionen verlangt und Unternehmen schneller reagieren müssen“, sagte Lippett. „Es ist sehr schwierig, eine zweijährige Wette auf das IoT zu platzieren, ohne eine sehr generische Plattform aufzubauen, die [eventuell] für kein Segment gut genug ist. [Mit Xcore.ai] ist es viel einfacher, Geräte viel schneller und mit weniger Investitionen auf den Markt zu bringen und effektiv kleinere Wetten auf kleinere Märkte zu platzieren und diese Märkte wirtschaftlich zu machen.“

Wie wird XMOS gegen die großen Mikrocontroller-Hersteller konkurrieren, die in diesen Bereich der Crossover-Prozessoren eintreten?

„Nicht durch den Bau von ARM-basierten SoCs! Weil sie das wirklich gut machen“, sagte Lippett. „Die einzige Möglichkeit, gegen diese Jungs anzutreten, besteht darin, einen architektonischen Vorsprung zu haben. Das sind die intrinsischen Fähigkeiten des Xcore in Bezug auf die Leistung, aber auch die Flexibilität.“

Eingebettet

- Renesas hebt Endpunktintelligenz auf der Embedded World 2019 hervor

- MCUs zielen auf sichere IoT-Endpunkt- und Edge-Designs ab

- Vorzertifizierte drahtlose Prozessormodule verfügen über Bluetooth-Mesh-Konnektivität

- Die Verwendung mehrerer Inferenzchips erfordert eine sorgfältige Planung

- PMIC vereinfacht Multi-Rail-Prozessordesigns

- Kleiner haptischer IC unterstützt stromsparende Wearables

- Multicore-Prozessor integriert neuronale Verarbeitungseinheit

- 60-GHz-Radar-on-Chip unterstützt die Anforderungen der Automobilindustrie

- Power Management IC unterstützt die Anwendungsprozessorfamilie

- Spezialisierte Prozessoren beschleunigen Endpoint-KI-Workloads