Prozessor-in-Memory-Chip beschleunigt KI-Berechnungen

Imec und GlobalFoundries haben einen Prozessor-in-Memory-Chip vorgestellt, der eine Energieeffizienz von bis zu 2900 TOPS/W erreichen kann, etwa zwei Größenordnungen über den heutigen kommerziellen Prozessor-in-Memory-Chips. Der Chip verwendet eine etablierte Idee, Analog Computing, implementiert in SRAM in der 22-nm-Full-depleted Silicon-on-Insulator (FD-SOI)-Prozesstechnologie von GlobalFoundries. Das analoge In-Memory-Computing (AiMC) von Imec wird GlobalFoundries-Kunden als Funktion zur Verfügung stehen, die auf der 22FDX-Plattform des Unternehmens implementiert werden kann.

Der AnIA-Testchip von Imec, der hier auf der zur Messung und Charakterisierung verwendeten Leiterplatte montiert ist, kann bis zu 2900 TOPS/W erreichen (Bild:Imec)

Analoges Rechnen

Analog Computing oder Processor-in-Memory ist eine etablierte Technik, die bereits in kommerziellen KI-Beschleunigerchips der Startups Mythic, Syntiant, Gyrfalcon und anderen verwendet wird.

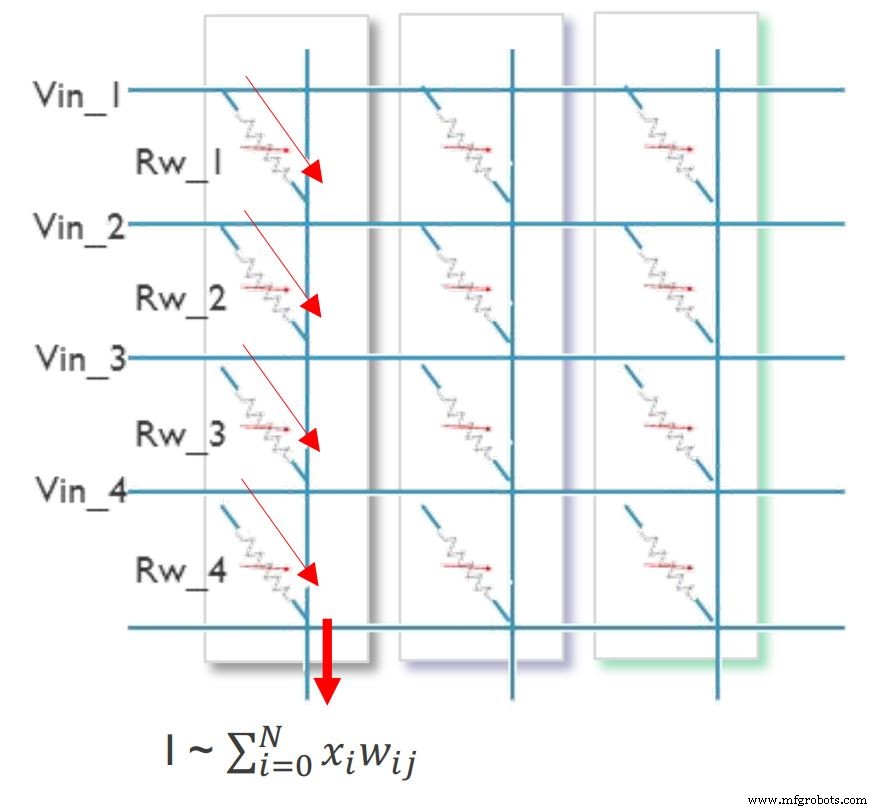

Da ein neuronales Netzwerkmodell Dutzende oder Hunderte Millionen Gewichte aufweisen kann, ist das Hin- und Hersenden von Daten zwischen dem Speicher und dem Prozessor ineffizient. Analog Computing verwendet ein Speicherarray, um die Gewichte zu speichern und auch Multiply-Accumulate-(MAC)-Operationen durchzuführen, sodass keine Übertragung vom Speicher zum Prozessor erforderlich ist. Die Leitfähigkeit jedes Memristorelements (vielleicht eine ReRAM-Zelle) ist auf ein analoges Niveau programmiert, das proportional zum erforderlichen Gewicht ist.

Das Anlegen einer Spannung proportional zur Eingangsaktivierung (über Digital-Analog-Umwandlung — links im Diagramm unten) bedeutet, dass der Strom durch jedes Element proportional zum Produkt aus Aktivierung und Gewicht ist. Der Strom durch jede vertikale Bitleitung (vertikale Leitungen im Diagramm unten) ist die Summe dieser Aktivierungsgewichtsprodukte, die durch einen Analog-Digital-Umsetzer gespeist werden können. Diese Summe der Aktivierungsgewichtsprodukte ist entscheidend für die Berechnung von neuronalen Netzwerkalgorithmen.

Analog Computing verwendet ein Array von Memristorzellen, um die Matrixvektormultiplikation zu berechnen, ohne dass Daten zwischen Speicher und Prozessor gesendet werden müssen (Bild:Imec)

„In der Praxis sind neben ReRAM viele Optionen möglich – wir können MRAM, Flash, DRAM verwenden … Ziel dieses Programms ist es, zu verstehen, welche für die Anwendung am besten geeignet ist, und die Optionen für jede Anwendungsdomäne zu optimieren“, erklärt Diederik Verkest, Programm Direktor für maschinelles Lernen bei Imec.

Testchip

Imec hat einen Testchip namens Analog Inference Accelerator (AnIA) gebaut, der auf dem 22-nm-FD-SOI-Prozess von GlobalFoundries basiert. Das 512k-Array von SRAM-Zellen von AnIA plus die digitale Infrastruktur mit 1024 DACs und 512 ADCs benötigt 4 mm 2 . Es kann etwa eine halbe Million leisten

Ioannis Papistas (Bild:Imec)

Berechnungen pro Operationszyklus basierend auf 6-Bit-Eingangsaktivierungen (plus Vorzeichenbit), ternären Gewichten (-1, 0, +1) und 6-Bit-Ausgängen.

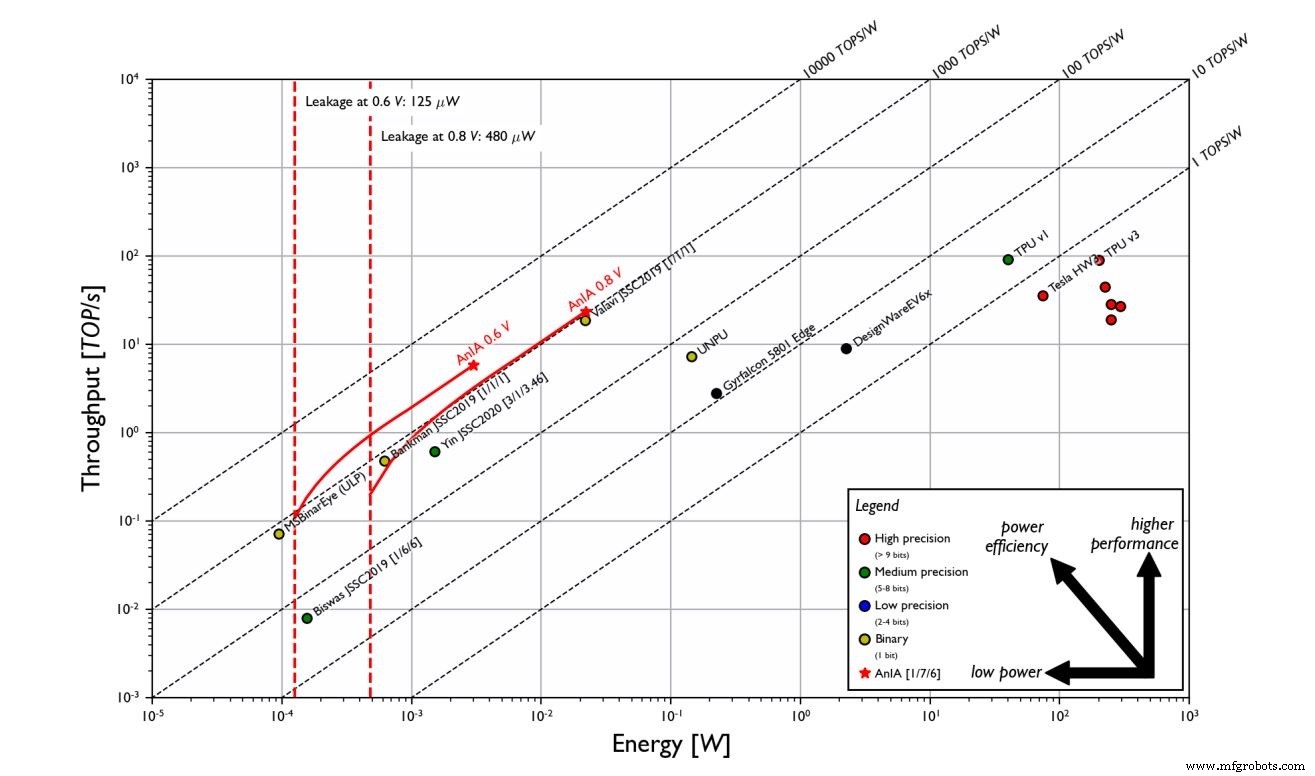

„Wir sind in der Lage, die Matrixvektor-Multiplikationsausgabe bei verschiedenen Versorgungsspannungen, 0,8 und 0,6 V, zu produzieren“, sagte Ioannis Papistas von Imecs Machine Learning Group. „Der Betrieb bei niedrigeren Versorgungsspannungen, ohne die Genauigkeit des Betriebs zu beeinträchtigen, kann den Stromverbrauch des Betriebs erheblich reduzieren, was besonders wichtig für die Inferenz in energiebeschränkten Systemen ist. Dies ist ein wichtiges Merkmal unseres Designs, das durch den 22FDX-Prozess ermöglicht wird und wettbewerbsfähige Inferenz am Edge ermöglicht.“

Imec zeigte Genauigkeitsergebnisse für die Objekterkennungsinferenz auf dem CIFAR 10-Datensatz, die im Vergleich zu einer ähnlich quantisierten Basislinie nur um einen Prozentpunkt abnahmen. Bei einer Versorgungsspannung von 0,8 V liegt die Energieeffizienz von AnIA zwischen 1050 und 1500 TOPS/W bei 23,5 TOPS. Bei einer Versorgungsspannung von 0,6 V erreichte AnIA 5,8 TOPS bei etwa 1800-2900 TOPS/W.

Energieeffizienz verschiedener KI-Beschleuniger im Vergleich zu Imecs AnIA-Testchip (Zum Vergrößern anklicken) (Bild:Imec)

Mainstream-Innovation

„Die Innovation [Imec präsentiert] wird Mainstream werden“, sagte Hiren Majmudar, VP und GM der Computing Business Unit von GlobalFoundries. „Wir sehen Partner, Kunden von GlobalFoundries, die sich in der Postproduktionsphase mit validiertem Silizium befinden … wir erwarten, dass analoges, computerbasiertes Silizium gegen Ende dieses Jahres oder Anfang nächsten Jahres in Produktion gehen wird. In Bezug auf die Massenmarktimplementierung gehen wir davon aus, dass analoge Computing spätestens 2022 in den Massenmarkt eintreten werden. Aber es könnte möglicherweise früher passieren.“

Diederik Verkest (Bild:Imec)

GlobalFoundries arbeitet daran, die AiMC-Technologie von Imec als eine Funktion aufzunehmen, die auf der 22 FDX-Plattform implementiert werden kann, um energieeffiziente KI-Beschleuniger zu ermöglichen. Der FD-SOI-Prozess ist auf einen geringen Stromverbrauch ausgelegt und kann bis zu 0,5 V mit 1 Pico Ampere pro Mikrometer betrieben werden, um einen extrem niedrigen Standby-Leckstrom zu erzielen. 22FDX mit der neuen AiMC-Funktion wird in der 300-mm-Produktionslinie von GlobalFoundries in Fab 1 in Dresden, Deutschland, entwickelt.

Was Imec betrifft, wird das maschinelle Lernprogramm fortgesetzt. Das Ziel der Gruppe ist es, 10.000 TOPS/W (10 TOPS unter 100mW) für immer aktive intelligente Sensoren und Verbraucher-Wearables zu erreichen, sagte Verkest.

„In unserem ML-Programm bestehen unsere nächsten Schritte darin, die Größe dieser Rechenzellen zu reduzieren und neue Speichergeräte als Implementierung der nächsten Generation für dieses Prinzip zu betrachten“, sagte er.

>> Dieser Artikel wurde ursprünglich veröffentlicht am unsere Schwesterseite EE Times.

Eingebettet

- Einführung in analoge integrierte Schaltungen

- Computerschaltungen

- Entwerfen mit Bluetooth Mesh:Chip oder Modul?

- KI-Chiparchitektur zielt auf die Grafikverarbeitung ab

- Kleines Bluetooth 5.0-Modul integriert Chipantenne

- Forscher bauen winzige Authentifizierungs-ID-Tags

- Debüts des bildgebenden Radarprozessors für die Automobilindustrie mit 30 fps

- Low-Power-Radarchip verwendet neuronale Spiking-Netzwerke

- Smart Sensor Board beschleunigt die Entwicklung von Edge-KI

- Dauerhafte UAV-Geschwindigkeiten bis zur Produktion