Informationen zur DSP-Aktivierung mit der i.MX RT500 Crossover-MCU von NXP

Erfahren Sie mehr über Multithread-Programme, die Entwicklung von Anwendungen mit dem Echtzeitbetriebssystem XOS, die gemeinsame Nutzung von Ressourcen mit Semaphoren und die i.MX RT500-Familie von NXP der Mikrocontroller helfen Ingenieuren bei der Entwicklung DSP-fähiger intelligenter Geräte.

Moderne intelligente Verbrauchergeräte erfordern Komponenten, die große Datenmengen verarbeiten können, um die Anforderungen verschiedener Sicherheits- und Signalverarbeitungsanwendungen zu erfüllen. Diese Komponenten (einschließlich Mikrocontroller) müssen in der Lage sein, diese Daten schnell und effizient zu verarbeiten, was hochoptimierte digitale Signalprozessoren erfordert.

In diesem Artikel werden einige Funktionen des Cadence® Tensilica® Fusion F1 Audioprozessors vorgestellt, einem designierten Coprozessor, der die Haupt-CPU der i.MX RT500 MCU bei der Durchführung von Signalverarbeitungsberechnungen unterstützt.

Kernkonzepte von Multithread-Programmen

Auf den ersten Blick erweckt moderne Verarbeitungshardware die Illusion, dass sie viele Threads gleichzeitig ausführt. In Wirklichkeit kümmert sich ein einzelner CPU-Kern um jeweils einen einzelnen Thread. Wenn die Anzahl der Threads die Anzahl der verfügbaren CPU-Kerne überschreitet, wird ein Betriebssystem benötigt, um die Threads zu planen.

Das Betriebssystem muss alle gestarteten Threads und deren Status verfolgen und weist jedem Thread CPU-Zeitschlitze zu, damit verschiedene Anwendungen effizient und scheinbar parallel ausgeführt werden können.

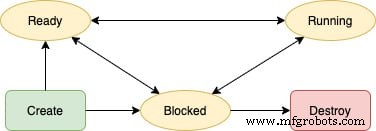

Abbildung 1. Die verschiedenen Zustände eines Threads

Der Betriebssystem-Scheduler verwaltet eine Warteschlange für Threads, die zur Ausführung bereit sind, eine Warteschlange zum Blockieren von Threads, und er muss Informationen über die aktuell laufenden Threads speichern, um eine gerechte Verteilung der CPU-Zeit zu erreichen:

- Threads in der Ready-Warteschlange warten derzeit darauf, dass das Betriebssystem sie auf der CPU plant. Normalerweise kennt der OS-Scheduler verschiedene Prioritätsstufen, die er bei der Auswahl des nächsten Threads zur Ausführung auf der CPU berücksichtigt.

- Blockierende Threads warten darauf, dass ein externes Ereignis eintritt, beispielsweise ein Pin-Interrupt oder eine Dateioperation. Die Planung dieser Threads würde bedeuten, dass die CPU Rechenleistung verschwendet, während sie darauf wartet, dass ein externer Vorgang abgeschlossen ist. Sobald die Blockierungsoperation abgeschlossen ist, kehrt der zugehörige wartende Thread zum Ende der Bereitschaftswarteschlange zurück.

- Die derzeit ausgeführten Threads führen möglicherweise einen Blockierungsvorgang durch, oder das Betriebssystem plant einen anderen Thread gemäß seiner Planungsstrategie. In diesem Fall verschiebt der Scheduler den aktuell laufenden Thread in die Liste der blockierten Threads bzw. an das Ende der Bereit-Warteschlange.

OS-Entwickler können je nach den genauen Anforderungen eine oder viele verschiedene Scheduling-Strategien implementieren. Neben dem Scheduling sind Synchronisation und Kommunikation zwischen verschiedenen Threads weitere wesentliche Aspekte von Multithread-Systemen.

Bedingungen und Ereignisse in XOS

Bedingungen innerhalb des XOS RTOS (Echtzeitbetriebssystem) ermöglichen es Entwicklern, einen Thread anzuweisen, zu blockieren, bis eine bestimmte Bedingung wahr wird. Das System wertet jede Bedingung anhand einer von den Anwendungsentwicklern definierten Bedingungsfunktion aus. XOS führt eine Auswertung immer dann durch, wenn ein anderer Thread das Bedingungsobjekt signalisiert oder wenn ein Interrupt-Handler einen auslöst.

Ereignisse innerhalb von XOS stellen andererseits eine Gruppe von Bits dar, die Entwickler verwenden können, um verschiedene Threads oder Threads und Interrupt-Handler zu synchronisieren. XOS ermöglicht es mehreren Threads, auf Ereignisse zu warten und diese gleichzeitig zu signalisieren.

Unterbrechungen in XOS

XOS bietet umfangreiche Funktionen zur Behandlung von Interrupts und Ausnahmen, die während der Laufzeit auftreten. Die Interrupt-Mechanismen in XOS bieten Programmierern die Flexibilität, benutzerdefinierte Handler zu installieren und gleichzeitig sicherzustellen, dass das Dispatching von Interrupts innerhalb des Systems so schnell wie möglich funktioniert. Das XOS unterstützt auch die Behandlung von verschachtelten Interrupts, was bedeutet, dass das Betriebssystem den aktuellen Interrupt-Handler anhält, wenn ein Interrupt mit höherer Priorität auftritt. Sobald das System die Verarbeitung des Interrupts mit hoher Priorität abgeschlossen hat, nimmt es automatisch die Verarbeitung der Interrupts mit niedriger Priorität wieder auf.

Threads können auch zeitbezogene Dienste wie zeitgesteuerte Verzögerungen und periodische Timer-Rückrufe in XOS haben. Der DSP-Coprozessor unterstützt bis zu drei interne Timer, die die Programmierer nach Bedarf konfigurieren können.

Semaphoren verstehen

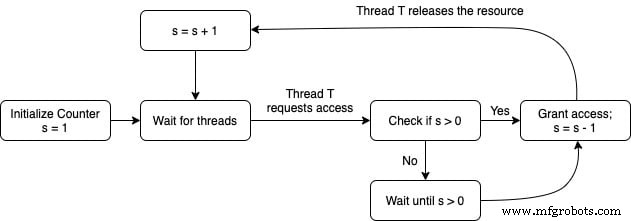

Bei der Multithread-Programmierung bieten Semaphoren ein Mittel zum Steuern und Koordinieren des Zugriffs auf eine gemeinsam genutzte Ressource. Semaphoren helfen, kritische Abschnittsprobleme in nebenläufigen Systemen zu vermeiden, indem sie verschiedene Threads synchronisieren. Semaphoren sind ein einfaches Konstrukt, das einen internen Zähler mit einem vorgegebenen Startwert verfolgt, den die Programmierer im Quellcode frei setzen können. Es gibt verschiedene Implementierungen, aber der Zähler gibt normalerweise an, wie viele Threads noch auf eine gemeinsam genutzte Ressource zugreifen können.

Immer wenn ein Thread auf die gemeinsam genutzte Ressource zugreifen möchte, überprüft das System, ob der zugehörige Zähler größer als Null ist. Wenn dies der Fall ist, gewährt das Betriebssystem Zugriff auf die Ressource und verringert den internen Zähler des Semaphors. Wenn ein Thread zum gegebenen Zeitpunkt nicht auf die Ressource zugreifen darf, wechselt der Thread in einen blockierenden Zustand und wartet, bis er Zugriff auf die Ressource erhält. Immer wenn ein Thread die Ressource freigibt, erhöht das Betriebssystem den Semaphor-Zähler und ein neuer Thread kann in den kritischen Abschnitt eintreten.

Abbildung 2. Ein Flussdiagramm zur Veranschaulichung der Funktionsweise von Semaphoren

Ein Überblick über die i.MX RT500 MCU und den DSP

i.MX RT500 ist eine Familie von Dual-Core-Mikrocontrollern basierend auf einem leistungsstarken Arm® Cortex®-M33-Kern mit einer Taktrate von bis zu 275 MHz und Unterstützung für bis zu fünf Megabyte SRAM.

Die i.MX RT500 MCU bietet Schutzfunktionen wie Arm TrustZone und eine integrierte Speicherschutzeinheit (MPU) mit Unterstützung für bis zu acht Regionen. Der CASPER Krypto-Coprozessor ermöglicht die Hardwarebeschleunigung, um verschiedene Funktionen zu steigern, die für asymmetrische kryptographische Algorithmen erforderlich sind. Dank einer Reihe von Energiesparfunktionen können Entwickler den Stromverbrauch des i.MX RT500 an ihre Anwendungsanforderungen anpassen.

Verschiedene dedizierte Hardwarebeschleuniger unterstützen die Haupt-CPU bei der Durchführung von DSP-Berechnungen. Ein zusätzlicher Cadence® Tensilica® Fusion F1 Audio-DSP, eine 2D-GPU mit Vektorgrafikbeschleunigung und verschiedene Display-Schnittstellen machen den i.MX RT500 für verschiedene sichere und stromsparende Embedded-Anwendungen geeignet. Typische Anwendungsfälle sind HMI-Anwendungen, IoT-Geräte, Hearables, sprachaktivierte persönliche Assistenten und andere ähnliche Verbrauchergeräte.

Ein Blick auf den Audio-DSP

Der i.MX RT500 enthält verschiedene spezielle Co-Prozessoren, die dazu beitragen können, die CPU-Kerne zu entlasten, indem sie mathematisch komplexe Berechnungen durchführen, während die Prozessorkerne für andere Aufgaben frei bleiben. Ein solcher dedizierter Prozessor ist der Fusion DSP, der einen Cadence® Tensilica® Fusion F1 Audioprozessor und eine Hardware-Gleitkommaeinheit umfasst.

Diese Audioverarbeitungs-Engine läuft mit Frequenzen von bis zu 200 MHz und ist so konzipiert, dass sie immer eingeschaltete sprachgesteuerte Geräte wie virtuelle Assistenten ermöglicht. Außerdem kombiniert der Audio-DSP verschiedene Module für typische Vor- und Nachbearbeitungsaufgaben unter Verwendung zahlreicher Audio-Codecs.

Die DSP- und Haupt-CPU-Kerne können auf verschiedene Weise miteinander kommunizieren. Entwickler können den gesamten SRAM verwenden, wenn sie mit dem Fusion DSP arbeiten, es sei denn, der RAM ist geschützt und bestimmte Teile sind für den sicheren Zugriff gekennzeichnet.

Programmieren mit DSP im Hinterkopf

Tensilica DSPs unterstützen verschiedene Echtzeit-Betriebssysteme (RTOS), einschließlich FreeRTOS™, Zephyr™, Linux® und XOS. Cadence hat den eingebetteten XOS-Kernel als Referenzdesign mit Blick auf Tensilica-Prozessoren entwickelt.

Zu den leichtgewichtigen XOS-Kernelfunktionen gehören ein Taskplaner, adaptiver Kontextwechsel, Synchronisationsmechanismen, Interrupt- und Ausnahmemanagement sowie das Management kritischer Ressourcen. Der Quellcode des Kernels ist hauptsächlich in Standard-C geschrieben und nicht spezifisch für Xtensa-Prozessoren und DSPs.

Erfüllen der Anforderungen für Smart Consumer-Geräte

Die Crossover-MCUs der i.MX RT500-Familie verfügen über verschiedene Funktionen, die die intelligenten Verbrauchergeräte von morgen inspirieren sollen. Die verschiedenen Co-Prozessoren unterstützen die Hauptverarbeitungskerne der MCU bei der Durchführung mathematisch komplexer Berechnungen für Sicherheits- und Signalverarbeitungsanwendungen. Einer dieser Co-Prozessoren ist der hochoptimierte Cadence® Tensilica® Fusion F1 Audio-DSP, der immer aktive sprachgesteuerte Geräte wie virtuelle Assistenten ermöglicht. Programmierer können XOS und die Xplorer IDE verwenden, um Anwendungen für den dedizierten Cadence-Prozessor zu entwickeln.

Die Anwendungsnotiz AN13159 enthält weitere Details, eine Liste der unterstützten API-Funktionen und Beispiele für Bedingungen und Ereignisse in XOS, und die Website von NXP bietet weitere Informationen zu den Funktionen und Anwendungen des i.MX RT500. Es bietet auch verschiedene Schulungsmaterialien wie Anwendungsnotizen, Videos und On-Demand-Webinare.

Branchenartikel sind eine Inhaltsform, die es Branchenpartnern ermöglicht, nützliche Nachrichten, Nachrichten und Technologien mit All About Circuits-Lesern auf eine Weise zu teilen, für die redaktionelle Inhalte nicht gut geeignet sind. Alle Branchenartikel unterliegen strengen redaktionellen Richtlinien, um den Lesern nützliche Neuigkeiten, technisches Know-how oder Geschichten zu bieten. Die in Branchenartikeln zum Ausdruck gebrachten Standpunkte und Meinungen sind die des Partners und nicht unbedingt die von All About Circuits oder seinen Autoren.

Eingebettet

- C# verwenden

- Hybridgerät vereint DSP- und MCU-Architekturen

- Wenn ein DSP einen Hardwarebeschleuniger schlägt

- Entscheidungen, Entscheidungen:Hardwarebeschleuniger oder DSP?

- Kontaktlose Flüssigkeitsstandmessung mit einem Reflektometer-Chip

- Verwendung von RFID-Tags für die Überwachung der Heimsicherheit

- 4D-Bildgebungsradar-Chipsätze verbessern die Objektidentifikation

- Bluetooth-MCU verbessert die IoT-Sicherheit

- Wireless-MCU verfügt über eine Dual-Core-Architektur

- Richtlinien für die Verwendung von DSP-Handles