Asynchrone Zähler

Im vorherigen Abschnitt haben wir eine Schaltung gesehen, die ein J-K-Flipflop verwendet, das in einer binären Zwei-Bit-Sequenz von 11 bis 10 bis 01 bis 00 rückwärts zählt.

Da wäre es wünschenswert, eine Schaltung zu haben, die vorwärts zählen könnte und nicht nur rückwärts

Da wir wissen, dass binäre Zählsequenzen einem Muster der Oktavfrequenz (Faktor 2) folgen und dass JK-Flip-Flop-Multivibratoren, die für den „Toggle“-Modus eingerichtet sind, diese Art von Frequenzteilung durchführen können, können wir uns eine Schaltung vorstellen bestehend aus mehreren JK-Flip-Flops, die kaskadiert sind, um vier Ausgabebits zu erzeugen.

Das Hauptproblem, mit dem wir konfrontiert sind, ist zu bestimmen, wie diese Flip-Flops miteinander zu verbinden, damit sie zum richtigen Zeitpunkt umschalten, um die richtige Binärsequenz zu erzeugen.

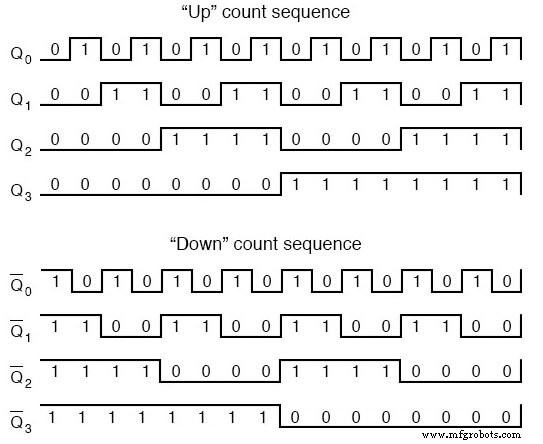

Untersuchen Sie die folgende binäre Zählsequenz und achten Sie dabei auf Muster, die dem „Umschalten“ eines Bits zwischen 0 und 1 vorausgehen:

Beachten Sie, dass jedes Bit in dieser 4-Bit-Sequenz umschaltet, wenn das Bit davor (das Bit mit geringerer Bedeutung oder Platzgewichtung) in eine bestimmte Richtung wechselt:von 1 auf 0.

Kleine Pfeile zeigen die Punkte in der Sequenz an, an denen ein Bit umschaltet, wobei die Spitze des Pfeils, der auf das vorherige Bit zeigt, von einem „high“ (1)-Zustand in einen „low“ (0)-Zustand übergeht:

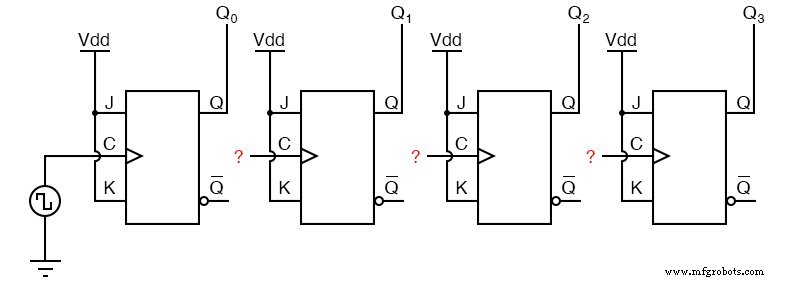

Beginnend mit vier JK-Flip-Flops, die so verbunden sind, dass sie immer im „Toggle“-Modus sind, müssen wir festlegen, wie die Takteingänge so verbunden werden, dass jedes nachfolgende Bit umschaltet, wenn das Bit vor dem Übergang von 1 auf 0.

Die Q-Ausgänge jedes Flip-Flops dienen als die jeweiligen binären Bits der endgültigen Vier-Bit-Zählung:

Wenn wir Flip-Flops mit negativer Flankentriggerung (Blasensymbole an den Takteingängen) verwenden, könnten wir einfach den Takteingang jedes Flip-Flops mit dem Q-Ausgang des Flip-Flops davor verbinden, so dass, wenn das Bit davor es wechselt von einer 1 zu einer 0, die "fallende Flanke" dieses Signals würde das nächste Flip-Flop "takten", um das nächste Bit umzuschalten:

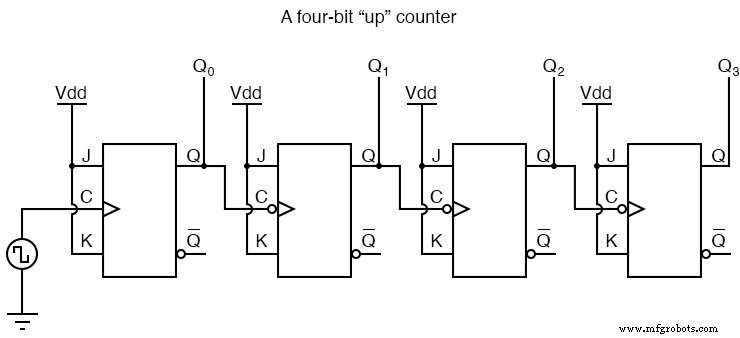

Vier-Bit-Aufwärtszähler

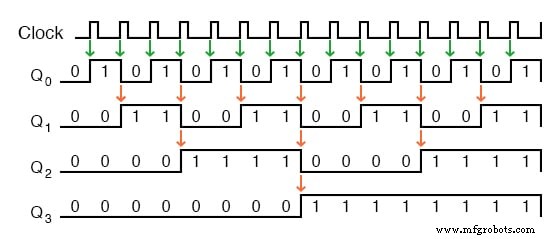

Diese Schaltung würde die folgenden Ausgangswellenformen liefern, wenn sie von einer sich wiederholenden Impulsquelle von einem Oszillator „getaktet“ wird:

Das erste Flip-Flop (das mit dem Q0 Ausgang) hat einen durch positive Flanken getriggerten Takteingang, der mit jeder steigenden Flanke des Taktsignals umschaltet.

Beachten Sie, dass das Taktsignal in diesem Beispiel ein Tastverhältnis von weniger als 50 % hat.

Ich habe das Signal auf diese Weise gezeigt, um zu zeigen, dass das Taktsignal nicht symmetrisch sein muss, um zuverlässige, „saubere“ Ausgangsbits in unserer 4-Bit-Binärsequenz zu erhalten.

In der allerersten Flip-Flop-Schaltung, die in diesem Kapitel gezeigt wird, habe ich das Taktsignal selbst als eines der Ausgangsbits verwendet.

Dies ist jedoch beim Zählerdesign eine schlechte Praxis, da es die Verwendung eines Rechtecksignals mit einem Tastverhältnis von 50% ("high"-Zeit ="low"-Zeit) erfordert, um eine Zählsequenz zu erhalten, bei der jeder einzelne Schritt pausiert für die gleiche Zeit.

Die Verwendung eines J-K-Flipflops für jedes Ausgangsbit befreit uns jedoch von der Notwendigkeit, ein symmetrisches Taktsignal zu haben, was die Verwendung praktisch jeder Vielzahl von High/Low-Wellenformen zum Inkrementieren der Zählsequenz ermöglicht.

Wie durch alle anderen Pfeile im Impulsdiagramm angezeigt, wird jedes nachfolgende Ausgangsbit durch die Aktion des vorhergehenden Bits umgeschaltet, das von „high“ (1) auf „low“ (0) übergeht.

Dies ist das Muster, das notwendig ist, um eine „Aufwärts“-Zählsequenz zu erzeugen.

Eine weniger naheliegende Lösung zum Generieren einer "Aufwärts"-Sequenz unter Verwendung von positiv flankengetriggerten Flip-Flops besteht darin, jedes Flip-Flop mit dem Q’-Ausgang des vorhergehenden Flip-Flops zu „takten“ anstatt mit dem Q-Ausgang.

Da der Q'-Ausgang immer der exakt entgegengesetzte Zustand des Q-Ausgangs an einem JK-Flip-Flop ist (keine ungültigen Zustände bei dieser Art von Flip-Flop), wird ein High-to-Low-Übergang am Q-Ausgang begleitet von ein Low-to-High-Übergang am Q'-Ausgang.

Mit anderen Worten, jedes Mal, wenn der Q-Ausgang eines Flip-Flops von 1 auf 0 übergeht, geht der Q'-Ausgang desselben Flip-Flops von 0 auf 1 über, indem wir den ins Positive gehenden Taktimpuls bereitstellen, den wir zum Umschalten von a . benötigen würden positiv flankengetriggertes Flip-Flop im richtigen Moment:

Alternativer Vier-Bit-Aufwärtszähler

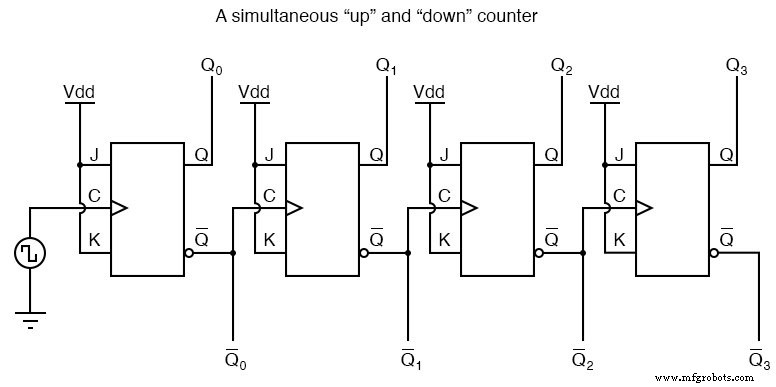

Eine Möglichkeit, die Fähigkeiten einer dieser beiden Zählerschaltungen zu erweitern, besteht darin, die Q’-Ausgänge als einen weiteren Satz von vier Binärbits zu betrachten.

Wenn wir das Pulsdiagramm für eine solche Schaltung untersuchen, sehen wir, dass die Q’-Ausgänge einen down . erzeugen -Zählfolge, während die Q-Ausgänge einen Aufwärts . erzeugen -Zählfolge:

Gleichzeitiger „Auf“- und „Ab“-Zähler

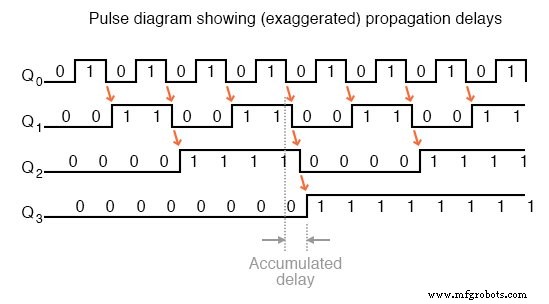

Leider haben alle bisher gezeigten Zählerschaltungen ein gemeinsames Problem:die Welligkeit Wirkung.

Dieser Effekt wird bei bestimmten Typen von Binäraddierer- und Datenumwandlungsschaltungen beobachtet und ist auf kumulative Ausbreitungsverzögerungen zwischen kaskadierten Gattern zurückzuführen.

Wenn der Q-Ausgang eines Flip-Flops von 1 auf 0 übergeht, befiehlt es dem nächsten Flip-Flop, umzuschalten.

Wenn das nächste Flip-Flop-Umschalten ein Übergang von 1 auf 0 ist, wird es auch das nachfolgende Flip-Flop anweisen, umzuschalten, und so weiter.

Da es jedoch immer eine kleine Ausbreitungsverzögerung zwischen dem Befehl zum Umschalten (dem Taktimpuls) und der tatsächlichen Umschaltantwort (Q- und Q'-Ausgänge ändern den Zustand) gibt, schalten alle nachfolgenden Flip-Flops, die umgeschaltet werden sollen, eine Zeit lang um nach das erste Flip-Flop hat umgeschaltet.

Wenn also mehrere Bits in einer binären Zählsequenz umschalten, schalten sie nicht alle gleichzeitig um:

Nachteil der asynchronen Zählerschaltung:Ausbreitungsverzögerung

Wie Sie sehen können, ist die akkumulierte Verzögerungszeit von LSB zu MSB umso schwerwiegender, je mehr Bits mit einem bestimmten Taktimpuls umschalten.

Wenn an einem solchen Übergangspunkt ein Taktimpuls auftritt (z. B. beim Übergang von 0111 zu 1000), "wellen" die Ausgangsbits der Reihe nach von LSB zu MSB, da jedes nachfolgende Bit umschaltet und auch das nächste Bit zum Umschalten befiehlt , mit einer kleinen Ausbreitungsverzögerung zwischen jedem Bitwechsel.

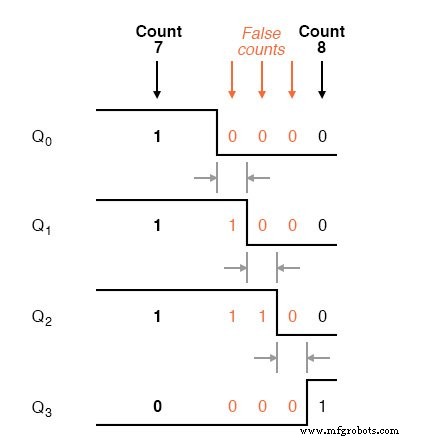

Wenn wir uns diesen Effekt während des Übergangs von 0111 zu 1000 genauer ansehen, können wir sehen, dass es falsch geben wird Ausgangszählungen, die in dem kurzen Zeitraum generiert wurden, in dem der „Wellen“-Effekt auftritt:

Anstatt sauber von einem „0111“-Ausgang zu einem „1000“-Ausgang überzugehen, wird die Zählerschaltung sehr schnell von 0111 auf 0110 auf 0100 auf 0000 auf 1000 oder von 7 auf 6 rippen bis 4 bis 0 und dann zu 8. Dieses Verhalten bringt der Zählerschaltung den Namen Ripple-Zähler , oder asynchroner Zähler .

Strobe-Signalzählerschaltung

In vielen Anwendungen ist dieser Effekt tolerierbar, da die Welligkeit sehr, sehr schnell auftritt (die Breite der Verzögerungen wurde hier zum besseren Verständnis der Effekte übertrieben).

Wenn wir beispielsweise nur einen Satz Leuchtdioden (LEDs) mit den Ausgängen des Zählers ansteuern wollten, wäre diese kurze Welligkeit völlig bedeutungslos.

Wenn wir diesen Zähler jedoch verwenden wollten, um die „Auswahl“-Eingänge eines Multiplexers zu steuern, einen Speicherzeiger in einer Mikroprozessor-(Computer-)Schaltung zu indizieren oder eine andere Aufgabe auszuführen, bei der falsche Ausgänge falsche Fehler verursachen könnten, wäre dies nicht akzeptabel .

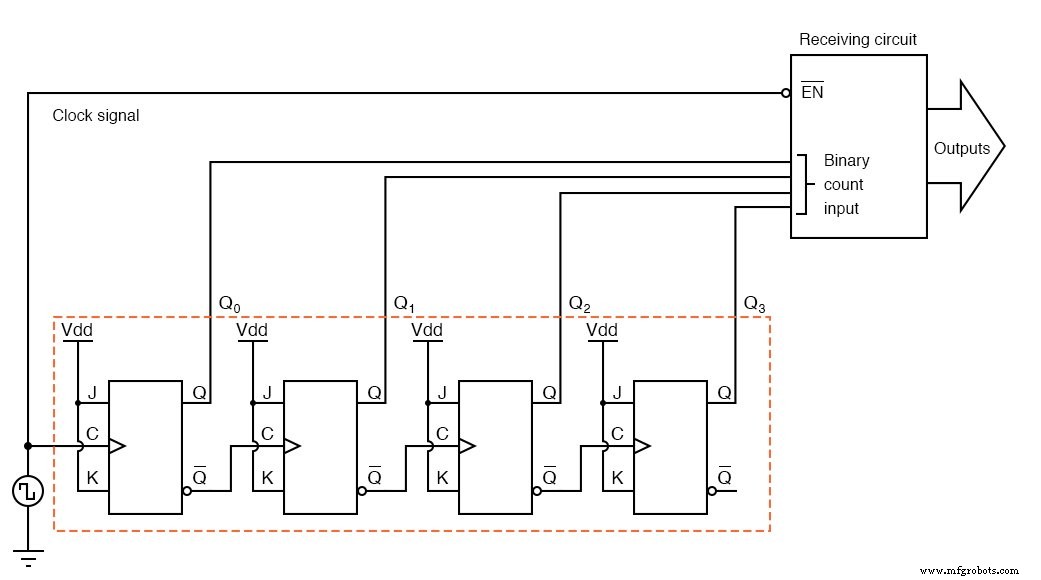

Es gibt eine Möglichkeit, diese Art von Zählerschaltung in Anwendungen zu verwenden, die empfindlich auf falsche, wellenerzeugte Ausgänge reagieren, und sie beinhaltet ein Prinzip, das als Strobing bekannt ist .

Die meisten Decoder- und Multiplexer-Schaltungen sind mit mindestens einem Eingang ausgestattet, der als „Enable“ bezeichnet wird.

Die Ausgänge eines solchen Schaltkreises werden nur aktiv, wenn der Freigabeeingang aktiviert wird.

Wir können diese Eingabe aktivieren für Strobe die Schaltung, die den Ausgang des Welligkeitszählers empfängt, so dass er während der kurzen Zeitspanne, in der die Zählerausgänge wellenförmig sein könnten, deaktiviert (und somit nicht auf den Zählerausgang reagiert) und erst aktiviert wird, wenn seit dem letzten Takt genügend Zeit vergangen ist dass alle Kräuselungen aufgehört haben.

In den meisten Fällen kann das Strobing-Signal derselbe Takt sein, der die Zählerschaltung antreibt:

Bei einem Aktiv-Low-Enable-Eingang reagiert die Empfangsschaltung nur auf den binären Zählerstand der Vier-Bit-Zählerschaltung, wenn das Taktsignal „low“ ist.

Sobald der Taktimpuls „high“ wird, reagiert die Empfangsschaltung nicht mehr auf die Ausgabe der Zählerschaltung.

Da die Zählerschaltung durch eine positive Flanke getriggert wird (wie durch die erste Flip-Flop-Takteingang), findet der gesamte Zählvorgang beim Übergang von niedrig nach hoch des Taktsignals statt, was bedeutet, dass die Empfangsschaltung deaktiviert wird, kurz bevor ein Umschalten an den vier Ausgangsbits der Zählerschaltung auftritt.

Die Empfangsschaltung wird erst aktiviert, wenn das Taktsignal in einen niedrigen Zustand zurückkehrt, der lange genug nach sein sollte alle Welligkeiten sind nicht mehr „sicher“, damit die neue Zählung auf die Empfangsschaltung wirken kann.

Der entscheidende Parameter ist hier die „High“-Zeit des Taktsignals:Sie muss mindestens so lang sein wie die maximal zu erwartende Welligkeit der Zählerschaltung.

Wenn nicht, aktiviert das Taktsignal die Empfangsschaltung vorzeitig, während noch eine gewisse Welligkeit stattfindet.

Nachteil der asynchronen Zählerschaltung:Begrenzte Geschwindigkeit

Ein weiterer Nachteil der asynchronen oder Welligkeitszählerschaltung ist die begrenzte Geschwindigkeit.

Während alle Gatterschaltungen in Bezug auf die maximale Signalfrequenz begrenzt sind, verschärft das Design asynchroner Zählerschaltungen dieses Problem, indem die Ausbreitungsverzögerungen addiert werden.

Selbst wenn in der Empfangsschaltung ein Strobing verwendet wird, kann eine asynchrone Zählerschaltung daher nicht mit einer höheren Frequenz als derjenigen getaktet werden, die es ermöglicht, die größtmögliche akkumulierte Ausbreitungsverzögerung lange vor dem nächsten Impuls zu verstreichen.

Die Lösung für dieses Problem ist eine Zählerschaltung, die Welligkeit vollständig vermeidet.

Eine solche Zählerschaltung würde die Notwendigkeit beseitigen, eine „Strobing“-Funktion in alle digitalen Schaltungen einzubauen, die den Zählerausgang als Eingang verwenden, und würde auch eine viel höhere Betriebsgeschwindigkeit als ihr asynchrones Äquivalent genießen.

Dieses Design der Zählerschaltung ist das Thema des nächsten Abschnitts.

RÜCKBLICK:

- Ein "Aufwärts"-Zähler kann hergestellt werden, indem die Takteingänge von positiv flankengetriggerten J-K-Flip-Flops mit den Q'-Ausgängen der vorhergehenden Flip-Flops verbunden werden. Eine andere Möglichkeit besteht darin, durch negative Flanken getriggerte Flip-Flops zu verwenden, die die Takteingänge mit den Q-Ausgängen der vorhergehenden Flip-Flops verbinden. In jedem Fall sind die Eingänge J und K aller Flip-Flops mit Vcc . verbunden oder Vdd um immer „high“ zu sein.

- Zählerschaltungen aus kaskadierten J-K-Flip-Flops, bei denen jeder Takteingang seine Impulse vom Ausgang des vorherigen Flip-Flops erhält, zeigen unweigerlich einen Welleneffekt , wobei zwischen einigen Schritten der Zählsequenz falsche Ausgabezählungen erzeugt werden. Diese Arten von Zählerschaltungen werden als asynchrone Zähler bezeichnet , oder Wellenzähler .

- Stroboskop ist eine Technik, die auf Schaltungen angewendet wird, die die Ausgabe eines asynchronen (Ripple-)Zählers empfangen, so dass die während der Welligkeitszeit erzeugten falschen Zählungen keine negativen Auswirkungen haben. Im Wesentlichen ist die Aktivierung Der Eingang einer solchen Schaltung ist so mit dem Taktimpuls des Zählers verbunden, dass er nur aktiviert wird, wenn sich die Zählerausgänge nicht ändern, und wird während der Zeiträume mit sich ändernden Zählerausgängen, in denen Welligkeit auftritt, deaktiviert.

VERWANDTE ARBEITSBLÄTTER:

- Ripple Counter-Arbeitsblatt

Industrietechnik