Variablen – VHDL-Beispiel

Variablen in VHDL verhalten sich ähnlich wie Variablen in C. Ihr Wert ist genau an der Stelle im Code gültig, an der die Variable geändert wird. Wenn also ein Signal den Wert der Variablen vorher verwendet die Zuweisung, hat sie den alten Variablenwert. Wenn ein Signal den Wert der Variablen after verwendet die Zuweisung hat den neuen Variablenwert.

Variablenregeln:

- Variablen können nur innerhalb von Prozessen verwendet werden

- Jede Variable, die in einem Prozess erstellt wird, kann nicht in einem anderen Prozess verwendet werden

- Variablen müssen nach dem Schlüsselwort process definiert werden aber vor dem Schlüsselwort begin

- Variablen werden mit := zugewiesen Zuordnungssymbol

- Zugewiesene Variablen nehmen sofort den Wert der Zuweisung an

Das Wichtigste zu verstehen ist, dass Variablen sofort den Wert ihrer Zuweisung annehmen. Hier ist ein Beispiel, das eine nützliche Möglichkeit zur Verwendung von Variablen zeigt:Speichern von Daten zur vorübergehenden Verwendung . Es verwendet eine case-Anweisung und den Verkettungsoperator kaufmännisches Und (&).

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

Im vorherigen Beispiel haben wir die beiden Signale verkettet, damit sie in der case-Anweisung verwendet werden können. Die Variable v_Choices stand unmittelbar nach ihrer Zuweisung zur Verfügung. Schauen wir uns ein anderes Beispiel an. Das folgende Beispiel ist umfassender und zeigt, wie Variablen sofort den Wert ihrer Zuweisung annehmen. Die Signale r_Var_Copy1 und r_Var_Copy2 scheinen gleich zu sein, aber r_Var_Copy2 kann niemals 5 erreichen, bevor es zurückgesetzt wird.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

Um unser Design zu simulieren, müssen wir eine Testbench erstellen. Außerdem kann es etwas schwierig sein, Variablen in der Simulation anzuzeigen. Wenn Sie Modelsim verwenden, lesen Sie mehr darüber, wie Sie Ihre Variablen im Wellenformfenster von Modelsim anzeigen können.

Testbench:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

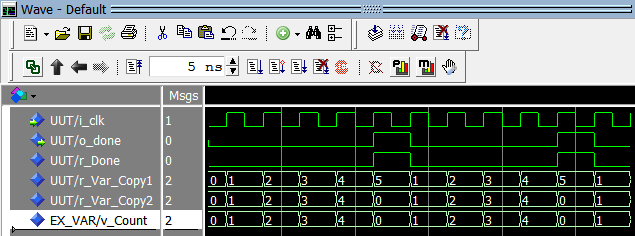

Variables Example Testbench Waveform

Variables Example Testbench Waveform Das obige Beispiel zeigt, wie sich Variablen von Signalen unterscheiden. Die Signale r_Var_Copy1 und r_Var_Copy2 scheinen gleich zu sein, aber r_Var_Copy2 kann niemals 5 erreichen, bevor es zurückgesetzt wird.

VHDL

- Prozeduranweisung – VHDL-Beispiel

- Aufzeichnungen - VHDL-Beispiel

- Analyseoptionen

- C#-Variablen und (primitive) Datentypen

- C++-Variablen, Literale und Konstanten

- C-Variablen, Konstanten und Literale

- C Lagerklasse

- Strings in C:Variable deklarieren, initialisieren, drucken, Beispiel

- Java - Variablentypen

- C - Variablen