Erste Schritte mit der Hardwarebeschreibungssprache von Verilog

In diesem Artikel untersuchen wir die Grundstruktur eines Verilog-Moduls und sehen uns einige Beispiele für die Verwendung des Verilog-Datentyps „wire“ und seiner Vektorform und gehen Sie kurz auf einige Unterschiede zwischen VHDL und Verilog ein.

In diesem Artikel untersuchen wir die Grundstruktur eines Verilog-Moduls, sehen uns einige Beispiele für die Verwendung des Verilog-Datentyps „wire“ und seiner Vektorform an und gehen kurz auf einige Unterschiede zwischen VHDL und Verilog ein.

Verilog und VHDL sind zwei Sprachen, die häufig verwendet werden, um digitale Schaltungen zu beschreiben. AAC enthält eine Reihe von technischen Artikeln, in denen die grundlegenden Konzepte von VHDL erörtert werden. Dieser Artikel dient als Ausgangspunkt für unsere Serie zu Verilog.

Brauche ich sowohl Verilog als auch VHDL?

Bevor wir mit unserer Diskussion beginnen, lassen Sie uns eine naheliegende Frage ansprechen:Müssen wir wirklich diese beiden Sprachen beherrschen?

Sowohl Verilog als auch VHDL sind leistungsstarke Werkzeuge, die zum Entwerfen einer komplexen digitalen Schaltung verwendet werden können. Obwohl es einige Unterschiede zwischen diesen beiden HDLs gibt, können Sie eine der beiden HDLs auswählen und verwenden. Ich glaube jedoch, dass Sie irgendwann davon profitieren werden, zumindest ein grundlegendes Verständnis beider Sprachen zu haben. Als Designer benötigen wir manchmal ein Beispielcodesegment, um eine Vorstellung von der Codierung eines Projekts zu bekommen. Wir surfen stundenlang im Netz und finden endlich, was wir brauchen, aber es macht für uns keinen Sinn – es steht in der für uns völlig unbekannten HDL geschrieben. Ohne ein grundlegendes Verständnis der Sprache können wir die Techniken möglicherweise nicht vollständig verstehen.

Verilog-Entwicklung

Verilog wurde Anfang 1984 von Gateway Design Automation entwickelt (ungefähr drei Jahre nachdem VHDL vom US-Verteidigungsministerium initiiert wurde). Mit der Unterstützung des DoD wurde VHDL 1987 zum IEEE-Standard. Verilog schaffte es erst 1995 in die Szene. Heute sind sowohl VHDL als auch Verilog beliebte HDLs und FPGA-Designtools unterstützen normalerweise beide Sprachen.

Das Wort „Verilog“ ist eine Kombination aus den Wörtern „Verifikation“ und „Logik“, da die Sprache zuerst als Simulations- und Verifikationswerkzeug vorgeschlagen wurde. Beginnen wir mit den Konzepten und der Syntax von Verilog.

Beispiel 1

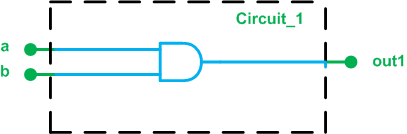

Schreiben wir als erstes Beispiel den Verilog-Code für die in Abbildung 1 dargestellte Schaltung.

Abbildung 1. Circuit_1

Es gibt zwei Eingänge und einen Ausgang. Die Ports sind alle ein Bit breit. Die Funktionalität der Schaltung besteht darin, die beiden Eingänge mit UND zu versehen und das Ergebnis auf den Port out1 zu legen.

Eine mögliche Verilog-Beschreibung für das Modul Circuit_1 lautet:

Zeilen 1 und 8

Diese beiden Zeilen verwenden die Schlüsselwörter „module“ und „endmodule“, um anzugeben, dass die Zeilen dazwischen (Zeile 2 bis 7) alle eine Schaltung namens „Circuit_1“ beschreiben. Dieser Name ist willkürlich und ermöglicht es uns, später auf diese Schaltung zu verweisen.

Zeilen 2 bis 6

Diese Zeilen spezifizieren die Schnittstelle von „Circuit_1“ mit seiner Umgebung. Die Ein- und Ausgabeports werden mit den Schlüsselwörtern „input“ und „output“ beschrieben. Auf diese Schlüsselwörter folgt ein weiteres Schlüsselwort „wire“ und dann der Name des Ports (siehe Abbildung 1). Was sagt das Stichwort „Draht“ aus? „Wire“ ist ein Verilog-Datentyp, der einen physischen Draht im Design darstellt. Wir werden die Verilog-Datentypen in einem zukünftigen Artikel genauer besprechen, aber im Moment wissen wir, dass es in unserem Modul drei Drähte namens a, b und out1 gibt, und da diese in der Port-Deklaration angegeben sind, entsprechen sie die Modulschnittstelle.

Zeile 7

Diese Zeile verwendet den bitweisen AND-Operator, d. h. &, um die Funktionalität der Schaltung zu beschreiben. Das Schlüsselwort „assign“ legt a&b auf den Ausgangsport out1. Diese Art der Zuweisung wird als kontinuierliche Zuweisung bezeichnet. Es heißt so, weil die Zuweisung immer dann aktiv ist, wenn sich ein Operand auf der rechten Seite ändert, a&b ausgewertet und out1 zugewiesen wird. Wir können uns eine kontinuierliche Zuweisung als eine kombinatorische Schaltung vorstellen, deren Ausgang abhängig von seinen Eingängen kontinuierlich aktualisiert wird. In unserem Beispiel ist diese kombinatorische Schaltung ein einfaches UND-Gatter. Es gibt auch Verfahrenszuweisungen in Verilog HDL, die in zukünftigen Artikeln erörtert werden.

Jetzt können wir ein Softwarepaket wie Xilinx ISE verwenden, um den obigen Code zu überprüfen. Ein Verilog-basiertes Tutorial zu dieser Software finden Sie hier (PDF).

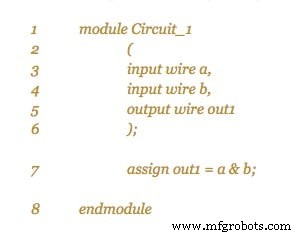

Vergleich von Beispiel 1 mit dem VHDL-Code

Abbildung 2 unten zeigt die Verilog- und VHDL-Beschreibungen für das Modul Circuit_1.

Abbildung 2. Vergleich von Verilog- und VHDL-Beschreibungen für Circuit_1.

Wie Sie sehen, müssen wir beim Codieren in VHDL einige Bibliotheken einbeziehen. Diese Bibliotheken geben die Definition für die Datentypen und Operatoren an. In Anbetracht der Hinzufügung dieser Bibliotheken und des allgemeinen Formats von VHDL stellen wir fest, dass der VHDL-Code ausführlicher ist. Diese Ausführlichkeit ist jedoch nicht ohne Vorteile. Beispielsweise kann die Bibliotheksverwaltungsfunktion von VHDL bei der Modellierung von Systemen auf höherer Ebene hilfreich sein. In zukünftigen Artikeln werden wir gelegentlich die Vor- und Nachteile dieser beiden HDLs diskutieren.

Verilog hat ein Vier-Werte-System

In den meisten Verilog-Datentypen werden vier Grundwerte verwendet. Die in Listing 1 definierten Drähte können einen der folgenden Werte annehmen:

- 0:für einen logisch niedrigen oder einen falschen Zustand

- 1:für eine logische High- oder True-Bedingung

- z:für den hochohmigen Zustand (kann verwendet werden, um die Ausgabe eines Tri-State-Puffers zu beschreiben)

- x:für einen egalen oder unbekannten Wert (wenn ein Eingang nicht initialisiert ist oder zwei oder mehr widersprüchliche Ausgänge miteinander verbunden sind).

Der Datentyp VHDL std_logic kann neun verschiedene Werte annehmen, aber seine häufig verwendeten Werte sind „0“, „1“, „Z“ und „-“ („-“ steht für „egal“.

Beispiel 2

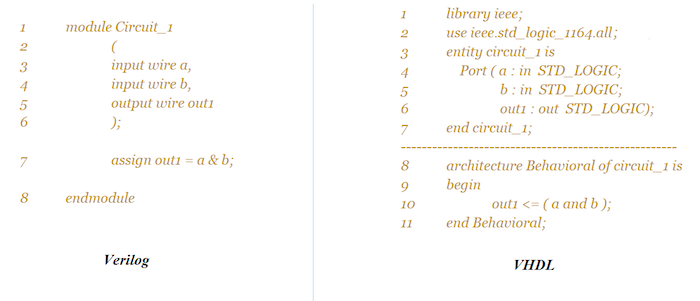

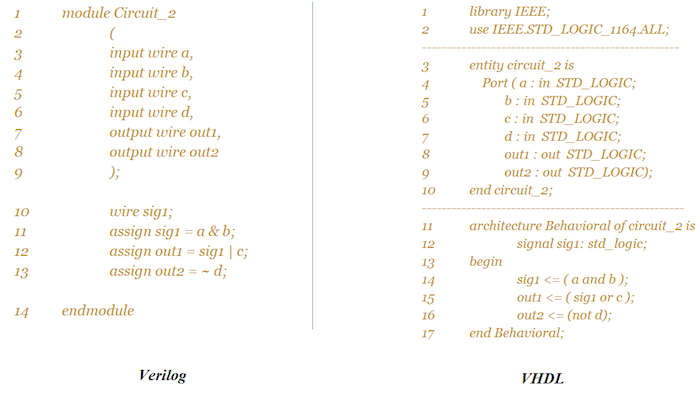

Als weiteres Beispiel schreiben wir den Verilog-Code für die Schaltung (die wir Circuit_2 nennen werden) in Abbildung 3.

Abbildung 3. Circuit_2

Der folgende Verilog-Code beschreibt diese Schaltung:

Die im obigen Code verwendeten Elemente sind denen in Beispiel 1 ähnlich, außer dass in Zeile 10 des Codes ein internes Signal definiert ist. Mit dem Schlüsselwort „wire“ wird der Datentyp dieser Verbindung angegeben. Wie oben besprochen, würde sich der Datentyp „Wire“ im Design in einen physischen Draht übersetzen.

Der obige Code verwendet auch einige neue bitweise Operatoren von Verilog:~ für NOT und | für den ODER-Betrieb. Ein weiterer nützlicher bitweiser Operator ist ^ für die XOR-Operation. Abbildung 4 zeigt sowohl die Verilog- als auch die VHDL-Beschreibung für das Circuit_2-Modul. Solche Vergleiche können Ihnen helfen, die Unterschiede und Ähnlichkeiten zwischen diesen beiden Sprachen zu erkennen.

Abbildung 4. Vergleich von Verilog- und VHDL-Beschreibungen für Circuit_2.

Beispiel 3

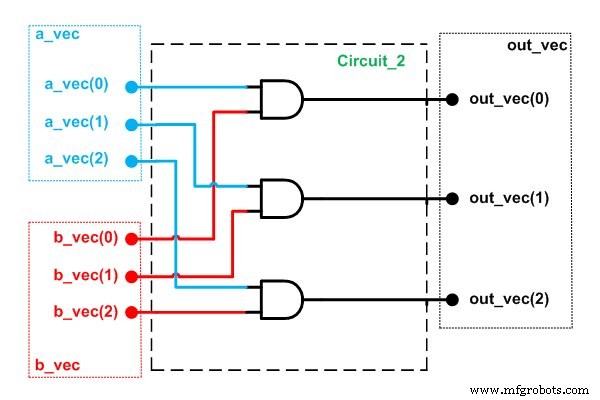

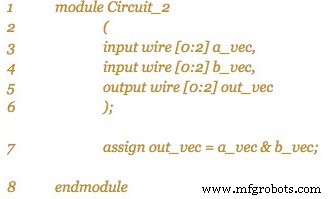

Für unser drittes und letztes Beispiel geben wir den Verilog-Code für den Schaltplan in Abbildung 5 an.

Abbildung 5. Schema zum Beispiel 3.

Wie Sie sehen, besteht zwischen den blauen Eingangsports und den roten eine gewisse Beziehung:Die entsprechenden Eingänge werden mit dem UND-Operator verknüpft. Das Ergebnis wird einem Ausgabeport zugewiesen. In solchen Fällen können wir die Signale gruppieren und als Vektor behandeln. Dadurch wird der Code kompakt und lesbar.

Mit dem Vektorkonzept in Verilog können wir den Code in Listing 1 leicht erweitern, um die obige Schaltung zu beschreiben (siehe Code in Listing 3 unten).

Beachten Sie, dass der Indexbereich der Vektoren entweder aufsteigend ([0:2] wie oben verwendet) oder absteigend ([2:0]) sein kann. Obwohl oben das aufsteigende Format verwendet wird, ist es normalerweise weniger fehleranfällig, die absteigende Form zu verwenden. Dies liegt daran, dass der absteigende Stil unserer Wahrnehmung entspricht, dass die ganz linke Position einer Binärzahl den höchsten Index hat. Beachten Sie, dass Vektoren auch in VHDL verwendet werden.

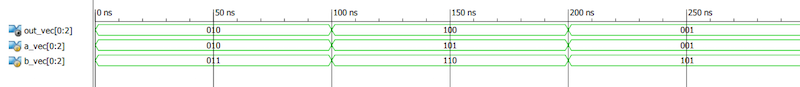

Abbildung 6 unten zeigt eine ISE-Simulation des Codes in Listing 3.

Abbildung 6. ISE-Simulation des Codes von Beispiel 3.

In diesem Artikel haben wir besprochen, dass es eine gute Idee ist, sowohl VHDL als auch Verilog zu lernen, wir haben die Grundstruktur eines Verilog-Moduls studiert und uns mit dem Verilog-Datentyp „wire“ und seiner Vektorform vertraut gemacht. Wir haben auch kurz auf einige Unterschiede zwischen VHDL und Verilog eingegangen. Der nächste Artikel in unserer Verilog-Reihe befasst sich mit dem Entwerfen von kombinatorischen Schaltungen in Verilog.

Eingebettet

- Code Ready Container:Erste Schritte mit Prozessautomatisierungstools in der Cloud

- Erste Schritte mit dem Keramik-3D-Druck

- Erste Schritte mit TJBot

- Erste Schritte mit dem RAK 831 Lora Gateway und RPi3

- Erste Schritte mit dem RAK831 LoRa Gateway und RPi3

- Erste Schritte mit KI-Inferenz am Edge

- Erste Schritte mit der Eagle-Gruppe:Was Sie wissen müssen

- Erste Schritte mit My.Cat.com

- Node-RED und erste Schritte mit Docker

- Erste Schritte mit Go auf PLCnext