Neigung (integrieren) ADC

Bisher konnten wir der schieren Menge an Komponenten im Flash-Konverter nur durch die Verwendung eines DAC als Teil unserer ADC-Schaltung entkommen. Dies ist jedoch nicht unsere einzige Option. Es ist möglich, die Verwendung eines DAC zu vermeiden, wenn wir eine analoge Rampenschaltung und einen digitalen Zähler mit präzisem Timing ersetzen.

Das ist die Grundidee hinter dem sogenannten Single-Slope , oder integrieren ADC. Anstatt einen DAC mit einem rampenförmigen Ausgang zu verwenden, verwenden wir eine Operationsverstärkerschaltung namens Integrator um eine Sägezahnwellenform zu erzeugen, die dann von einem Komparator mit dem analogen Eingang verglichen wird.

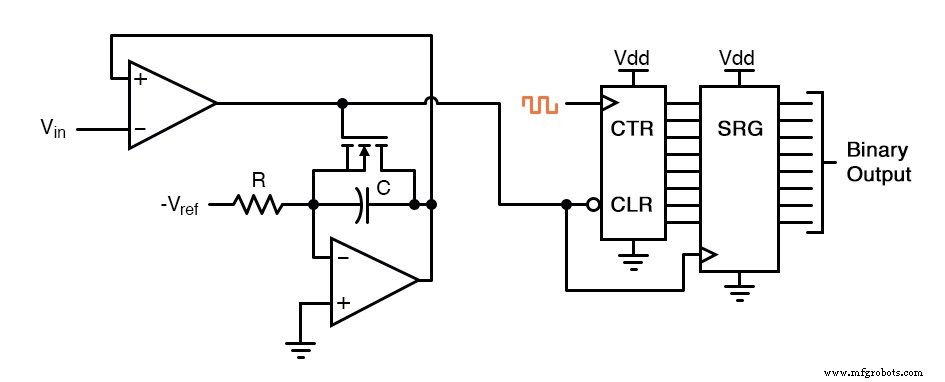

Die Zeit, die die Sägezahnwellenform benötigt, um den Spannungspegel des Eingangssignals zu überschreiten, wird mit einem digitalen Zähler gemessen, der mit einer präzisen Rechteckwelle (normalerweise von einem Quarzoszillator) getaktet wird. Das grundlegende schematische Diagramm ist hier gezeigt:

Das hier gezeigte IGFET-Kondensatorentladungstransistorschema ist etwas zu stark vereinfacht. In Wirklichkeit müsste höchstwahrscheinlich eine mit dem Taktsignal getaktete Latch-Schaltung mit dem IGFET-Gate verbunden werden, um eine vollständige Entladung des Kondensators sicherzustellen, wenn der Ausgang des Komparators hoch geht.

Die Grundidee ist jedoch in diesem Diagramm ersichtlich. Wenn der Komparatorausgang niedrig ist (Eingangsspannung größer als der Integratorausgang), darf der Integrator den Kondensator auf lineare Weise laden. Währenddessen zählt der Zähler mit einer durch die Präzisionstaktfrequenz festgelegten Rate aufwärts.

Die Zeit, die der Kondensator benötigt, um sich auf den gleichen Spannungspegel wie der Eingang aufzuladen, hängt vom Eingangssignalpegel und der Kombination von -Vref . ab , R und C. Wenn der Kondensator diesen Spannungspegel erreicht, geht der Komparatorausgang hoch und lädt den Ausgang des Zählers in das Schieberegister für eine endgültige Ausgabe.

Der IGFET wird durch den hohen Ausgang des Komparators „ein“ getriggert, wodurch der Kondensator wieder auf null Volt entladen wird. Wenn die Ausgangsspannung des Integrators auf Null abfällt, schaltet der Komparatorausgang zurück auf einen niedrigen Zustand, wodurch der Zähler gelöscht wird und der Integrator die Spannung wieder hochfahren kann.

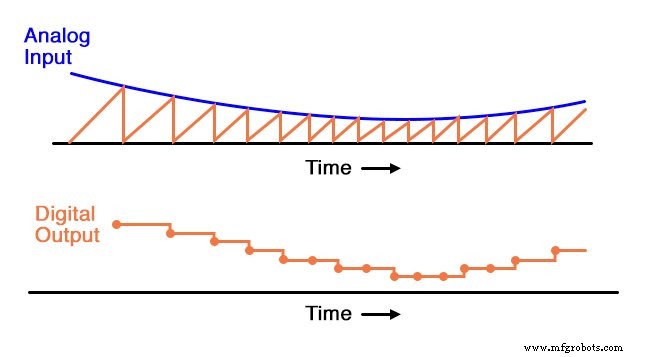

Diese ADC-Schaltung verhält sich sehr ähnlich wie der digitale Rampen-ADC, außer dass die Komparator-Referenzspannung eine glatte Sägezahn-Wellenform und keine „Treppe“ ist:

Der Single-Slope-ADC hat alle Nachteile des digitalen Rampen-ADC, mit dem zusätzlichen Nachteil der Kalibrierungsdrift . Die genaue Übereinstimmung des Ausgangs dieses ADC mit seinem Eingang hängt davon ab, dass die Spannungsflanke des Integrators an die Zählrate des Zählers (die Taktfrequenz) angepasst ist.

Beim digitalen Rampen-ADC hatte die Taktfrequenz keinen Einfluss auf die Wandlungsgenauigkeit, sondern nur auf die Aktualisierungszeit. Da bei dieser Schaltung die Integrationsrate und die Zählrate unabhängig voneinander sind, ist eine Variation zwischen den beiden mit zunehmendem Alter unvermeidlich und führt zu einem Genauigkeitsverlust.

Das einzig Gute an dieser Schaltung ist, dass sie die Verwendung eines DAC vermeidet, was die Komplexität der Schaltung reduziert.

Dual-Slope-Konverter

Eine Antwort auf dieses Dilemma der Kalibrierungsdrift findet sich in einer Designvariante namens Dual-Slope Konverter. Im Dual-Slope-Wandler wird eine Integratorschaltung in abwechselnden Zyklen positiv und negativ angesteuert, um herunter- und dann hochzufahren, anstatt am Ende jedes Zyklus auf 0 Volt zurückgesetzt zu werden.

In einer Rampenrichtung wird der Integrator durch das positive analoge Eingangssignal angesteuert (wodurch eine negative, variable Änderungsrate der Ausgangsspannung oder Steigung des Ausgangs erzeugt wird ) für einen festen Zeitraum, gemessen von einem Zähler mit einer Präzisionsfrequenzuhr. Dann in die andere Richtung mit einer festen Referenzspannung (die eine feste Änderungsrate der Ausgangsspannung erzeugt) mit der Zeit, die von demselben Zähler gemessen wird.

Der Zähler hört auf zu zählen, wenn der Ausgang des Integrators dieselbe Spannung erreicht wie zu Beginn des festen Zeitabschnitts des Zyklus. Die Zeit, die der Kondensator des Integrators benötigt, um sich wieder auf seine ursprüngliche Ausgangsspannung zu entladen, gemessen an der vom Zähler aufgelaufenen Größe, wird zum digitalen Ausgang des ADC-Schaltkreises.

Das Dual-Slope-Verfahren kann man sich analog als Drehfeder vorstellen, wie sie in einem mechanischen Uhrwerk verwendet wird. Stellen Sie sich vor, wir bauen einen Mechanismus, um die Drehzahl einer Welle zu messen.

Somit ist die Wellendrehzahl unser „Eingangssignal“, das von diesem Gerät gemessen werden soll. Der Messzyklus beginnt mit der Feder im entspannten Zustand.

Die Feder wird dann durch die rotierende Welle (Eingangssignal) für eine festgelegte Zeit gedreht oder „aufgezogen“. Dadurch wird die Feder proportional zur Wellendrehzahl gespannt:Eine höhere Wellendrehzahl entspricht einer schnelleren Wickelgeschwindigkeit und einer größeren Federspannung, die sich über diesen Zeitraum ansammelt.

Danach wird die Feder von der Welle abgekoppelt und kann sich mit einer festen Geschwindigkeit abwickeln, wobei die Zeit, die sie benötigt, um sich wieder in einen entspannten Zustand zurückzuziehen, von einem Zeitgeber gemessen wird. Die Menge der Zeit es dauert, bis sich die Feder mit dieser festen Geschwindigkeit entspannt, ist direkt proportional zur Geschwindigkeit bei der es während des festen Zeitabschnitts des Zyklus gewickelt wurde (Eingangssignalgröße).

Diese Technik der Analog-Digital-Wandlung entgeht dem Kalibrierungsdriftproblem des Single-Slope-ADC, da sowohl der Integrationskoeffizient (oder „Verstärkung“) des Integrators als auch die Geschwindigkeit des Zählers während des gesamten „Aufwickelns“ und „Abwickelns“ wirksam sind ” Zyklusabschnitte. Wenn die Taktgeschwindigkeit des Zählers plötzlich ansteigen würde, würde dies die feste Zeitdauer verkürzen, in der der Integrator „aufläuft“ (was zu einer geringeren vom Integrator akkumulierten Spannung führt), aber es würde auch bedeuten, dass er während der Zeitdauer von . schneller zählt Zeit, in der sich der Integrator mit einer festen Rate „abwickeln“ durfte.

Der Anteil, um den der Zähler schneller zählt, ist der gleiche Anteil, wie die akkumulierte Spannung des Integrators vor der Änderung der Taktfrequenz verringert wird. Somit würde sich der Taktfehler von selbst aufheben und der digitale Ausgang wäre genau das, was er sein sollte.

Ein weiterer wichtiger Vorteil dieses Verfahrens besteht darin, dass das Eingangssignal gemittelt wird, wenn es den Integrator während des festen Zeitabschnitts des Zyklus antreibt. Alle Änderungen des Analogsignals während dieses Zeitraums wirken sich kumulativ auf den Digitalausgang am Ende dieses Zyklus aus.

Andere ADC-Strategien „erfassen“ lediglich den analogen Signalpegel zu einem einzigen Zeitpunkt in jedem Zyklus. Wenn das analoge Signal „verrauscht“ ist (erhebliche Pegel von störenden Spannungsspitzen/-einbrüchen enthält), kann eine der anderen ADC-Wandlertechnologien gelegentlich eine Spitze oder einen Einbruch umwandeln, da sie das Signal zu einem einzigen Zeitpunkt wiederholt erfasst.

Ein Dual-Slope-ADC hingegen mittelt alle Spitzen und Einbrüche innerhalb der Integrationsperiode, wodurch ein Ausgang mit größerer Störfestigkeit bereitgestellt wird. Dual-Slope-ADCs werden in Anwendungen verwendet, die eine hohe Genauigkeit erfordern.

VERWANDTES ARBEITSBLATT:

- Arbeitsblatt zur Analog-zu-Digital-Konvertierung

Industrietechnik