Effektive Maßnahmen zur Beseitigung des Verzugsproblems bei Leiterplatten

Heutzutage erfordern elektronische Produkte Miniaturisierung und hohe Genauigkeit, so dass die Miniaturisierung von Komponenten zu einem wesentlichen Entwicklungstrend geworden ist. Wenn miniaturisierte Bauteile für die Bestückung großflächiger Leiterplatten bereit sind, werden deutlich höhere Anforderungen an die Platinenglätte gestellt. Natürlich ist es für Leiterplattenhersteller zu einem wesentlichen Thema geworden, darüber nachzudenken, wie das Ausmaß des Verzugs von Leiterplatten reduziert werden kann.

Gemäß den durch IPC-600 bestätigten Herstellungsvorschriften darf der Verzug von Leiterplatten, die für die SMT-Bestückung bereit sind, höchstens 0,75 % betragen. Bei der Bestückung kleiner Bauteile auf großflächigen Leiterplatten greift diese Regelung jedoch nicht. Um den Anforderungen der miniaturisierten Komponentenmontage auf Leiterplatten mit großen Flächen gerecht zu werden, sollte der Leiterplattenverzug im Allgemeinen auf 0,5 % oder weniger reduziert werden.

Verzugsanalyse

Das Verzugsproblem wird in diesem Teil dieses Artikels zuerst mit einer 8-lagigen Muster-Leiterplatte analysiert, deren Größe 248 mm ± 0,25 x 162,2 ± 0,20 beträgt. Der Verzug dieser Platte muss 0,5 % betragen, aber sein praktischer Verzug nach der ersten Produktionscharge fällt in den Bereich von 2,5 % bis 3,2 %.

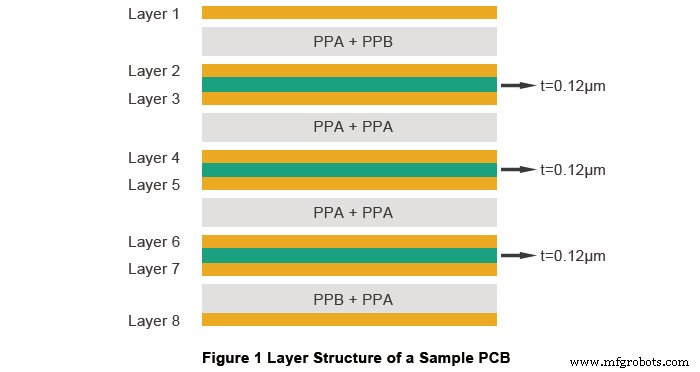

Der Schichtaufbau einer 8-Schicht-Leiterplatte wird wie folgt gezeigt.

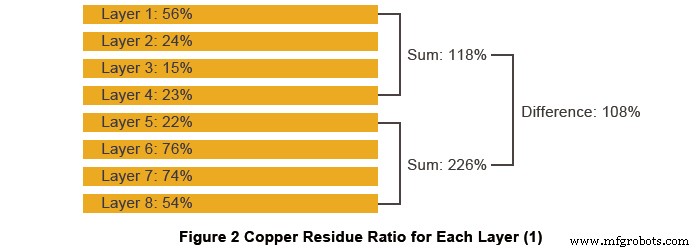

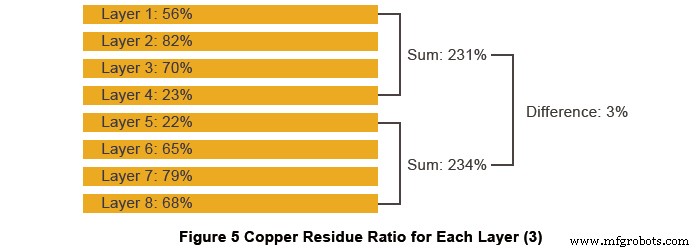

Das Kupferrückstandsverhältnis für jede Schicht ist in der folgenden Abbildung dargestellt.

Basierend auf der obigen Analyse ist das herausragende Merkmal dieser Musterplatte eine ungleichmäßige Kupferverteilung jeder Schicht. Außerdem ist Kupfer relativ dick. Als Ergebnis wird eine Platinenverwerfung hervorgerufen.

Lösungen zur Vermeidung von PCB-Verwerfungen

• Schema Nr. 1

Die primäre Methode zum Ausgleichen von Kupferrückständen zwischen den Schichten der Platine besteht darin, Kupfer in einen Rohling zu gießen.

Um die Verformungsspannung der Platte zu reduzieren, ist es eine angenehme Idee, die Plattengröße mit einer Rotationsplattenmethode zu verkleinern. Bei dieser Beispielplatine sollte die Panelgröße von 610 mm x 520 mm auf 610 mm x 356 mm geändert werden. Das Panel-Array des ersteren ist 3x2, während das des letzteren 2x2 ist.

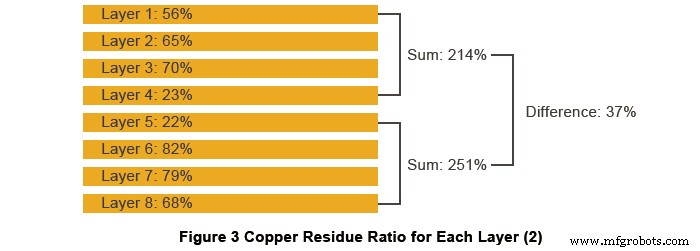

Aufgrund der oben genannten Verbesserungsmaßnahmen wird das Kupferrückstandsverhältnis in Abbildung 3 unten gezeigt. Nach solchen Modifikationen wurde der Verzug so modifiziert, dass er im Bereich von 2,0 % bis 2,9 % liegt, was eine offensichtliche Verbesserung erfährt, aber etwas weit von der Anforderung von 0,5 % entfernt ist.

•Schema#2

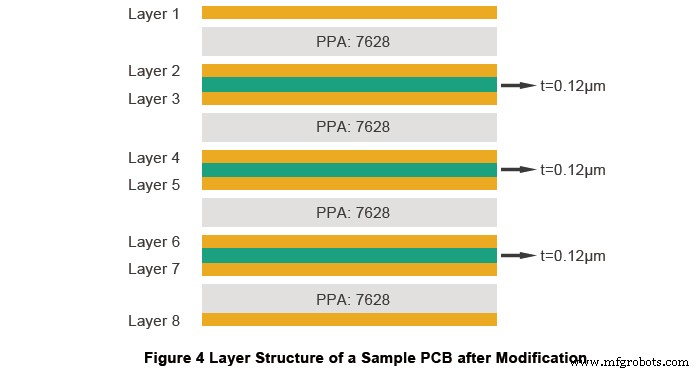

Basierend auf Schema Nr. 1 wird Platinensteifigkeit hinzugefügt. Nach einer solchen Modifikation kann der Schichtaufbau der Leiterplatte durch die folgende Abbildung angezeigt werden.

Die Implementierung dieses Schemas führt zu einem PCB-Verzug im Bereich von 2,0 % bis 2,9 %. Offensichtlich funktioniert dieses Schema nicht bei der Lösung von Verzugsproblemen, was darauf hinweist, dass es wenig Korrelation zwischen Verzug und Board-Steifigkeit gibt. Wir müssen mit der Optimierung von Schema Nr. 1 fortfahren, das heißt, wir müssen nach weiteren Wegen zur Kupferrückstandsbilanz suchen.

•Schema#3

Basierend auf Scheme#1 sollen Layer 2 und Layer 6 miteinander ausgetauscht werden. Das Kupferrückstandsverhältnis für jede PCB-Schicht nach der Anwendung von Schema Nr. 3 ist in Abbildung 5 unten dargestellt.

Gemäß Schema Nr. 3 bleibt der PCB-Verzug innerhalb von 0,5 % und bleibt auch nach zweimaligem Reflow-Löten immer noch bei 0,5 %, was mit der Nachfrage kompatibel ist. Darüber hinaus bestätigt eine Probeproduktion von 300 Stück die Zuverlässigkeit dieses Schemas. Daher schneidet Schema Nr. 3 von allen Schemata am besten ab.

Da die Verteilung unter allen dielektrischen Schichten gleichmäßig ist, ist es gemäß den obigen Experimenten die ungleichmäßige Verteilung von Kupfer, die dazu führt, dass eine PCB-Verwerfung auftritt. Durch das Ausgleichen von Kupferresten auf jeder Schicht der Leiterplatte reduziert sich der Leiterplattenverzug von 2,5 % bis 3,2 % auf den Bereich innerhalb von 0,5 %, was darauf hinweist, dass die Kernlösung für das Problem des Leiterplattenverzugs im Gleichgewicht zwischen Kupferresten zwischen dielektrischen Schichten und Kupfer liegt Schichten. Was den Verzug während des Montageprozesses anbelangt, sollte dementsprechend ein Ausgleich durch Komponentenlayout, Wärmeverteilung und Montageverteilung erreicht werden, damit der Platinenverzug bei garantierter Produktqualität verringert werden kann.

Hilfreiche Ressourcen

• Faktoren, die die Anzahl der Schichten und die Schichtverteilung in Leiterplatten bestimmen

• Mehrschichtige Leiterplattenherstellung

• Die wichtigsten PCB-Designregeln, die Sie kennen müssen

• PCB-Designelemente, die SMT beeinflussen Fertigung

Industrietechnik

- Bow &Twist-Probleme mit PCBS

- SMT-Bestückung für Leiterplatten

- Leiterplatten für raue Umgebungen

- Leitfaden zu den IPC-Standards für Leiterplatten

- Niedertemperatur-PCB-Material

- Design für die Herstellung von Leiterplatten

- Vorschriften für bleifreie PCB

- Was verursacht Schäden an flexiblen Leiterplatten?

- PCB-Marktausblick

- Leiterplattenfertigung für 5G