So stoppen Sie die Simulation in einer VHDL-Testbench

Wie stoppen Sie den VHDL-Simulator, wenn die Simulation abgeschlossen ist? Dazu gibt es mehrere Möglichkeiten. In diesem Artikel untersuchen wir die gängigsten Methoden, um einen erfolgreichen Testbench-Lauf zu beenden.

Der hier vorgestellte VHDL-Code ist universell und sollte in jedem leistungsfähigen VHDL-Simulator funktionieren. Für die Methoden mit Tcl werde ich die Befehle für die ModelSim- und Vivado-Simulatoren auflisten.

Sie können ein Beispielprojekt mit den vier verschiedenen Testbenches aus diesem Artikel herunterladen, wenn Sie ModelSim installiert haben. Geben Sie Ihre E-Mail-Adresse in das untenstehende Formular ein, um die ZIP-Datei zu erhalten!

Mit Fertig stellen Verfahren

Das VHDL beendet Das Verfahren ist meine bevorzugte Methode, um eine VHDL-Testbench zu stoppen, die ohne Fehler abgeschlossen wird. Sie müssen „finish“ aus dem STD.ENV-Paket importieren und die Testbench in VHDL-2008 oder neuer kompilieren, um sie zu verwenden.

Der folgende Code beendet die Simulation, wenn wir die letzte Zeile des Testbench-Sequencer-Prozesses erreichen.

use std.env.finish; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'finish'"; finish; end process;

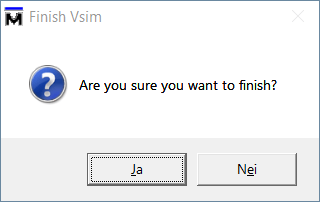

Beachten Sie, dass beenden beendet standardmäßig die Simulation. Wenn Sie ModelSim in der GUI-Version ausführen, erscheint ein Popup mit der Meldung „Sind Sie sicher, dass Sie beenden möchten?“. Wenn Sie auf Ja klicken, wird ModelSim beendet.

Das ist wahrscheinlich nicht das, was Sie wollen. Glücklicherweise können wir dieses Verhalten verhindern, indem wir die Option „-onfinish stop“ zum vsim-Befehl hinzufügen, wie unten gezeigt. Damit fertig Die Prozedur verhält sich genauso wie der Stopp Verfahren, das wir im nächsten Abschnitt dieses Artikels besprechen werden.

vsim -onfinish stop work.using_finish_tb

Ein Vorteil der Verwendung von finish ist, dass Sie das Standardverhalten verwenden können, wenn Sie im Stapelmodus simulieren. Wenn Sie Skripte verwenden, um die Simulation zu starten, möchten Sie die Kontrolle an das aufrufende Skript zurückgeben, nachdem die Simulation beendet ist.

Das folgende Beispiel zeigt eine Testbench mit finish -Prozedur im ModelSim-Stapelmodus unter Linux gestartet. Nachdem die Testbench abgeschlossen ist, wird der Simulator beendet und in der letzten Zeile befinden wir uns wieder in der Linux-Shell.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_finish_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_finish_tb # vsim work.using_finish_tb # Start time: 22:58:31 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_finish_tb(sim) # run -all # ** Note: Calling 'finish' # Time: 1 ms Iteration: 0 Instance: /using_finish_tb # End time: 22:58:31 on Jun 21,2020, Elapsed time: 0:00:00 # Errors: 0, Warnings: 8 jonas@ubuntu:~/stop_tb$

Das VHDL beendet Das Verfahren ist im Standard-ENV-Paket definiert. Wie wir aus dem folgenden Code ersehen können, gibt es zwei überladene Varianten. Es gibt die Version ohne Parameter, die ich immer verwende, und eine andere, die eine Status-Ganzzahl als konstante Eingabe verwendet.

procedure FINISH (STATUS: INTEGER); procedure FINISH;

Man könnte meinen, dass der Status-Integer beim Aufruf aus einer Linux-Shell zum Exit-Code wird, aber das ist nicht der Fall, zumindest nicht bei ModelSim. Das Problem bei der Verwendung dieses Statuscodes besteht darin, dass seine Funktion vom Simulator abhängt. Der Wortlaut im VHDL-2008-Standard lautet „der Wert des STATUS-Parameters kann vom Host-Simulator in einer implementierungsdefinierten Weise verwendet werden “.

Sie können jedoch den Wert des Linux-Exit-Codes in ModelSim steuern, indem Sie den Tcl-Befehl exit -code <value> verwenden , aber das ist eine andere Geschichte.

Mit der Haltestelle Verfahren

Die VHDL stoppt Prozedur bewirkt, dass die Simulation angehalten wird. Das kann nützlich sein, wenn Sie Signalwerte manuell untersuchen oder die Simulation später sogar fortsetzen möchten. Der Simulator behandelt es wie einen Breakpoint.

Das folgende Beispiel zeigt, wie der Stopp importiert und verwendet wird Verfahren.

use std.env.stop; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'stop'"; stop; end process;

Ein Problem bei der Verwendung von stop in skriptbasierten Setups ist, dass die Simulation nicht beendet wird. Anstatt die Kontrolle an den Aufrufer zurückzugeben, öffnet ModelSim eine Tcl-Befehlsshell, wodurch das aufrufende Skript auf unbestimmte Zeit hängen bleibt.

Die folgende Auflistung zeigt die Ausgabe der Ausführung der Testbench, die den Stopp verwendet Vorgang im Batch-Modus. Nachdem die Simulation beendet ist, befinden wir uns immer noch in ModelSim. Um die Tcl-Shell zu verlassen, müssten wir „exit“.

eingebenjonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_stop_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_stop_tb # vsim work.using_stop_tb # Start time: 22:58:56 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_stop_tb(sim) # run -all # ** Note: Calling 'stop' # Time: 1 ms Iteration: 0 Instance: /using_stop_tb # Break in Process SEQUENCER_PROC at ~/stop_tb/src/using_stop_tb.vhd line 23 # Stopped at ~/stop_tb/src/using_stop_tb.vhd line 23 VSIM 3>

Genau wie das Finish Prozedur, stopp erfordert VHDL-2008 oder neuer. Wie unten gezeigt, existiert eine überladene Version der Prozedur. Es nimmt einen ganzzahligen Statuswert an, aber das Verhalten variiert zwischen den Simulatoren.

procedure STOP (STATUS: INTEGER); procedure STOP;

Mit dem assert Schlüsselwort

Eine ausfallsichere und universelle Möglichkeit, eine VHDL-Testbench zu stoppen, besteht darin, einen Behauptungsfehler zu erstellen. Das war die erste Art, wie mir jemand beibrachte, die Simulation zu beenden, als ich VHDL an der Universität lernte.

Es sind keine zusätzlichen Importe erforderlich und es funktioniert in allen VHDL-Versionen. Achten Sie nur darauf, den Schweregrad Fehler zu verwenden , wie im folgenden Beispiel gezeigt.

SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; assert false report "Test: OK" severity failure; end process;

Und warum hasse ich diese Art, eine erfolgreiche Simulation zu stoppen?

Zunächst einmal sieht es seltsam und verwirrend aus, den Ausdruck aus dem obigen Beispiel zu sehen:

# ** Failure: Test: OK

Es heißt, es sei ein „Fehler“, aber der Test ist gleichzeitig „OK“. Das liegt daran, dass assert -Anweisung soll einen Fehlerzustand anzeigen und nicht den erfolgreichen Abschluss der Simulation.

Das andere ärgerliche Problem, das mir einfällt, ist, dass es schwierig wird, programmgesteuert herauszufinden, ob die Simulation erfolgreich war.

Die meisten VHDL-Profis starten die Simulationen irgendwann aus einem Skript, beispielsweise als Teil eines größeren Regressionstestschemas. Wenn die Testbench auch bei einem Behauptungsfehler stoppt, obwohl nichts falsch ist, können wir das nicht als Marker verwenden, um den Zustand des VHDL-Moduls zu bestimmen.

Tcl verwenden

Die letzte Methode zum Stoppen der Simulation, die ich behandeln werde, ist die Verwendung von Tcl in Kombination mit VHDL. Anstatt die Testbench aus der VHDL-Datei zu stoppen, setzen wir ein reguläres VHDL-Signal, wenn es Zeit zum Stoppen ist. Und vorher konfigurieren wir den Simulator so, dass er auf eine Änderung dieses Triggersignals wartet.

Lesen Sie auch:

Warum Sie Tcl lernen müssen

Sehen Sie sich das Beispiel unten an, das ein Signal namens stop_condition setzt wenn alle Testfälle abgeschlossen sind.

signal stop_condition : boolean;

begin

-- Replace this line with your DUT instantiation

stop_condition <= not stop_condition after 1 ms;

SEQUENCER_PROC : process

begin

-- Put your testbench logic here

-- Pause this process forever after all tests are done

wait;

end process;

Sie können jeden Testbench-Prozess, der seine Arbeit erledigt hat, mit einem einzigen Warten in den Ruhezustand versetzen -Anweisung vor dem Prozess beenden Schild. Dadurch wird ein Neustart verhindert. Der Tcl-Code zum tatsächlichen Stoppen der Simulation unterscheidet sich zwischen den Simulatoren.

In ModelSim

Wir wollen die Testbench stoppen, wenn stop_condition VHDL-Signal wird wahr . Wir können das tun, indem wir einen Rückruf in Tcl einrichten, bevor wir die VHDL-Testbench ausführen.

Laut dem ModelSim Command Reference Manual können wir das erreichen, indem wir das Tcl when verwenden Befehl. Im folgenden Tcl-Code registrieren wir einen solchen Callback und starten dann den Simulator mit run -all .

when {stop_condition} {

stop

echo "Test: OK"

}

run -all

Beachten Sie, dass der Code in den geschweiften Klammern nicht ausgeführt wird, bis der Rückruf erfolgt. Wenn der VHDL-Code die stop_condition ändert Signal auf true , hält der Simulator an und führt die beiden Zeilen aus. Im Beispiel stoppen wir die Simulation und geben „Test:OK“ an die Konsole aus. Sie könnten auch einen Exit von Tcl haben Befehl darin, der den Simulator beenden würde, genau wie das VHDL finish Verfahren.

# vsim # Start time: 22:31:11 on Jun 22,2020 # Loading std.standard # Loading work.using_tcl_tb(sim) # Test: OK # Simulation stop requested.

Die obige Auflistung zeigt die Ausgabe, die an die ModelSim-Konsole gedruckt wird, wenn die Tcl/VHDL-Testbench abgeschlossen ist. Wenn Sie es auf Ihrem Computer ausprobieren möchten, verwenden Sie das folgende Formular, um das ModelSim-Projekt mit allen Beispielen aus diesem Artikel herunterzuladen!

In Vivado

Gemäß dem Vivado Design Suite Tcl Command Reference Guide können wir einen Tcl-Callback mit der add_condition registrieren Befehl. Der folgende Code zeigt das Xilinx-Äquivalent für die zuvor besprochene ModelSim-Version.

set sim_fileset sim_1

launch_simulation -simset [get_filesets $sim_fileset]

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

run all

Der -notrace switch verhindert, dass die Codezeilen in der Callback-Funktion während ihrer Ausführung an das Terminal zurückgesendet werden. Ich ziehe es vor, das zusätzliche Durcheinander in der Konsole nicht zu haben.

Die folgende Auflistung zeigt einen Auszug aus der Simulation, die in der Vivado-Simulatorkonsole ausgeführt wird.

launch_simulation: ...

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

condition8

run all

Test: OK

Abschließende Gedanken

Wie Sie gesehen haben, gibt es viele Möglichkeiten, eine VHDL-Simulation zu beenden. Allerdings ist das einzige, das ich jemals verwende, das VHDL-2008 Finish Verfahren.

Alle Simulatoren unterstützen inzwischen VHDL-2008, und Sie müssen nicht den RTL-Code in 2008 kompilieren, sondern nur die Testbench. Das Finish Die Prozedur ist die portabelste Methode und ermöglicht es Ihnen, den Simulator zu stoppen, wenn er im GUI-Modus ausgeführt wird, oder ihn zu beenden, wenn er im Stapelmodus ausgeführt wird. Genau das Verhalten, das ich mir die meiste Zeit wünsche.

Die Tcl-Methoden haben jedoch Vorteile, die nicht Gegenstand dieses Artikels sind. Wenn Sie den Simulator im Tcl-Callback angehalten haben, können Sie viel mehr tun, als nur den Simulator anzuhalten und zu beenden. Sie können VHDL-Signale untersuchen und sogar mit Tcl manipulieren, während Sie sich im Rückruf befinden. Das ist die Verifizierung mit Tcl.

VHDL

- So erstellen Sie eine Liste von Zeichenfolgen in VHDL

- So erstellen Sie eine Tcl-gesteuerte Testbench für ein VHDL-Code-Sperrmodul

- So erstellen Sie einen PWM-Controller in VHDL

- So generieren Sie Zufallszahlen in VHDL

- Interaktive Testbench mit Tcl

- So erstellen Sie eine selbstüberprüfende Testbench

- So erstellen Sie eine verknüpfte Liste in VHDL

- So verwenden Sie eine Prozedur in einem Prozess in VHDL

- So verwenden Sie eine Funktion in VHDL

- So stoppen Sie Rost