Interaktive Testbench mit Tcl

Eine interaktive Testbench ist ein Simulatoraufbau, bei dem Eingaben für das zu testende Gerät (DUT) von einem Bediener bereitgestellt werden, während die Testbench läuft. Meistens bedeutet dies, dass Sie Befehle in die Simulatorkonsole eingeben, um dem DUT einen Stimulus zu geben.

Während Sie immer eine selbstprüfende Testbench erstellen sollten, kann eine interaktive Testbench eine schöne Ergänzung sein. Es ist einfacher, Ad-hoc-Tests mit einer interaktiven Testbench durchzuführen, als den Code der selbstprüfenden Testbench zu ändern.

Oft werden Sie im Labor Probleme entdecken, die Sie in der Testbench ausprobieren möchten. Mit einer interaktiven Testbench kann es so einfach sein, die beobachtete Eingabesequenz einzugeben, um das unerwünschte Verhalten im Simulator zu replizieren.

Tcl interagiert mit VHDL

Die meisten VHDL-Simulatoren verwenden Tcl als Konsolensprache. Die Simulatoren haben eine Reihe von herstellerspezifischen Befehlen, aber die gute Nachricht ist, dass sie wie jeder andere Tcl-Befehl behandelt werden können. Sie können Tcl zum Erstellen komplexer, meist portabler Skripte zum Verwalten und Unterstützen Ihrer VHDL-Testbenches verwenden.

VHDL-Signale von Tcl ändern

Um mit VHDL zu interagieren, müssen wir den Befehl zum Ändern eines Signalwerts finden. In ModelSim ist dies der „force“-Befehl. Wie im Befehlsreferenzdokument angegeben, lautet die Zusammenfassung für den Befehl:

force {<object_name> <value> [[@]<time_info>][, <value> [@]<time_info>]...

[-deposit | -drive | -freeze] [-cancel [@]<time_info>] [-repeat [@]<time_info>] Der Schalter, den Sie verwenden möchten, ist das Flag „-deposit“. Dies ändert den Wert des VHDL-Signals sofort, erlaubt aber einem anderen VHDL- oder Tcl-Treiber, es zu einem späteren Zeitpunkt auf etwas anderes zu ändern.

Durch Ignorieren der Optionen, die wir nicht verwenden, sieht die vereinfachte Zusammenfassung so aus:

force -deposit <signal_name> <value>

Der VHDL-Trigger

Nachdem wir nun wissen, wie VHDL-Signale von Tcl gesteuert werden, müssen wir in unserer VHDL-Testbench eine Art Empfängerprozess erstellen. Der folgende Code zeigt ein Minimalbeispiel einer solchen Testbench.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity interactive is

end interactive;

architecture sim of interactive is

-- Controlled by Tcl

signal trigger : std_logic := '0';

begin

process is

begin

wait until trigger = '1';

report "Triggered!";

end process;

end architecture;

Der Prozess wird aktiviert, wenn trigger Signal ändert sich von etwas zu '1' . Es wird "Triggered!" an die Konsole, wenn dies passiert, was es uns ermöglicht, das Konzept der Steuerung von VHDL-Prozessen von Tcl aus zu testen.

Ich habe genau das ist die ModelSim-Konsole. Die ausgegebenen Befehle sowie die Ausgabe können im folgenden Transkript eingesehen werden.

VSIM 1> run 10 ns; VSIM 2> force -deposit /trigger '1' VSIM 3> run 0 ns; # ** Note: Triggered! # Time: 10 ns Iteration: 0 Instance: /interactive VSIM 4> force -deposit /trigger '0' VSIM 5> run 10 ns;

Ich habe die Testbench nach dem Start der Simulation 10 Nanosekunden lang ausgeführt.

Dann habe ich die trigger erzwungen Signal an '1' . In der nächsten Zeile warte ich auf 0 Nanosekunden. Der Zweck besteht darin, einen Delta-Zyklus zu erstellen. Ich möchte, dass der Prozess ausgelöst wird, aber ich möchte nicht, dass Simulationszeit vergeht.

Schließlich erzwinge ich die trigger Signal zurück zu '0' bevor Sie mit der Testbench fortfahren.

Wir können sehen, dass der VHDL-Prozess nach der Zeile „run 0 ns“ aufgewacht ist und „Triggered!“ ausgedruckt hat. zur Konsole.

VHDL-Signalwerte in tcl lesen

Um Signalwerte in ModelSim auszulesen, können Sie den Befehl „Untersuchen“ verwenden. Wir können zum Beispiel den Wert von trigger lesen Signal mit diesem Befehl in der ModelSim-Konsole:

VSIM 6> examine /trigger # 0

Sie möchten den Wert einer Tcl-Variablen zuweisen, wenn Sie „examine“ in einem Skript verwenden. Versuchen wir das in der ModelSim-Konsole:

VSIM 7> set triggerVal [examine /trigger] # 0

Dann können wir die Variable zum Beispiel mit dem Tcl-Befehl „puts“ ausgeben:

VSIM 8> puts "triggerVal: $triggerVal" # triggerVal: 0

Stoppen des Simulators nach jedem Test

Der einfachste Weg, den Test lange genug laufen zu lassen, damit das DUT reagieren kann, besteht darin, den Simulator einfach für einen festen Zeitwert laufen zu lassen. Wenn das DUT beispielsweise nach zwei Taktzyklen reagieren soll und die Taktperiode 10 Nanosekunden beträgt, würden wir in unserem Tcl-Skript den Befehl „run 20 ns“ verwenden.

Wenn das DUT keine feste Reaktionszeit hat, kann eine VHDL-Assertion verwendet werden, um die Simulation zu stoppen und die Kontrolle an eine Tcl-Callback-Funktion zu übergeben. In ModelSim würde dies bedeuten, einen Haltepunkt aus Ihrem Tcl-Skript zu setzen, indem Sie den „when“-Befehl verwenden:

when [[-fast] [-id <id#>] [-label <label>] {<when_condition_expression>} {<command>}] Sie müssten auch eine „onBreak“-Callback-Funktion in Tcl definieren, die ausgeführt wird, wenn der Haltepunkt erreicht wird. Die „onBreak“-Funktion ist in der ModelSim-Befehlsreferenz spezifiziert.

Die Nachteile von Tcl-gesteuertem Testen

Die Verwendung von Testbenches, die sich stark auf Tcl-Skripte stützen, hat Nachteile. Die offensichtlichsten sind die Geschwindigkeits- und Portabilitätsprobleme.

Tcl-gesteuerte Testbenches funktionieren, indem sie den Simulator mehrmals starten und stoppen, um mit dem VHDL-Code zu interagieren. Das Starten und Stoppen der Simulation, um zwischendurch eine Tcl-Funktion auszuführen, ist zeitaufwändiger als das kontinuierliche Betreiben einer VHDL-Testbench. Während Tcl eine interpretierte Sprache ist, wird VHDL im Simulator kompiliert und läuft viel schneller als Tcl.

Während Tcl auf andere Simulatoren portierbar ist, sind die simulatorspezifischen Befehle, die Sie verwenden müssen, dies nicht. Auch wenn Sie die entsprechenden Befehle im anderen Simulator finden, funktionieren sie möglicherweise anders. Simulatoranbieter stellen ihre eigenen Regeln für die von ihnen unterstützten Befehle auf. Daher sollte eine Tcl-gesteuerte Testbench als weniger portabel angesehen werden als eine reine VHDL-Testbench.

Neuer VHDL- und FPGA-Kurs

* Ich erstelle einen neuen VHDL- und FPGA-Kurs, der ausführlich in Testbenches eintauchen wird. Sie lernen, wie Sie ein FPGA-Design von Grund auf neu erstellen. Nach Abschluss des Kurses wissen Sie, wie Sie selbstprüfende Testbenchs erstellen und den Code wiederverwenden, um eine interaktive Testbench zu erstellen.

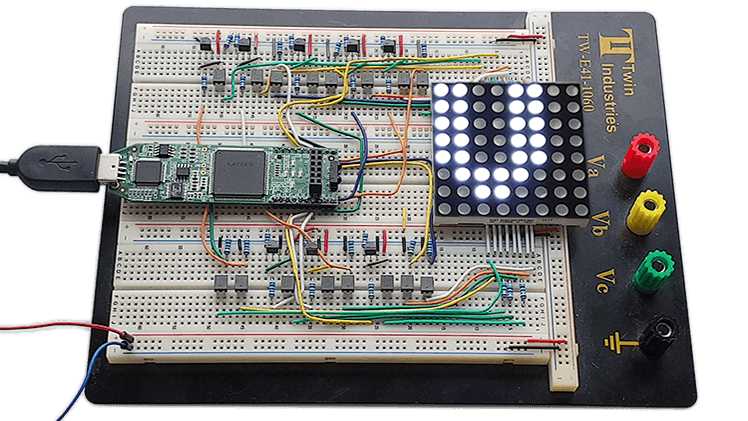

* Aktualisiert am 12. Oktober 2020: Ich habe den Kurs abgeschlossen. Klicken Sie auf das Bild unten, um mehr zu erfahren.

Das Produkt, das wir erstellen werden, ist ein Punktmatrix-LED-Controller-Modul. Wir werden das Lattice iCEstick-Entwicklungsboard für 49 US-Dollar verwenden. Am Ende setzen wir das Design auf einem Steckbrett um. Sie können auf der Tastatur Ihres Computers tippen, und die Zeichen werden auf dem vom FPGA gesteuerten Punktmatrix-LED-Bildschirm angezeigt.

Lesen Sie hier mehr über den Dot-Matrix-VHDL- und FPGA-Kurs!

Öffnet:

Noch zu entscheiden .

VHDL

- Lernprogramm - Einführung in VHDL

- Beispiele für VHDL-Konvertierungen

- Prozeduranweisung – VHDL-Beispiel

- Aufzeichnungen - VHDL-Beispiel

- Signiert vs. Unsigniert in VHDL

- C# verwenden

- So erstellen Sie eine Liste von Zeichenfolgen in VHDL

- So erstellen Sie eine selbstüberprüfende Testbench

- Interaktiver Laserprojektor mit Zigbee-Sensoren

- Eine Mühle als Drehbank verwenden