Trittfrequenz beschleunigt die SoC-Verifizierung auf Milliarden von Gates

Cadence Design Systems hat seine Emulations- und Prototyping-Systeme der nächsten Generation auf den Markt gebracht, die laut eigenen Angaben das schnellste und leistungsfähigste Pre-Silicon-Hardware-Debugging und die Software-Validierung für die Verifizierung von Milliarden-Gate-System-on-Chip-Designs (SoC) bieten.

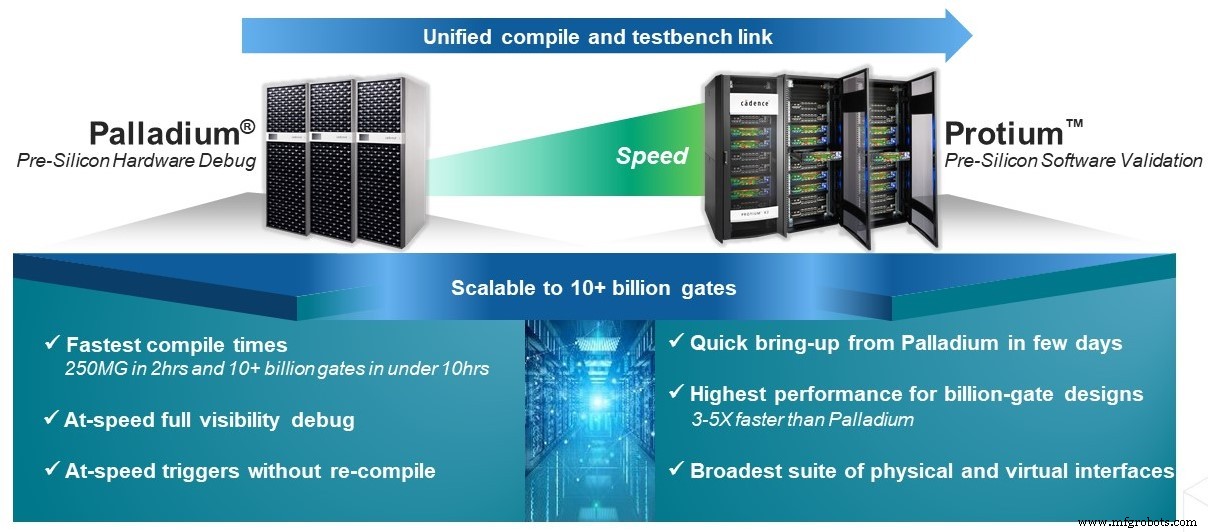

Mit einer einheitlichen Compiler-Schnittstelle sowie gemeinsamen Debug-Schnittstellen und Testbench-Inhalten bieten die neue Palladium Z2 Enterprise-Emulation und die Protium X2 Enterprise-Prototyping-Systeme Kunden eine doppelte Kapazitäts- und 1,5-fache Leistungsverbesserung gegenüber ihren Vorgängern, sodass mehr Validierungszyklen auf größeren Chips ausgeführt werden können in kürzerer Zeit. Laut Cadence bieten beide Systeme auch eine bahnbrechende modulare Compile-Technologie, mit der 10 Milliarden Gates in weniger als 10 Stunden auf dem Palladium Z2-System und in weniger als 24 Stunden auf dem Protium X2-System kompiliert werden können.

Ein Schlüssel zur Kombination Palladium Z2 / Protium X2, die Teil der breiteren Cadence-Verifizierungssuite einschließlich intelligenter Verifizierungsanwendungen sind, ist die einheitliche Compiler-Schnittstelle, was bedeutet, dass ein Design, das für Palladium kompiliert wird, auf Protium kompiliert und ausgeführt wird. Mit dem nahtlos integrierten Ablauf, vereinheitlichtem Debug, gemeinsamen virtuellen und physischen Schnittstellen und Testbench-Inhalten für alle Systeme bieten die beiden Systeme eine schnelle Designmigration und Tests von der Emulation bis zum Prototyping. Durch die skalierbare Kapazität sind sie darauf ausgelegt, die Herausforderungen zu bewältigen, denen sich diejenigen stellen müssen, die für die fortschrittlichsten Anwendungen entwickeln, einschließlich Mobil-, Verbraucher- und Hyperscale-Computing-Designs.

Paul Cunningham von Cadence sagte:„Die Vor-Silizium-Verifizierung des fortschrittlichen SoC-Designs erfordert eine Lösung mit einer Kapazität von mehreren Milliarden Gates, die sowohl höchste Leistung als auch schnelles, vorhersehbares Debuggen bietet.“ Der Senior Vice President und General Manager der System- und Verifikationsgruppe fügte hinzu:„Unser neues dynamisches Duo erfüllt diese Anforderungen mit zwei eng integrierten Systemen, der Palladium Z2-Emulation, die für schnelles, vorhersehbares Hardware-Debugging optimiert ist, und der Protium X2-Prototyping, die für höchste Leistung im Milliardenbereich optimiert ist. Gate-Software-Validierung. Wir freuen uns über das starke Kundeninteresse und freuen uns darauf, mit ihnen zusammenzuarbeiten, um diese neuen Systeme zu nutzen, um den höchsten Verifizierungsdurchsatz bei ihren Designs zu erzielen.“

Erste Kunden haben sich zu den Vorteilen des gemeinsamen Front-End-Verifizierungsdurchsatzes geäußert. Narendra Konda, Senior Director für Hardware-Engineering bei Nvidia, sagte:„Die Komplexität unserer High-End-Grafik- und Hyperscale-Designs nimmt mit jeder Generation zu, während sich unsere Time-to-Market-Zeitpläne verkürzen. Mit dem gemeinsamen Front-End-Flow der Cadence Palladium Z2- und Protium X2-Systeme optimieren wir die Arbeitslastverteilung zwischen Verifikation, Validierung und Pre-Silicon-Software-Bring-Up. Mit der doppelten nutzbaren Kapazität, einem um 50 % höheren Durchsatz und einer schnelleren Durchlaufzeit des modularen Compilers können wir unsere anspruchsvollsten GPU- und SoC-Designs umfassend und termingerecht validieren.“

Unterdessen sagte Tran Nguyen, Senior Director of Design Services bei Arm:„Best-in-Class-Emulationen sind der Schlüssel zu unserem Erfolg, und Arm nutzt die Emulation ausgiebig zusammen mit der Simulation auf Arm-basierten Servern, um den höchsten Verifizierungsdurchsatz zu erzielen. Mit dem neuen Cadence Palladium Z2-System haben wir bei unseren neuesten Designs eine bis zu 50-prozentige Leistungssteigerung und eine zweifache Verbesserung der Kapazität festgestellt /P>

Wie ihre Vorgänger sind Palladium Z2 und Protium X2 in einer Standard-Rack-Konfiguration aufgebaut und für die Installation in einem Rechenzentrum und den Zugriff vom Schreibtisch der Ingenieure vorgesehen. Beide können viele Designs gleichzeitig verarbeiten, je nachdem, wie viel Kapazität die einzelnen Designs tatsächlich benötigen. Die Granularität, die geteilt werden kann, liegt beim einzelnen Chip innerhalb des Systems, und beide Systeme skalieren so, dass jeder einzelne Chip parallel für ein anderes Design verwendet werden kann:

- Palladium Z2 skaliert von einem Chip mit 8 Millionen Gates und kann bis zu 144 gleichzeitige Jobs pro Rack haben. Oder es kann auf 18,4 Milliarden Gates pro Rack skaliert werden, wenn das gesamte Rack für ein einziges Design verwendet wird. Darüber hinaus können bis zu 12 Racks für ein einziges Design verwendet und auf 18,4 Milliarden Gates skaliert werden.

- Ein volles Rack von Protium X2 enthält 60 FPGAs und wir haben Kunden, die 60 Jobs parallel ausführen. Da ein einzelner FPGA in Protium X2 ~40 Millionen Gates enthält, sind dies keine kleinen Designs. Das gesamte Rack kann für ein einziges Design von 2,4 Milliarden Gates verwendet werden. Oder, wie bei Palladium Z2, kann ein großes Design über mehrere Racks weiter skaliert werden.

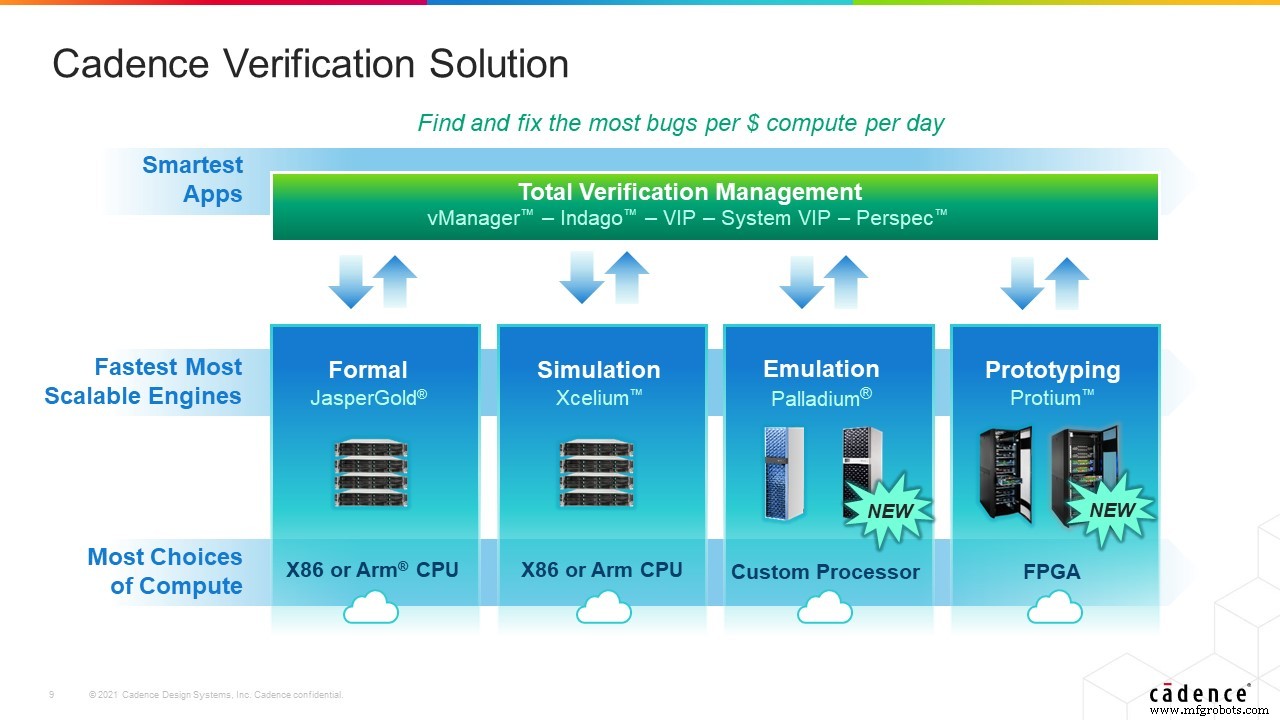

Der vollständige Ablauf der Cadence-Verifizierung, einschließlich Palladium Z2-Emulation, Protium X2-Prototyping, Xcelium-Logiksimulation, der formalen Verifizierungsplattform JasperGold und der Cadence-Suite intelligenter Verifizierungsanwendungen, liefert laut dem Unternehmen den höchsten Verifizierungsdurchsatz von Fehlern pro Dollar und Tag.

Eingebettet

- Zahlensysteme

- Gate-Universalität

- Stromsignalsysteme

- Warum ein Bare-Metal-Entwickler auf Betriebssysteme umgestiegen ist

- Cadence kündigt Cloud Passport-Partnerprogramm an

- SoC steigert die Leistung von Wearables

- Smart Sensor Board beschleunigt die Entwicklung von Edge-KI

- Modellierung auf Gatterebene

- Hitachi erwirbt Robotik-Systemintegrator JR Automation für 1,4 Milliarden US-Dollar

- ABB beansprucht einen 20-prozentigen Anteil am 14-Milliarden-Dollar-Markt für verteilte Steuerungssysteme