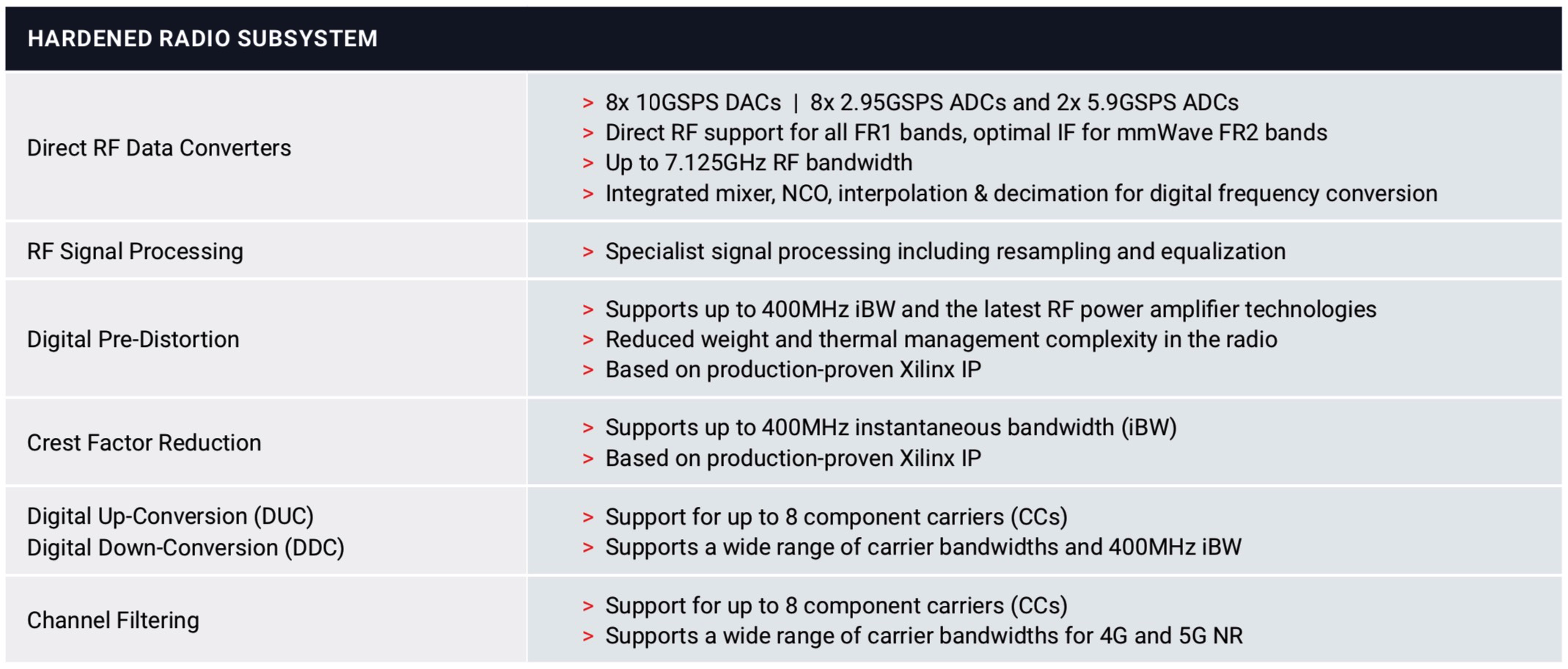

Xilinx steigert die RFSoC-Leistung mit digitaler Front-End-Hard-IP für 5G-Funkgeräte

Xilinx hat sein digitales Frontend-Gerät (DFE) Zynq RFSoC angekündigt, das für 5G New Radio (NR)-Bereitstellungen entwickelt wurde. Aufbauend auf der Zynq-UltraScale-Architektur des Unternehmens erweitert das Zynq-RFSoC-DFE die Xilinx-RFSoC-Familie um eine Hard-IP-Implementierung der rechenintensiven Funktionen, die erforderlich sind, um 5G NR sowie Legacy 4G in aufstrebenden 5G-Funkeinheiten (RUs) effektiv zu unterstützen.

Bei all seinem Potenzial stellt 5G Entwickler von 5G-Infrastrukturen vor zahlreiche Herausforderungen. Während Designer von Smartphones und anderen Mobilgeräten aus einem wachsenden Angebot an 5G-Chipsätzen wählen können, erfordern die vielfältigen Anforderungen, die mit dem breiten Leistungsspektrum von 5G verbunden sind, in der Regel spezialisiertere Lösungen.

Während 3GPP Release 15 mit seinem Fokus auf verbessertem mobilen Breitband (eMBB) den Grundstein für 5G NR legte, erweiterte Release 16 Anfang dieses Jahres 5G zu neuen Arten von Kommunikationsdiensten rund um Ultra-Zuverlässig Low-Latency Communication (URLLC) und massive Machine Type Communication (mMTC). URLLC adressiert die Notwendigkeit einer minimalen Reaktionsverzögerung, die für kritische Anwendungen wie industrielle Automatisierung, Fernchirurgie und Transport erforderlich ist, während mMTC groß angelegte Bereitstellungen von intelligenten Geräten mit hoher Dichte in Anwendungen wie intelligenten Städten und intelligenten Fabriken unterstützt. Zukünftige 3GPP-Releases werden 5G weiterhin um Funktionen wie NR MIMO (Multiple-Input and Multiple-Output), dynamische Spektrumsteilung, URLLC-Verbesserungen und andere in Release 17 sowie erweiterte Unterstützung für bestimmte Anwendungsbereiche in Release 18 erweitern.

Mit 5G-Funktionen wie Network Function Virtualization (NFV) und Network Slicing können Anbieter von 5G-Lösungen spezialisierte Netzwerke bereitstellen, die in der Lage sind, die für jede Anwendung und jeden Kunden erforderliche einzigartige Kombination von Diensten bereitzustellen. Um das Versprechen einer umfassenden Flexibilität von 5G-Netzen zu erfüllen, hängt jedoch die Verfügbarkeit von Geräten ab, die eine geeignete Kombination aus Leistung und Flexibilität sowie Energieeffizienz bieten.

"Angesichts der sich entwickelnden Marktanforderungen rund um 5G müssen integrierte HF-Lösungen anpassungsfähig sein, um zukünftige Standards zu erfüllen", sagte Liam Madden, Executive Vice President und General Manager der Wired and Wireless Group von Xilinx. , in einer Stellungnahme. „Zynq RFSoC DFE bietet das optimale Gleichgewicht zwischen dieser Anpassungsfähigkeit und festem Funktions-IP.“

Das Zynq RFSoC DFE bettet Hard-IP ein, das die Kernfunktionen implementiert, die in 5G-RU-Signalpfaden erforderlich sind (Abbildung 1).

klicken Sie für das Bild in voller Größe

Abbildung 1. Das Zynq RFSoC DFE Hard IP unterstützt eine breite Palette von Verarbeitungsfunktionen, die für 5G NR sowie für ältere 4G-Funkgeräte erforderlich sind. (Quelle:Xilinx)

Da der Hard-IP-DFE-Kern weniger Platz benötigt als die entsprechende Soft-IP-Implementierung im früheren Zynq-RFSoC-Gen-3-Gerät, kann das neue Gerät mehr DFE-Kerne unterstützen, wodurch die DFE-Rechenleistung gesteigert wird und geringerer Stromverbrauch im Vergleich zum früheren Gerät. Infolgedessen kann das Zynq-RFSoC-DFE laut Xilinx mindestens die doppelte DFE-Verarbeitungsleistung pro Watt im Vergleich zu einem voll ausgelasteten Zynq-RFSoC-Gen-3-Gerät erreichen.

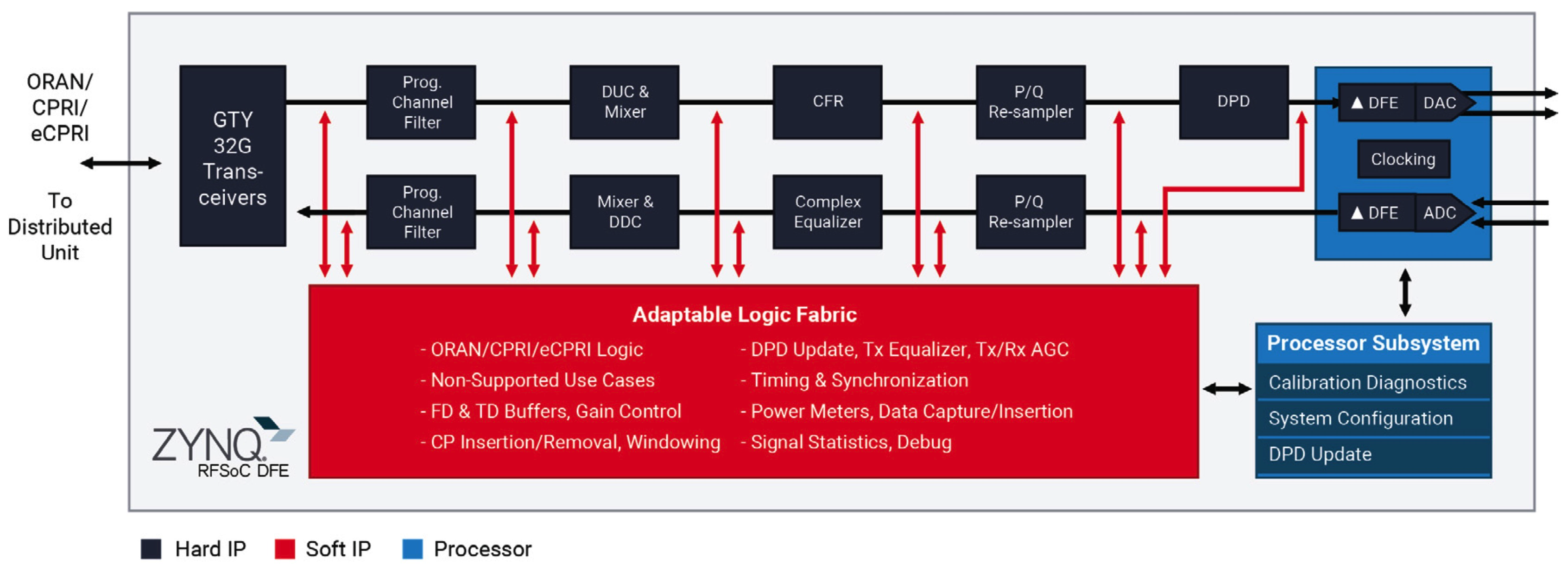

Gleichzeitig können Entwickler den Signalpfad modifizieren, harte IP-Blöcke umgehen oder ihre eigene, in die Logikstruktur implementierte Funktionalität einfügen (Abbildung 2).

klicken Sie für das Bild in voller Größe

Abbildung 2. Die funktionale Architektur des Zynq RFSoC DFE kombiniert Hard-IP, Logik-Fabric und Prozessor-Subsystem. (Quelle:Xilinx)

Zynq RFSoC DFE-Designdokumentation und -Support stehen Early-Access-Kunden zur Verfügung, Auslieferungen werden im ersten Halbjahr 2021 erwartet. Weitere Informationen finden Sie auf der Xilinx-RFSoC-DFE-Produktseite. Xilinx stellt im Rahmen seiner virtuellen 5G-Veranstaltung vom 18. bis 19. November auch weitere Informationen zu dem Gerät bereit.

Eingebettet

- Xilinx erweitert das Zynq UltraScale+ RFSoC-Portfolio um die volle Unterstützung des Sub-6-GHz-Spektrums

- Trittfrequenz:Tensilica ConnX B20 DSP steigert die Leistung für 5G-Kommunikation um das bis zu 30-fache

- Renesas:RX-Lösung für funktionale Sicherheit mit SIL3-Softwarezertifizierung für Industrieanlagen

- Renesas:RX72M-MCUs mit EtherCAT-Unterstützung für industrielle Anwendungen

- ST:STM32H7-MCUs kombinieren Dual-Core-Leistung mit umfassender Funktionsintegration

- SoC steigert die Leistung von Wearables

- Lanner:Virtualisierungsoptimierte Lösung mit Mehrkernprozessor

- Portwell:Mini-ITX powered by Intel Core i Familie mit bis zu sechs Kernen Leistung

- Globale Indikatoren für Wartung, Verfügbarkeitsleistung

- Blog:Medizinische Wearables mit großer Leistung