Hochleistungsverbindungen mit mehreren PCIe-Generationen aufbauen

PCI Express und der Hunger nach Bandbreite

Als Mittel zur Verbindung von Computern, eingebetteten und benutzerdefinierten Hostprozessoren mit „Endpunkt“-Peripheriegeräten wie Ethernet-Ports, USB-Ports, Grafikkarten und Speichergeräten ist PCI Express® (PCIe®) zum Referenz-High-Performance-Interconnect geworden. PCIe nutzt die serielle Hochgeschwindigkeitskommunikation und bietet effiziente Punkt-zu-Punkt-Konnektivität und – durch Erhöhung der Kanalanzahl und Signalisierungsrate – skalierbare Schnittstellenbandbreite.

Die PCIe 1.0-Spezifikation wurde 2002 veröffentlicht und arbeitet mit 2,5 Giga-Transfers pro Sekunde (GT/s), was einer gesamten x16-Schnittstellenbandbreite von 8 GByte/s entspricht. Die Bandbreite wurde anschließend im Jahr 2006 mit der Einführung der PCIe 2.0-Spezifikationen der zweiten Generation verdoppelt und erneut im Jahr 2010, als PCIe 3.0 die Bandbreite auf 32 GByte/s erhöhte, um die ständig steigenden Anforderungen führender zeitgenössischer Anwendungen zu erfüllen, darunter High-End-PCs, Spiele, Unternehmens-Computing und -Netzwerke.

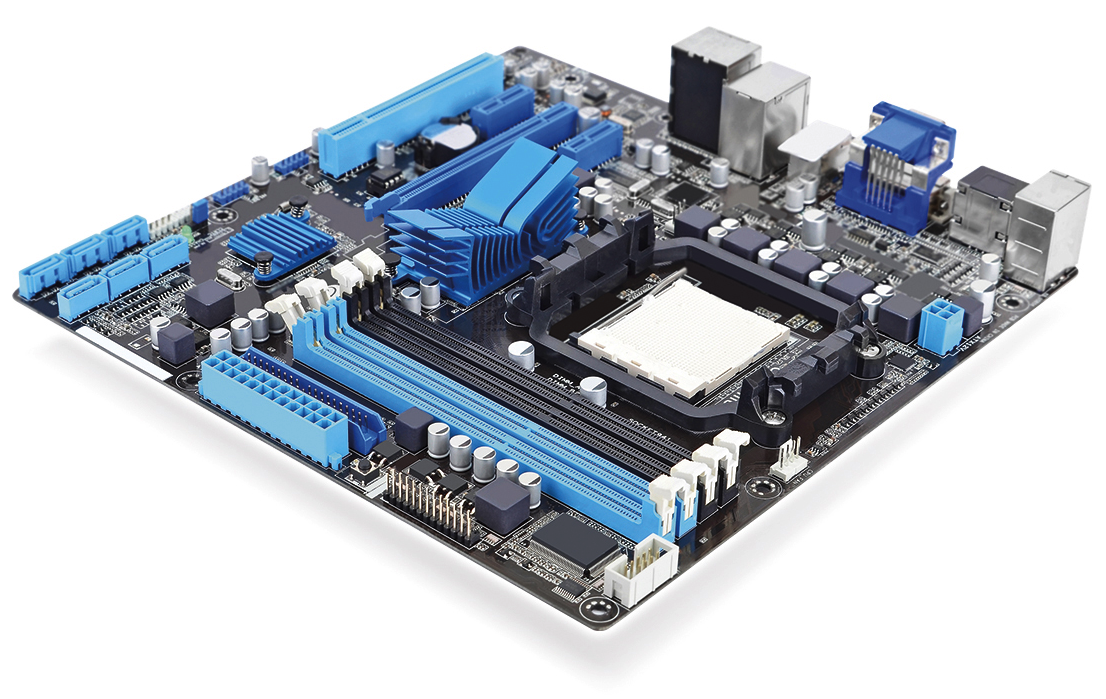

PCI Express hat sich zum Referenz-High-Performance-Interconnect für eine Vielzahl von Systemdesigns entwickelt.

(Quelle:Diodes Inc.)

In jüngerer Zeit hat die rasche Verbreitung von Cloud-basierten Diensten wie Social Media und Video-Streaming neue und anspruchsvollere Anforderungen an die Hochgeschwindigkeitskonnektivität in großen Rechenzentren gestellt.

Jetzt, da die IoT-Ära Einzug hält, werden vernetzte Sensoren, die in intelligenten Städten und Infrastrukturen, intelligenten Fabriken und anderen Industrieanlagen, Gewerbe- und Wohngebäuden sowie Wearables für Fitness- und medizinisches Tracking installiert sind, riesige Datenmengen für Hyperscale-Rechenzentren generieren, um erfassen, speichern, verarbeiten und analysieren. Diese Kräfte treiben die Nachfrage nach den nächsten PCIe-Generationen an, um Rechenzentrumsserver effizient mit Hochgeschwindigkeits-Ethernet, Network Attached Storage und KI-Beschleunigern zu verbinden.

Vernetzte Autos werden die Datenlast weiter erhöhen und den Echtzeitdruck erhöhen, um ein höheres Maß an autonomem Fahren und letztendlich vollständig selbstfahrende Fahrzeuge zu ermöglichen. Hinter den Rechenzentren ist das Training neuronaler Netze für KI-Inferenz eine rechenintensive Aufgabe, die Engpässe in der peripheren Kommunikation deutlich aufdeckt.

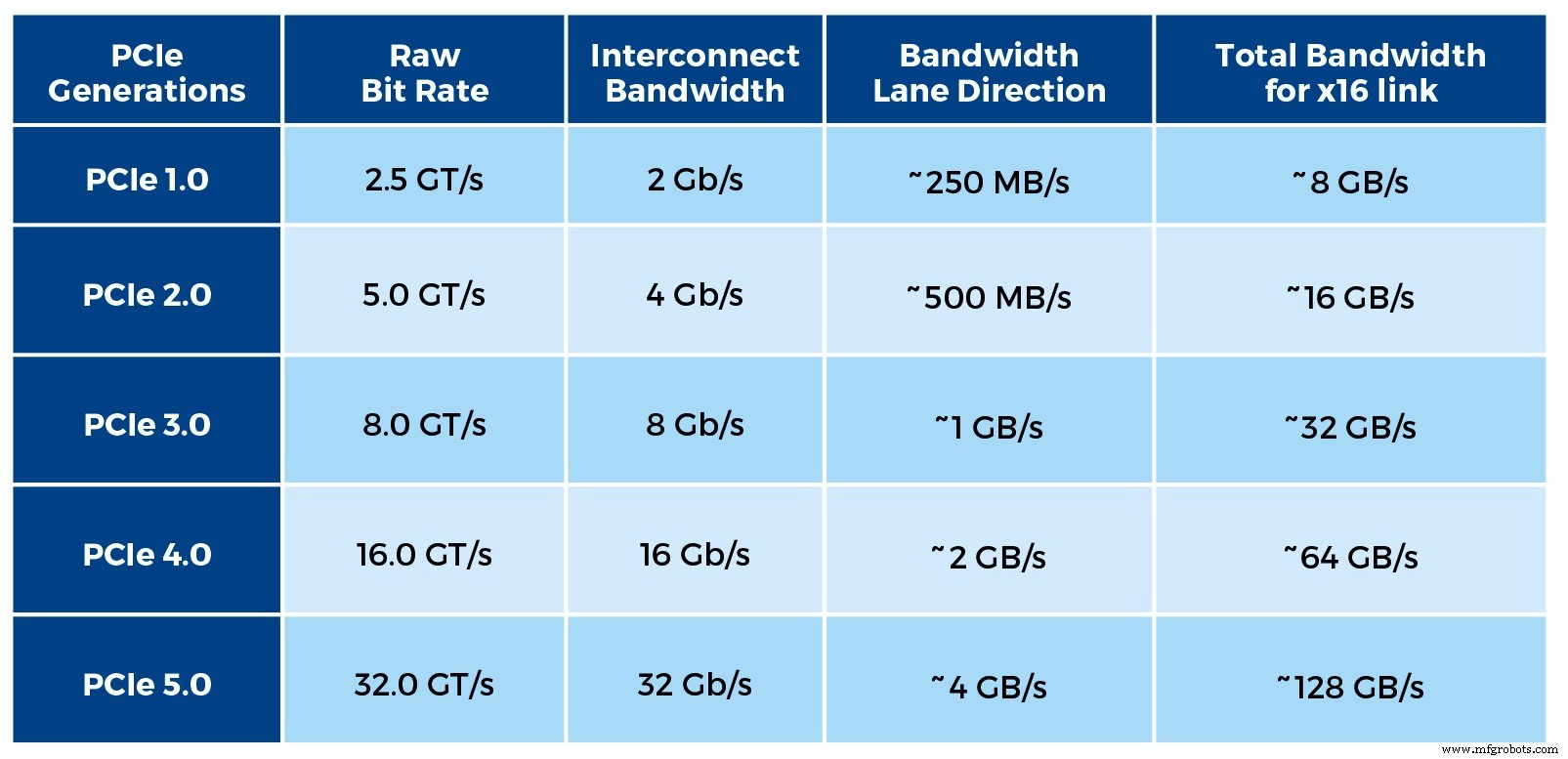

Da diese verschiedenen Faktoren nun ins Spiel kommen, ist die Zeit für PCIe reif, wieder voranzukommen. PCIe 4.0, angekündigt im Jahr 2017, folgte schnell mit der Veröffentlichung von PCIe 5.0 im Jahr 2019. Abbildung 1 zeigt die Gesamtgeschwindigkeiten, die von jeder PCIe-Version geboten werden.

Abbildung 1:Von PCIe-Versionen gebotene Gesamtgeschwindigkeiten (Quelle:Diodes Inc.)

PCIe 5.0 wird voraussichtlich weit verbreitet eingesetzt werden, da führende Rechenzentren den Übergang von 100-Gb-Ethernet auf die neueste 400-Gb-Spezifikation vollziehen. In der Praxis hat die Erhöhung der PCIe-Bandbreite mehr oder weniger mit den Fortschritten bei den Ethernet-Geschwindigkeiten Schritt gehalten, idealerweise wird ein Gleichgewicht zwischen den beiden Standards beibehalten, um Leistungsengpässe zu vermeiden.

„Legacy“-PCI-Standards bleiben aktuell

Mit dem Beginn der Markteinführung von PCIe 5.0-Produkten und der jüngsten Ankündigung der PCI Special Interest Group (PCI-SIG), dass mit der Arbeit an der nächsten Generation, PCIe 6.0, begonnen wurde, die 2021 fertiggestellt werden soll, ist PCIe das Protokoll der Wahl für Leistung -hungrige periphere Kommunikation auf absehbare Zeit.

Gleichzeitig ist die Abwärtskompatibilität eine der wichtigsten Stärken der PCIe-Reihe. Da es kein Ablaufdatum für PCIe-Spezifikationen gibt, können mehrere Generationen auf dem Markt und sogar in derselben Anwendung nebeneinander existieren. Dies ist ein Vorteil für Systemdesigner:Während sukzessive neue PCIe-Generationen auftauchen, um den zunehmend bandbreitenhungrigen Anforderungen gerecht zu werden, bieten frühere Iterationen weiterhin Wert in einer Vielzahl von Szenarien wie Personal Computing, Gaming und einigen Unternehmens-Computing- und Netzwerkanwendungen.

Implementierungsherausforderungen lösen

Die Abwärtskompatibilität zwischen den verschiedenen PCIe-Generationen ermöglicht es Systemen, mit minimalen Designänderungen von höheren Übertragungsgeschwindigkeiten zu profitieren, wenn neues Silizium verfügbar wird. Andererseits üben steigende Signalgeschwindigkeiten zusätzlichen Druck auf die Signalmargen aus und können die Designkomplexität erhöhen. Darüber hinaus besteht ein klarer Bedarf an Lösungen, die das Bridging von und zu PCIe ermöglichen, nicht nur zwischen Legacy-Schnittstellen, sondern auch anderen Schnittstellen wie USB- oder Grafikports.

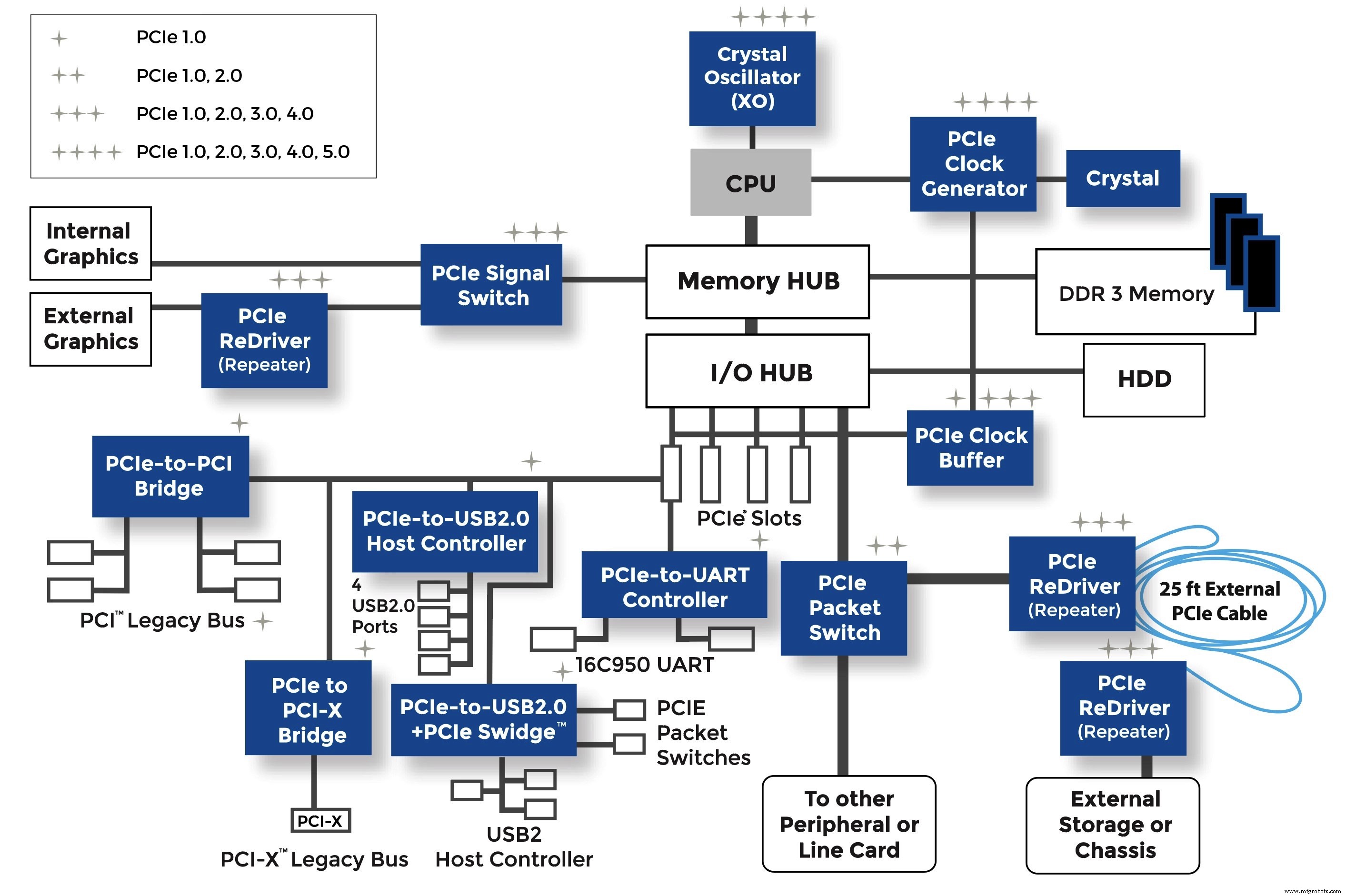

Um diese Herausforderungen zu bewältigen, benötigen Designer Zugriff auf Geräte, die verschiedene PCIe-Generationen unterstützen, wie die in Abbildung 2 gezeigten Taktgeneratoren, Taktpuffer, Controller, Paketschalter/Bridges, ReDriver™-Chips und Hochgeschwindigkeits-Multiplexer.

Klicken für größeres Bild

Abbildung 2:Ein Beispiel für die von Diodes Inc. erhältlichen PCIe-Lösungen (Quelle:Diodes Inc.)

ReDriver-Chips können eine kostengünstige und bequeme Lösung zur Verbesserung der Signalintegrität in Hochgeschwindigkeitssystemen darstellen. Unter Verwendung von Techniken wie Entzerrung und Preemphasis mit einem Ausgangstreiber, der minimale Latenzzeiten einführt, kompensiert der ReDriver Übertragungsleitungsverluste, um den Signalspielraum wiederherzustellen und Jitter zu minimieren, um eine niedrige Bitfehlerrate am Empfänger zu gewährleisten. Im Vergleich zu einem Retimer, der zusätzliche Funktionen wie Takt- und Datenwiederherstellung integriert, führt ein ReDriver zu einer geringen Verzögerung und ist relativ kostengünstig und einfach zu implementieren. Abbildung 2 zeigt, wie ein PCIe-ReDriver verwendet werden kann, wenn Signale über eine längere Leiterplattenspur geleitet werden müssen, z. B. zu einer externen Grafikkarte oder über Kabel zu einem externen Speicher. Diese ReDriver sind vollständig abwärtskompatibel und unterstützen alle vorherigen PCIe-Generationen.

Bridges und Switches erfüllen die Anforderungen an eine Schnittstelle zwischen Host- und Endpunktgeräten verschiedener Typen. Eine Paketbrücke stellt typischerweise eine Schnittstelle zwischen zwei Schichten im OSI-Referenzmodell oder zwischen zwei Protokollen bereit. Abbildung 2 zeigt auch, wie eine Bridge verwendet werden kann, um eine Verbindung zwischen PCIe und älteren PCI-Standards, einschließlich PCI-X, oder mit USB-Ports oder einer UART-Bus-Schnittstelle herzustellen. Paket-Switches sind Multiport-/Multilane-Geräte, die normalerweise verwendet werden, um einen einzelnen Root-Komplex auf mehrere Ports mit mehreren Lanes zu erweitern, um auf andere Peer-Systeme wie ein Peripheriegerät oder eine Linecard zuzugreifen.

Neben einzelnen Packet Bridges und Switches mit verschiedenen Portkonfigurationen und Übersetzungsfähigkeiten werden die Funktionalitäten eines PCIe Packet Switch und einer PCIe-to-USB2.0 Bridge in Geräten wie dem PI7C9X442SL PCI Express-to-USB 2.0 'Swidge . von Diodes Incorporated kombiniert '. Dieses multifunktionale Gerät kann von einem PCIe-x1-Upstream-Port auf zwei x1-Downstream- und vier USB-2.0-Ports auffächern und ermöglicht dem Hostprozessor des Systems, gleichzeitig auf mehrere PCIe- und USB-Geräte zuzugreifen.

Unternehmen wie Diodes Inc. können ein Portfolio passiver bidirektionaler PCIe 1.0-, PCIe 2.0- oder PCIe 3.0-Signalmultiplexer/-demultiplexer anbieten, um eine einzelne PCIe-Lane mit mehreren Lanes zur Bandbreitenerweiterung für Grafik oder Berechnungen zu verbinden. Diese Geräte können auch verwendet werden, um Verbindungen über eine einzige Multiprotokollschnittstelle zu ermöglichen.

Taktpuffer können normalerweise ein einzelnes Referenzsignal als Eingang verwenden und mehrere Ausgänge für eine breitere Verteilung auf einer Leiterplatte erzeugen. Taktpuffer-ICs sind in einer Vielzahl von Konfigurationen erhältlich und Diodes bietet ein proprietäres PLL-Design, das sicherstellt, dass Jitter innerhalb der PCIe-Anforderungen bleibt. Taktgeneratoren können ein Taktsignal mit einer bestimmten Frequenz mit sehr geringem Ausgangsjitter erzeugen, wodurch sie sowohl für PCIe als auch für andere Systemtakte geeignet sind. Designer finden eine breite Palette geeigneter Geräte wie die 1,8-V-PI6CG18xxx- und 1,5-V-PI6CG15xxx-PCIe-4.0-Taktgeneratoren und -Puffer in 2-, 4- und 8-Kanal-Konfigurationen, die mit allen vorherigen PCIe-Generationen kompatibel sind. Durch die Integration von Abschlüssen auf dem Chip sparen diese Geräte vier externe Widerstände pro Ausgang und trimmen bis zu 32 Komponenten aus der Stückliste.

Schlussfolgerung

PCIe ist die ideale Hochleistungsverbindung für Anwendungen von Embedded- und Desktop-Computing bis hin zu Konnektivität für Rechenzentren mit hoher Bandbreite und neuronalem Netzwerktraining. Designer können die lange Nutzungsdauer früherer PCIe-Standards mit Abwärtskompatibilität zwischen Legacy- und späteren Generationsspezifikationen nutzen, um verschiedene Systemanforderungen kostengünstig zu erfüllen. Mit dem Zugriff auf ein Geräteportfolio mit Funktionen wie Bridges, Buffer, ReDrivers, Switches und Mux/Demux-ICs können Designer effiziente Lösungen für anspruchsvolle Anwendungen liefern.

Eingebettet

- Flüssige additive Fertigung:Erstellen von 3D-Objekten mit Flüssigkeit

- Erstellen hybrider Blockchain-/Cloud-Anwendungen mit Ethereum und Google

- Erstellen serverloser mobiler Anwendungen mit React Native und AWS

- TECHWAY:Kintex-7 FPGA PCIe-Plattform zur Steigerung der Datenratenleistung mit 12 HSS-Links

- Roboter bauen mit Raspberry Pi und Python

- Einen Segway mit Raspberry Pi bauen

- Nexam versorgt Diab mit eigenschaftenverbesserndem Nexamite für Hochleistungs-PET-Schaum

- Hochleistungsfähige technische Harzverbindungen mit Recyclinganteil

- Wie IoT bei HLK-Big Data helfen kann:Teil 2

- Aufbau der Mitarbeitererfahrung der Zukunft mit intelligenter Automatisierung