Asynchrone Reset-Synchronisation und -Verteilung – ASICs und FPGAs

Ein Mangel an Koordination zwischen asynchronen Resets und synchronen Logiktakten führt zu zeitweiligen Ausfällen beim Einschalten. In dieser Artikelserie diskutieren wir die Anforderungen und Herausforderungen des asynchronen Resets und erkunden fortschrittliche Lösungen für ASIC- und FPGA-Designs.

Asynchrone Rücksetzungen werden traditionell in VLSI-Designs verwendet, um synchrone Schaltungen nach dem Einschalten in einen bekannten Zustand zu bringen. Der asynchrone Reset-Freigabevorgang muss mit dem synchronen Logiktaktsignal koordiniert werden, um Synchronisationsfehler aufgrund einer möglichen Konkurrenz zwischen dem Reset und dem Takt zu beseitigen. Ein Mangel an einer solchen Koordination führt zu zeitweiligen Ausfällen beim Einschalten. Das Problem verschlimmert sich, wenn große Domänendesigns mit mehreren Takten in Betracht gezogen werden. Zusätzlich zu den Synchronisationsproblemen ist die Verteilung eines asynchronen Resets auf Millionen von Flip-Flops eine Herausforderung, die ähnliche Techniken wie CTS (Clock Tree Synthesis) erfordert und ähnliche Flächen- und Routing-Ressourcen erfordert.

Die Anforderungen und Herausforderungen des asynchronen Zurücksetzens werden überprüft, wobei der Schwerpunkt auf Synchronisations- und Verteilungsproblemen liegt. Die Nachteile klassischer Lösungen zur Reset-Synchronisation (Reset-Tree-Source-Synchronisation) und Verteilung (Reset-Tree-Synthese) werden diskutiert. Es werden fortschrittliche Lösungen für eine schnellere und einfachere Timing-Konvergenz und eine zuverlässigere Reset-Synchronisation und -Verteilung vorgestellt. Unterschiedliche Ansätze für ASIC- und FPGA-Designs werden detailliert beschrieben.

Teil 1 beschreibt die Probleme im Zusammenhang mit asynchronen Zurücksetzungen und skizziert Lösungsansätze für diese Probleme. Teil 2 (dieser Artikel) beschreibt zusätzliche Lösungen für das korrekte asynchrone Zurücksetzen in ASIC und FPGA. Einige nützliche Sonderfälle werden in Teil 3 besprochen.

2. Konvergenztechniken für asynchrones Reset-Timing

Eines der Hauptprobleme, die in Teil 1 diskutiert wurden, war die Komplexität der Reset-Freigabe für große Designs (mit einem Reset-Verteilungsnetzwerk mit hoher Latenz), insbesondere wenn ein kurzer Taktzyklus verwendet wird. Die Timing-Konvergenz basierend auf der Standard-STA-Optimierung führt zu einem teuren Design und ist in einigen Fällen sogar unmöglich. Hier diskutieren wir zwei Techniken, die dieses Zeitproblem mildern. Beide Techniken sind für ASIC- und FPGA-Designs anwendbar.

2.1. Asynchrones Reset-Pipelining

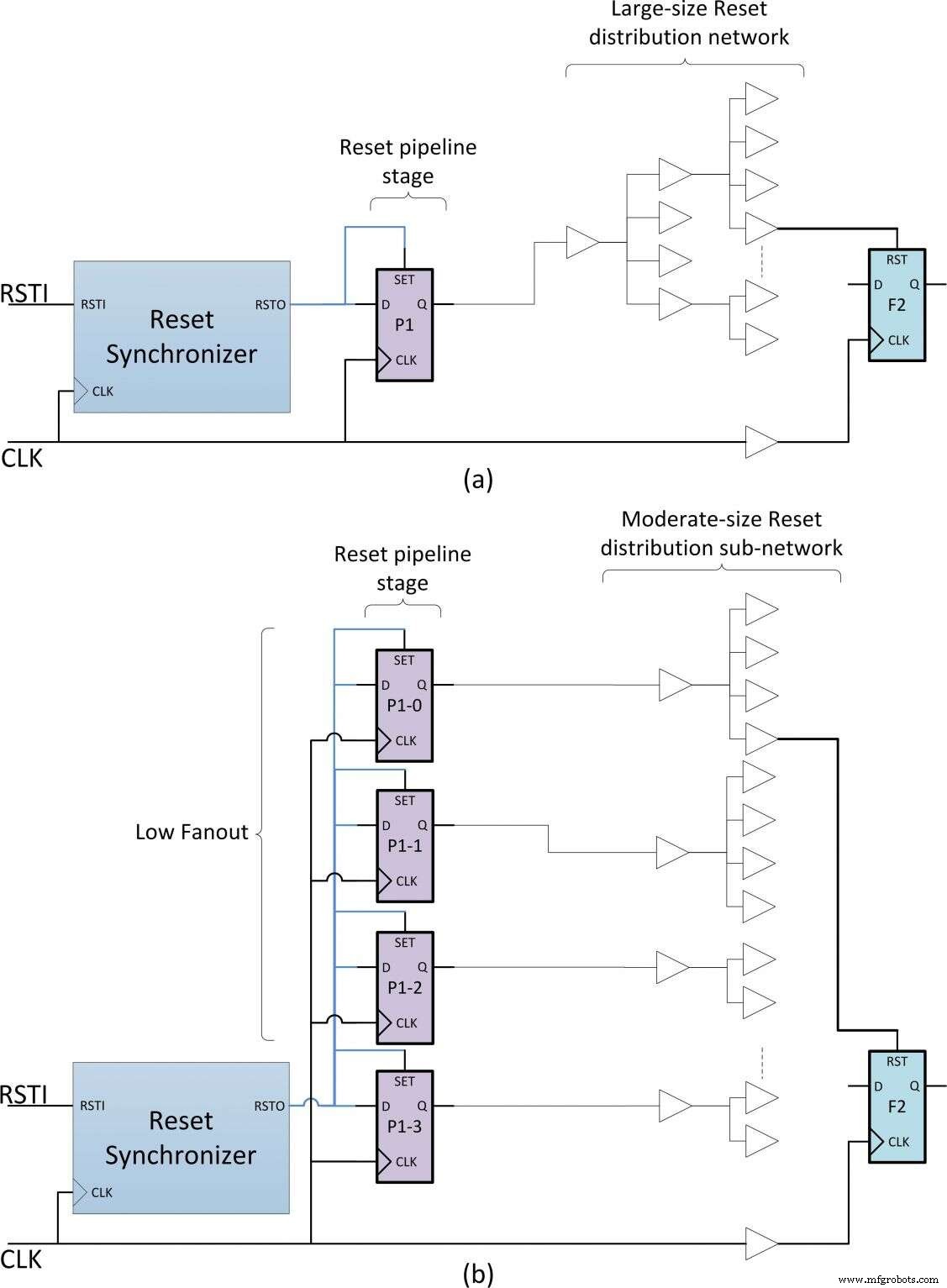

Eine Möglichkeit, mit dem Timing-Problem der asynchronen Reset-Freigabe umzugehen, besteht darin, die Reset-Release-Latenz gegen ein entspannteres Timing einzutauschen. Dies kann durch Pipelining des Reset-Baums auf folgende Weise erreicht werden. Nach jedem Synchronisierer ist eine zusätzliche asynchron eingestellte Flip-Flop-Stufe P1 auf der Rücksetzleitung enthalten (Fig. 6a). Sowohl der SET- als auch der D-Eingang des Flip-Flops sind mit dem aktiven High-Reset-RSTO verbunden, der vom Reset-Synchronizer kommt. Bei der RSTO-Version werden die Setup- und Haltebedingungen für P1 D- und SET-Eingänge erfüllt, da sie als reguläre synchrone Pfade eingeschränkt sind.

Klicken für größeres Bild

Abbildung 6:Asynchroner Reset mit Pipelining (Quelle:vSync Circuits)

Die Funktionsweise des neuen Schemas ähnelt der in Teil 1 (Abbildung 3d) beschriebenen regulären Vorgehensweise, mit Ausnahme einer zusätzlichen Latenzzeit bei einem einzelnen Zyklus bei der Reset-Freigabe. Die durch diese Technik verursachte höhere Reset-Latenz ist normalerweise für die meisten Anwendungen akzeptabel, da sie nur einmal pro Einschalten auftritt.

Ein komplementärer Teil dieser Technik deckt Entwurfsbeschränkungen ab. Während die Synchronisierer-Flipflops gegen Duplizierung beschränkt werden müssen, um Rekonvergenzpfadprobleme zu verhindern, wie in Teil 1 beschrieben, unterliegt die Pipeline-Stufe P1 der MAX_FANOUT-Beschränkung. Ein Beispiel für eine maximale Fanout-Beschränkung ist in Abbildung 6b gezeigt. Das P1-Flip-Flop wird automatisch durch das Synthesetool dupliziert, wodurch vier Subnetzwerke für die Reset-Verteilung erstellt werden. Jedes Subnetzwerk hat eine geringere Latenz als das ursprüngliche Netzwerk und erfüllt die Timing-Anforderungen für die Reset-Freigabe. Darüber hinaus erreicht der Ausgang des Reset-Synchronizers problemlos einen Fanout von acht.

Diese asynchrone Reset-Pipelining-Technik ist für jede Designgröße skalierbar und erfordert keine Änderungen, wenn sich das Design ändert, da das Synthesetool automatisch die P1-Stufe dupliziert und das Reset-Subnetz mit moderater Latenz begrenzt hält. Der duplizierte Fanout der P1-Stufe für den Synchronisiererausgang ist normalerweise klein und verursacht keine Timing-Verletzungen. Wenn jedoch eine einzelne Pipeline-Stufe nicht zu einer zeitlichen Konvergenz führt, können zusätzliche Pipeline-Stufen P2 – PN eingeschlossen und mit unterschiedlichen MAX_FANOUT-Beschränkungen eingeschränkt werden.

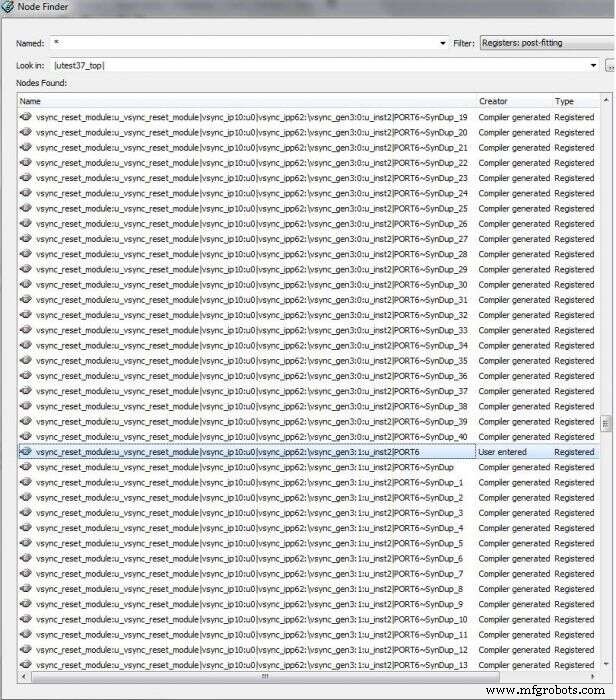

Ein Beispiel für diese Technik, die auf ein reales Design angewendet wird, ist in Abbildung 7 gezeigt. Das P1-Stufenregister mit dem Namen PORT6 wurde automatisch etwa 40-mal durch das Synthesewerkzeug [6] dupliziert, um die MAX_FANOUT-Beschränkung zu erfüllen. Jedes der 40 Subnetze hat das Timing für seinen lokalen Fanout eingehalten.

Klicken für größeres Bild

Abbildung 7:Beispiel für asynchrones Reset-Pipelining (Quelle:vSync Circuits)

Eingebettet

- Strukturen und Klassen in C++

- Postfächer:Einführung und grundlegende Dienste

- Semaphoren:Einführung und grundlegende Dienste

- Anvo-Systems und Mouser unterzeichnen Vertriebsvereinbarung

- Mouser und Inventek Systems geben globale Vertriebsvereinbarung bekannt

- Rutronik und AP Memory unterzeichnen globale Vertriebsvereinbarung

- Getrennte Vertriebs- und Compoundiergeschäfte von Albis Plastics

- Die Kunst und Wissenschaft der Standortauswahl

- Sechs Möglichkeiten zur Emissionsreduzierung bei Lagerung und Vertrieb

- RG Group vereinbart Vertriebs- und Integrationspartnerschaft mit AutoGuide Mobile Robots