Open-Source-GPU baut auf RISC-V auf

Eine Gruppe von Enthusiasten schlägt einen neuen Satz von Grafikanweisungen vor, die für die 3D-Grafik und die Medienverarbeitung entwickelt wurden. Diese neuen Befehle bauen auf dem RISC-V-Basisvektorbefehlssatz auf. Sie werden Unterstützung für neue grafikspezifische Datentypen als geschichtete Erweiterungen im Geiste der RISC-V-Kernbefehlssatzarchitektur (ISA) hinzufügen. Vektoren, transzendentale Mathematik, Pixel und Texturen sowie Z/Frame-Pufferoperationen werden unterstützt. Es kann eine fusionierte CPU-GPU-ISA sein. Die Gruppe nennt es RV64X, da die Anweisungen 64 Bit lang sein werden (32 Bit werden nicht ausreichen, um eine robuste ISA zu unterstützen).

Warum jetzt?

Die Welt hat viele GPUs zur Auswahl, warum das? Denn, so die Gruppe, kommerzielle GPUs seien weniger effektiv bei der Erfüllung ungewöhnlicher Anforderungen wie z. Sie glauben, dass Zusammenarbeit flexible Standards bietet, den sonst erforderlichen Aufwand von 10 bis 20 Mannjahren reduziert und bei der Gegenverifizierung hilft, Fehler zu vermeiden.

Das Team sagt, dass seine Motivation und Ziele von dem Wunsch getrieben werden, ein kleines, flächeneffizientes Design mit benutzerdefinierter Programmierbarkeit und Erweiterbarkeit zu erstellen. Es sollte kostengünstigen Besitz und Entwicklung von geistigem Eigentum bieten und nicht mit kommerziellen Angeboten konkurrieren. Es kann in FPGA- und ASIC-Zielen implementiert werden und ist kostenlos und Open Source. Das anfängliche Design wird auf Mikrocontroller mit geringem Stromverbrauch ausgerichtet sein. Es wird Khronos Vulkan-kompatibel sein und im Laufe der Zeit andere APIs (OpenGL, DirectX und andere) unterstützen.

Die endgültige Hardware wird ein RISC-V-Kern mit einer GPU-Funktionseinheit sein. Für den Programmierer sieht es aus wie ein einzelnes Stück Hardware mit 64-Bit langen Befehlen, die als Skalarbefehle codiert sind. Das Programmiermodell ist eine scheinbare SIMD, d. h. der Compiler generiert SIMD aus vorangestellten skalaren Opcodes. Es wird variable Probleme, prädiziertes SIMD-Backend, Vektor-Frontend, präzise Ausnahmen, Branch Shadowing und viel . enthalten mehr. Es wird kein RPC/IPC-Aufrufmechanismus benötigt, um 3D-API-Aufrufe an/von ungenutztem CPU-Speicherplatz an GPU-Speicherplatz und umgekehrt zu senden, sagt das Team. Und es wird als 16-Bit-Festkomma (ideal für FPGAs) sowie als 32-Bit-Gleitkomma (ASICs oder FPGAs) verfügbar sein.

Das Design verwendet das Vblock-Format (von der Libre-GPU):

- Es ist ein bisschen wie VLIW (nur nicht wirklich)

- Ein Block von Anweisungen wird mit Register-Tags vorangestellt, die skalaren Anweisungen innerhalb des Blocks zusätzlichen Kontext verleihen

- Unterblöcke umfassen:Vektorlänge, Swizzle, Vektor-/Breitenüberschreibungen und Prädikation.

- All dies wird zu skalaren Opcodes hinzugefügt

- Es gibt keine Vektor-Opcodes (und es sind auch keine erforderlich)

- Im Vektorkontext sieht das so aus:Wenn ein Register von einem skalaren Opcode verwendet wird und das Register im Vektorkontext aufgeführt ist, wird der Vektormodus aktiviert

- Die Aktivierung führt dazu, dass eine for-Schleife auf Hardwareebene mehrere zusammenhängende skalare Operationen ausgibt (statt nur einer).

- Implementierer können die Schleife beliebig implementieren:SIMD, Multi-Isse, Single-Execution.

Das Design verwendet Skalare (8-, 16-, 24- und 32-Bit Fixed und Floats) sowie Transzendentalen (sincos, atan, pow, exp, log, rcp, rsq, sqrt usw.). Die Vektoren (RV32-V) unterstützen Vektoroperationen mit 2-4 Elementen (8-, 16- oder 32-Bit/Element) zusammen mit speziellen Anweisungen für eine allgemeine 3D-Grafik-Rendering-Pipeline für Punkte, Pixel, Texel (im Wesentlichen spezielle Vektoren) )

- XYZW-Punkte (64- und 128-Bit fest und Floats)

- RGBA-Pixel (8-, 16-, 24- und 32-Bit-Pixel)

- UVW-Texel (8-, 16-Bit pro Komponente)

- Lichter und Materialien (Ia, ka, Id, kd, Is, ks…)

Matrizen sind 2 × 2, 3 × 3 und 4 × 4 Matrizen werden als nativer Datentyp zusammen mit Speicherstrukturen unterstützt, um sie für Attributvektoren zu unterstützen, und werden im Wesentlichen in einer 4 × 4-Matrix dargestellt.

Zu den Vorteilen von Fused CPU-GPU ISA gehört die Möglichkeit, eine Standardgrafikpipeline in Mikrocode zu implementieren, Unterstützung für benutzerdefinierte Shader bereitzustellen und Raytracing-Erweiterungen zu implementieren. Es unterstützt auch Vektoren für numerische Simulationen mit 8-Bit-Integer-Datentypen für KI und maschinelles Lernen.

Benutzerdefinierte Rasterizer wie Splines, SubDiv-Oberflächen und Patches können implementiert werden.

Das Design wird flexibel genug sein, um benutzerdefinierte Pipeline-Stufen, benutzerdefinierte Geometrie-/Pixel-/Frame-Puffer-Stufen, benutzerdefinierte Tessellatoren und benutzerdefinierte Instanzierungsvorgänge zu implementieren.

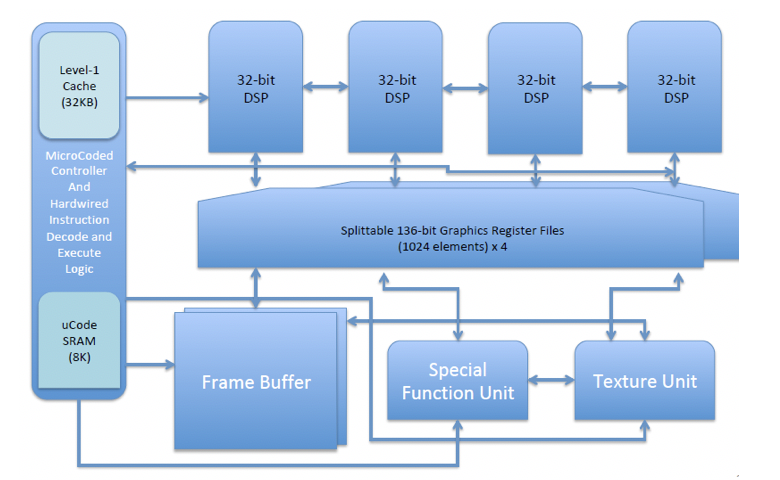

RV64X-Blockdiagramm

Die RV64X-Referenzimplementierung umfasst:

- Anweisungs-/Daten-SRAM-Cache (32 KB)

- Mikrocode-SRAM(8KB)

- Dual Function Instruction Decoder

- Festverdrahtete Implementierung von RV32V und X

- Mikrocodierter Befehlsdecoder für benutzerdefinierte ISA

- Quad Vector ALU (32 Bit/ALU – fest/float)

- 136-Bit-Registerdateien (1K Elemente)

- Sonderfunktionseinheit

- Textureinheit

- Konfigurierbarer lokaler Frame-Puffer

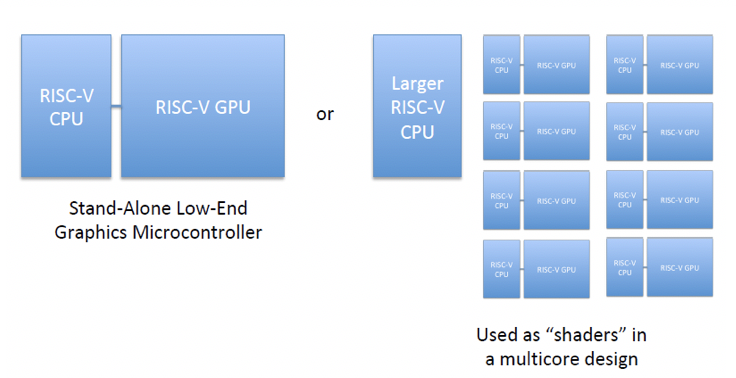

Das Design soll wie unten angegeben skalierbar sein.

Das skalierbare Design von RV64X

Das RV64X-Design verfügt über mehrere neuartige Ideen, darunter fusionierte Unified CPU-GPU ISA, konfigurierbare Register für benutzerdefinierte Datentypen und benutzerdefinierten SRAM-basierten Mikrocode für anwendungsdefinierte benutzerdefinierte Hardware-Erweiterungen für:

- Benutzerdefinierte Rasterisierungsstufen

- Raytracing

- Maschinelles Lernen

- Computer Vision

Das gleiche Design dient sowohl als eigenständiger Grafik-Mikrocontroller als auch als skalierbare Shader-Einheit, und Datenformate unterstützen FPGA-native oder ASIC-Implementierungen.

Warum werden offene Grafiken benötigt?

Die Entwickler glauben, dass die meisten Grafikprozessoren das High-End wie Gaming, Hochfrequenzhandel, Computer Vision und maschinelles Lernen abdecken. Sie glauben, dass dem Ökosystem ein skalierbarer Grafikkern für Mainstream-Anwendungen für Dinge wie Kioske, Billboards, Casinospiele, Spielzeug, Robotik, Haushaltsgeräte, Wearables, industrielle Mensch-Maschine-Schnittstellen, Infotainment und Automobil-Messgeräte fehlt. In der Zwischenzeit müssen spezielle Programmiersprachen verwendet werden, um GPU-Kerne für OpenGL, OpenCL, CUDA, DirectCompute und DirectX zu programmieren.

Eine Grafikerweiterung für RISC-V würde die Skalierbarkeit und Mehrsprachenlast beseitigen und ein höheres Maß an Anwendungsfallinnovation ermöglichen.

Nächste Schritte

Dies ist eine sehr frühe Spezifikation, die sich noch in der Entwicklung befindet und je nach Stakeholder- und Brancheneingaben geändert werden kann. Das Team wird ein Diskussionsforum einrichten. Ein unmittelbares Ziel ist der Aufbau einer Beispielimplementierung mit Befehlssatzsimulator, einer FPGA-Implementierung mit Open-Source-IP und benutzerdefinierter IP als Open-Source-Projekt. Demos und Benchmarks sind in Vorbereitung. Entwickler, die an einer Teilnahme interessiert sind, sollten Atif Zafar unter Vertrag nehmen.

Was die Libre-RISC 3D-GPU betrifft, so besteht das Ziel des Unternehmens darin, eine hybride CPU, VPU und GPU zu entwickeln. Es handelt sich nicht, wie weithin berichtet, um eine „dedizierte exklusive GPU“. Es besteht die Möglichkeit, ein eigenständiges GPU-Produkt zu erstellen. Ihr Hauptziel ist es, einen kompletten All-in-One-Prozessor-SoC zu entwickeln, der zufällig eine von Libre lizenzierte VPU und GPU enthält.

Was denken wir?

Die Zahl der GPU-Lieferanten nimmt zu. Wir haben jetzt über ein Dutzend.

AppleLibre-RISC-V 3D GPUQualcommAMDNvidiaRISC-V GraphicsArmIntelThink-SiliconDMPJingjia MicroVeriSilcionImagination TechnologiesEine Anwendung, die nicht als potenzieller Benutzer einer kostenlosen, flexiblen, kleinen GPU aufgeführt ist, umfasst Kryptowährung und Mining.

Wenn es das Ziel der RISC-V-Community ist, IP-Anbieter wie Arm und Imagination zu emulieren, können wir DSP-, ISP- und DP-Designs erwarten. Es gibt mindestens einen Open DSP-Vorschlag; vielleicht kann es in die RISC-V-Community eingebracht werden.

Es wird mindestens zwei Jahre dauern, bis Hardware-Implementierungen auf den Markt kommen. Einer der logischsten Kandidaten für die Übernahme dieses Designs ist Xilinx, das jetzt Arms Mali in seinem Zynq-Design verwendet. Wir würden auch erwarten, dass mehrere Implementierungen aus China kommen.

>> Dieser Artikel wurde ursprünglich veröffentlicht am unsere Schwesterseite EE Times.

Jon Peddie , ein Pionier in der grafischen Industrie, ist Präsident von Jon Peddie Research.

Jon Peddie , ein Pionier in der grafischen Industrie, ist Präsident von Jon Peddie Research. Für mehr Embedded, abonnieren Sie den wöchentlichen E-Mail-Newsletter von Embedded.

Eingebettet

- Einführung in die Open-Source-Terminologie

- Open Source und das IoT:Innovation durch Zusammenarbeit

- RISC-V-Gipfel:Highlights der Tagesordnung

- Sicherheit im industriellen IoT baut auf Hardware auf

- Ein Projektprotokoll für FirePick Delta, die Open Source MicroFactory

- AT&T, Tech Mahindra arbeiten an einer neuen Open-Source-KI-Plattform zusammen

- Softwarerisiken:Sicherung von Open Source im IoT

- Open-Source-IoT-Entwicklungstools im Vergleich zu anbieterunterstützten Tools

- MassRobotics veröffentlicht „weltweit erste“ Open-Source-Interoperabilitätsstandards für autonome mobile Roboter

- Die Notwendigkeit von Open Source am Edge (eBook)