Neuromorphe KI-Chips für die Bestückung neuronaler Netze debütieren

Innatera, das niederländische Startup, das neuromorphe KI-Beschleuniger für das Beschleunigen neuronaler Netze herstellt , hat seine ersten Chips produziert, ihre Leistung gemessen und Details ihrer Architektur enthüllt.

Innatera, das niederländische Startup, das neuromorphe KI-Beschleuniger für das Spiking neuronaler Netze herstellt, hat seine ersten Chips produziert, ihre Leistung gemessen und Details ihrer Architektur enthüllt.

Das Unternehmen hat außerdem bekannt gegeben, dass Alberto Sangiovanni-Vincentelli, Mitbegründer von Cadence und Synopsys, als Vorstandsvorsitzender in das Unternehmen eingetreten ist. Der Branchenveteran ist derzeit Professor an der University of California in Berkeley.

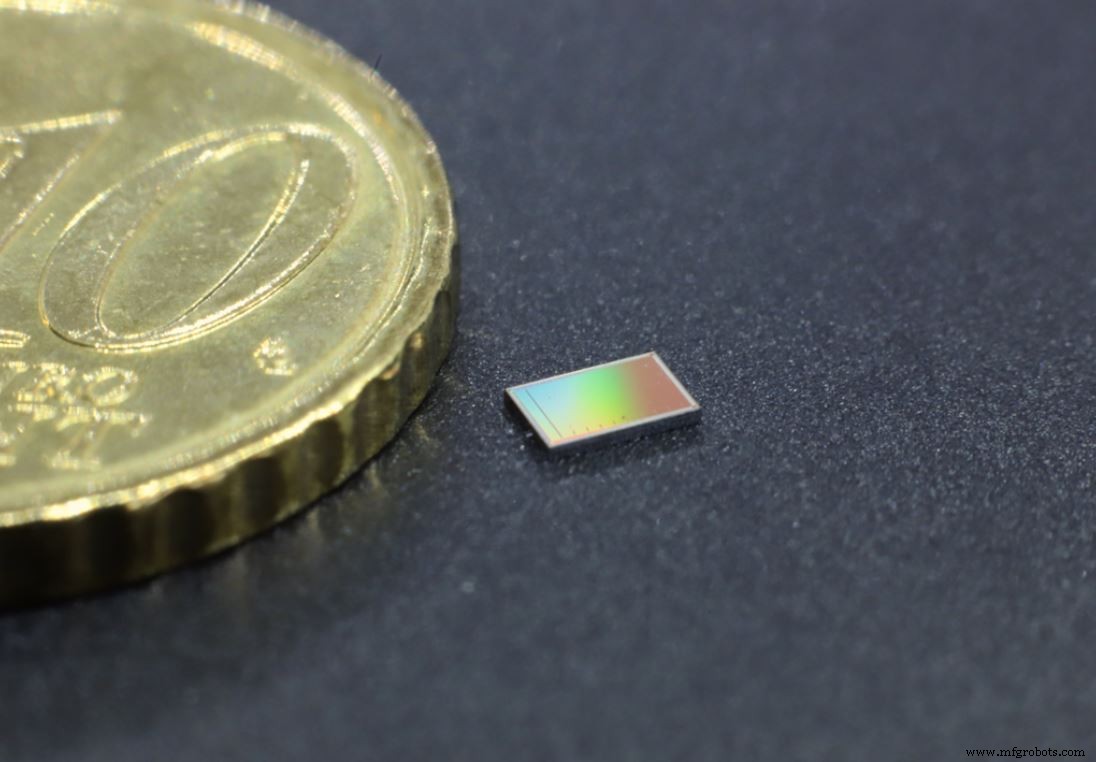

Der Chip von Innatera wurde entwickelt, um verschiedene SNNs für Audio-, Gesundheits- und Radaranwendungen zu beschleunigen (Bild:Innatera)

Der Innatera-Chip wurde entwickelt, um Spiking Neural Networks (SNNs) zu beschleunigen, eine Art neuromorpher KI-Algorithmus, der auf der Gehirnbiologie basiert und das Timing von Spitzen in einem elektrischen Signal verwendet, um Mustererkennungsaufgaben auszuführen. SNNs unterscheiden sich in ihrer Struktur vollständig von Mainstream-KI-Algorithmen und erfordern daher dedizierte Hardware zur Beschleunigung, bieten jedoch in der Regel erhebliche Vorteile bei Stromverbrauch und Latenz für Sensor-Edge-Anwendungen.

Die meisten anderen Unternehmen, die daran arbeiten, neuronale Netzwerkalgorithmen und -hardware zu verbessern (z. B. Prophesee), zielen auf Bilder und Videostreams ab. Innatera hat beschlossen, sich auf Audio (Ton- und Spracherkennung), Gesundheit (Überwachung von Vitalzeichen) und Radar (für Verbraucher-/IoT-Anwendungsfälle wie Sturzsensoren für ältere Menschen, die die Privatsphäre schützen) zu konzentrieren.

Marco Jacobs (Bild:Innatera)

„Diese Sensoren haben Zeitreihendaten anstelle von Bildern, die sehr parallel sind“, sagte Marco Jacobs, Innatera VP Marketing and Business Development, in einem Interview mit EE Times . „Unser Array ist besonders gut bei der Verarbeitung von Zeitreihendaten … es passt gut zur Technologie. Auch aus Marktsicht sehen wir in diesem Bereich viele interessante Anwendungen und nicht so viele Lösungen, die sich damit befassen.“

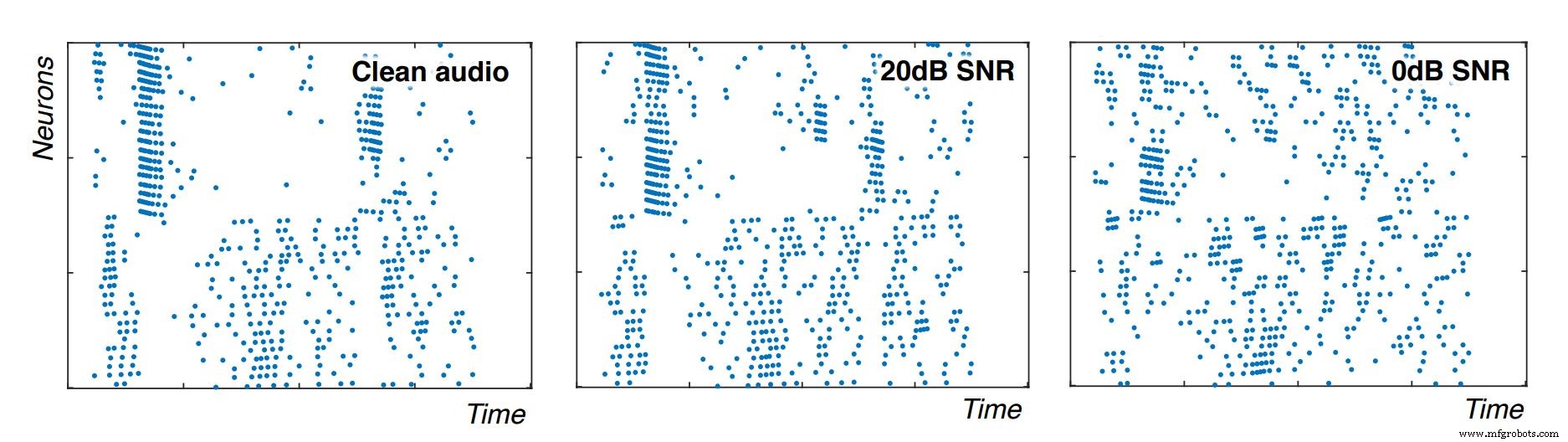

Eine weitere Gemeinsamkeit dieser drei Anwendungen besteht darin, dass der Leistungsbereich sehr eng ist, da eine Verarbeitung im Sensorknoten erforderlich ist. In den Tests von Innatera benötigte jedes Spike-Ereignis (jedes Neuron feuert als Reaktion auf Eingabedaten) weniger als ein PicoJoule Energie – tatsächlich weniger als 200 FemtoJoule in TSMC 28 nm, bestätigte Innatera. Dies nähert sich der Energiemenge, die von biologischen Neuronen und Synapsen verbraucht wird. Eine typische Audio-Keyword-Spotting-Anwendung erforderte weniger als 500 Spitzenereignisse pro Inferenz, was laut Sumeet Kumar, CEO von Innatera, zu einer „tiefen Verlustleistung im Sub-Milliwatt-Bereich“ führte. In diesem Fall repräsentieren Cluster von Neuronen, die zusammen feuern, verschiedene Phoneme in der Sprache.

Cluster feuernder Neuronen (hier Punktgruppen) repräsentieren die Erkennung von Phonemen in der Sprache. Da die Eingabedaten mehr Rauschen enthalten, sind meistens dieselben Cluster vorhanden, obwohl sie schwerer zu erkennen sind (Bild:Innatera)

Verarbeitungsarchitektur

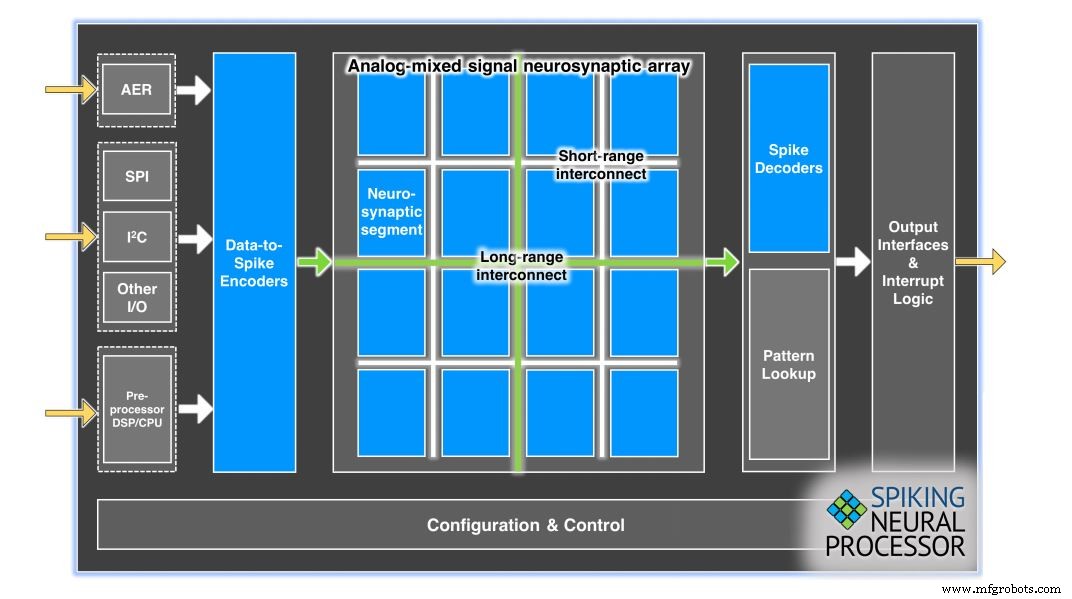

Der Spiking-Neuralprozessor von Innatera verwendet eine parallele Anordnung von Spiking-Neuronen und Synapsen, um zeitkontinuierliche SNNs mit feinkörniger zeitlicher Dynamik zu beschleunigen. Das Gerät ist ein Analog-/Mixed-Signal-Beschleuniger, der entwickelt wurde, um die Fähigkeit von SNN zu nutzen, den Zeitbegriff in die Verarbeitung der Daten einzubeziehen.

Der neuronale Spiking-Prozessor von Innatera umfasst ein massiv paralleles neurosynaptisches Array sowie Spike-Encoder und -Decoder (Bild:Innatera)

Einer der Schlüsselaspekte der Compute Fabrics von Innatera ist ihre Programmierbarkeit, die aus zwei Gründen wichtig ist.

Zuerst das Programmieren verschiedener SNNs auf dem Chip. Neuronen müssen flexibel verbunden werden – das Gehirn verwendet sehr komplexe neuronale Netztopologien, um Dinge effizient zu erledigen, was komplexe Verbindungen zwischen Neuronen erfordert, die in Silizium neu erstellt werden müssen.

Sumeet Kumar (Bild:Innatera)

Zweitens, um die Leistung zu optimieren. Anstatt Informationen als Bits in Worten darzustellen, werden Informationen in einem SNN als präzise zeitlich festgelegte Spitzen dargestellt. Das Timing der Spitzen muss auf sehr feinkörniger Ebene manipuliert werden, um Erkenntnisse über die Daten zu gewinnen. Die Neuronen und die Verbindungen zwischen ihnen (die Synapsen) müssen daher ein komplexes Timing-Verhalten aufweisen. Diese Verhaltensweisen können über das SDK von Innatera angepasst werden, um die Leistung zu optimieren.

Innatera beschreibt seinen Chip als Analog-Mixed-Signal oder „Digitally Assisted Analog“. Neuronen und Synapsen sind in analogem Silizium implementiert, um einen extrem niedrigen Stromverbrauch aufrechtzuerhalten. Analoge Elektronik ermöglicht auch zeitkontinuierliche Netzwerke (digitale Elektronik würde eine Diskretisierung erfordern). Dies ist für SNNs wichtig, da sie aufgrund ihrer Natur von Natur aus eine Vorstellung von Zeit haben und in der Lage sein müssen, bestimmte Zustände über einen bestimmten Zeitraum zu halten.

„Dies ist im analogen Bereich viel einfacher – Sie müssen die Komplexität der Zustandsbeibehaltung nicht auf die Netzwerktopologie verlagern“, sagte Kumar. „Unsere Rechenelemente behalten diese Zustandsinformationen natürlich bei. Aus diesem Grund machen wir Dinge im analogen Bereich.“

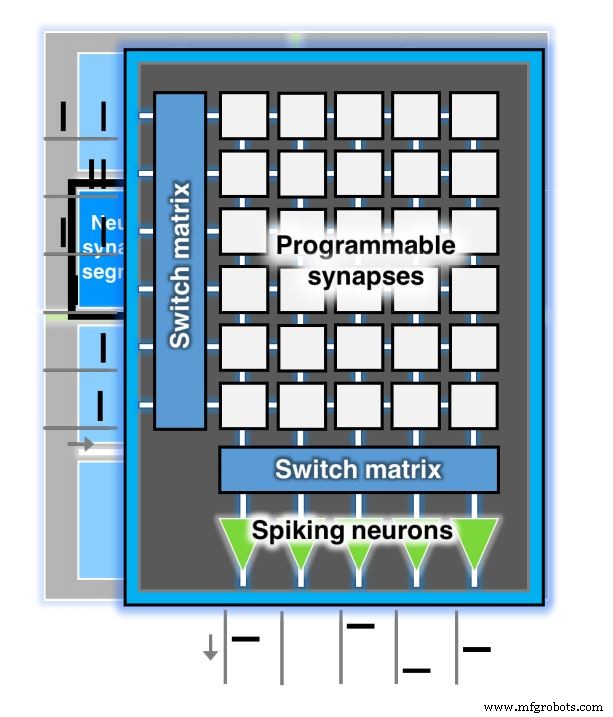

Ein Rechensegment im Array von Innatera, in dem die Neuronen sorgfältig aufeinander abgestimmt sind. Programmierbare Synapsen sind in einer mehrstufigen Crossbar-Struktur angeordnet. (Schwarze Linien/Strichstriche stellen hier Input- und Output-Spitzen dar) (Bild:Innatera)

Geringfügige Inkonsistenzen bei der Herstellung zwischen Rechenelementen auf dem Chip und zwischen verschiedenen Chips können ein Problem für die genaue Implementierung neuronaler Netze im analogen Bereich sein. Die Lösung von Innatera besteht darin, Neuronen in sogenannte Segmente zu gruppieren, die sorgfältig so gestaltet sind, dass sie den Pfadlängen und der Anzahl der Neuronen entsprechen.

Das Segmentdesign „ermöglicht uns im Wesentlichen, die besten analogen Schaltungen zu verwenden und gleichzeitig diese Nicht-Idealitäten zu minimieren, die Sie normalerweise in einer analogen Schaltung haben würden“, sagte Kumar. „All dies wurde im Wesentlichen getan, um sicherzustellen, dass Neuronen innerhalb eines Segments ein deterministisches Verhalten zeigen und ähnlich wie ihre unmittelbaren Nachbarn funktionieren.“

Inkonsistenzen zwischen verschiedenen Chips können zu Problemen führen, wenn das gleiche trainierte Netzwerk auf Geräte im Feld ausgerollt wird. Innatera umgeht dies mit Software.

„Mismatch und Variabilität werden tief im SDK behandelt“, sagte Kumar. „Wenn Sie ein Power-User sind, können wir Ihnen einiges davon zeigen, aber ein typischer Programmierer muss sich nicht darum kümmern.“

Anwendungsspezifisch

Innatera, ein Spin-out der Technischen Universität Delft, arbeitete bereits mit Umsatzkunden an seinen SNN-Algorithmen, bevor sie in die Hardware einstieg und gegen Ende 2020 eine Seed-Runde von 5 Millionen Euro (rund 6 Millionen US-Dollar) aufnahm.

„Wir haben mit einer Reihe von Kunden zusammengearbeitet, seit wir das Unternehmen tatsächlich gegründet haben, und diese Engagements dauern noch an – sie sind sehr gereift“, sagte Kumar. „Wir hoffen, im Laufe dieses Jahres weitere Vorführungen zusammen mit einigen dieser Kunden zeigen zu können.“

Kumar sagte, dass das Unternehmen seinen Fokus als Computing-Lösungsunternehmen beibehält, das heißt, es wird schlüsselfertige Lösungen liefern, die sowohl hardware- als auch anwendungsspezifische SNN-Algorithmen umfassen.

Der erste Chip von Innatera eignet sich für Audio-, Gesundheits- und Radaranwendungen. Die Roadmap des Unternehmens könnte weitere optimierte Chips für jede der Anwendungen beinhalten.

„Wir haben das Gerät so konzipiert, dass wir eine Vielzahl von Spiking-Neuralnetzwerken beschleunigen können“, sagte Kumar. „[Unser Chip] kann diese Netzwerke über Anwendungsdomänen hinweg implementieren. Wenn wir jedoch tiefer in die Domänen vordringen, kann es erforderlich sein, das Hardwaredesign zu optimieren, und dies werden wir uns in Zukunft ansehen. Im Moment ist die Hardware nicht übermäßig auf eine bestimmte Klasse von Anwendungen oder irgendeine Art von Spiking-Neuralnetzwerken spezialisiert, das Ziel besteht darin, eine Vielzahl von ihnen im Allgemeinen innerhalb der Architektur zu unterstützen.“

Muster des ersten Chips werden voraussichtlich vor Ende 2021 verfügbar sein.

>> Dieser Artikel wurde ursprünglich auf unserer Schwesterseite EE . veröffentlicht Zeiten.

Verwandte Inhalte:

- KI-Chip zielt auf Edge-Geräte mit geringem Stromverbrauch ab

- Toolkette und Sensorplatine verbessern das KI-Chip-Ökosystem

- Neue KI-Beschleunigungsmodule verbessern die Edge-Leistung

- KI am Rande:Worauf Sie 2021 achten sollten

- So implementieren Sie AI of Things (AIoT) auf MCUs

Für mehr Embedded, abonnieren Sie den wöchentlichen E-Mail-Newsletter von Embedded.

Eingebettet

- Co-Simulation für Zynq-basierte Designs

- Renesas:Automobilchips von Nissan für seinen neuen Skyline ProPILOT 2.0

- CEVA:KI-Prozessor der zweiten Generation für tiefe neuronale Netzwerk-Workloads

- Plädoyer für neuromorphe Chips für KI-Computing

- Low-Power-Radarchip verwendet neuronale Spiking-Netzwerke

- Lanner:LTE-fähiges Edge-Gateway zertifiziert für IoT und SD-WAN in Mobilfunknetzen

- IBM bei SPIE:Sieben Fortschritte für mehr als 7-nm-Chips

- NPE ist US-Debüt für das Campetella Robotic Center

- 3G ist tot:Wie geht es weiter für Produktdesigner?

- LoRaWAN ersetzt vorübergehend 5G-Netze für IoT