Delta-Sigma-ADC

Eine der fortgeschritteneren ADC-Technologien ist das sogenannte Delta-Sigma oder ΔΣ (mit der richtigen griechischen Buchstabenschreibweise). In Mathematik und Physik steht der griechische Großbuchstabe Delta (Δ) für Unterschied oder ändern , während der Großbuchstabe Sigma (Σ) eine Summation . darstellt :das Zusammenfügen mehrerer Begriffe. Manchmal wird dieser Konverter mit denselben griechischen Buchstaben in umgekehrter Reihenfolge bezeichnet:Sigma-Delta oder ΣΔ.

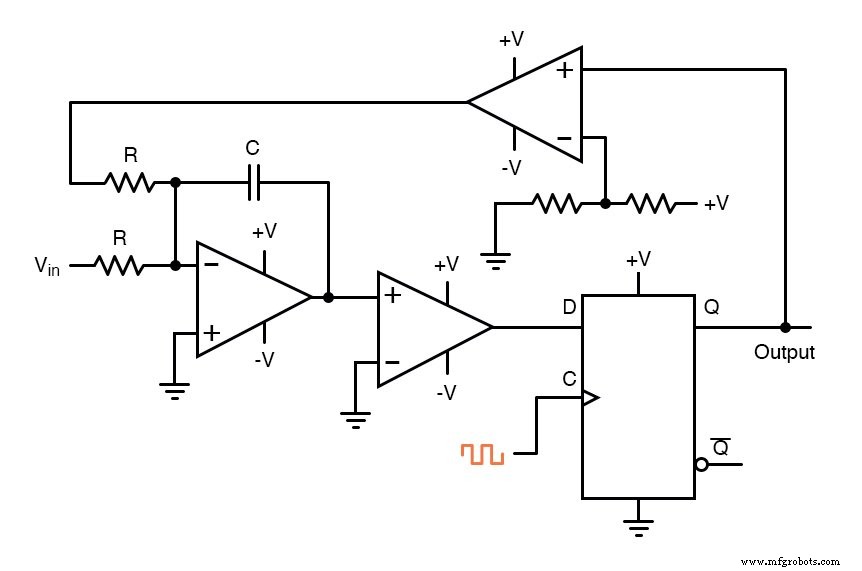

In einem -Wandler wird das analoge Eingangsspannungssignal mit dem Eingang eines Integrators verbunden, wodurch eine Spannungsänderungsrate oder Steilheit am Ausgang entsprechend der Eingangsgröße erzeugt wird. Diese Rampenspannung wird dann von einem Komparator mit dem Massepotential (0 Volt) verglichen.

Der Komparator fungiert als eine Art 1-Bit-ADC, der 1 Bit Ausgabe ("high" oder "low") erzeugt, je nachdem, ob der Integratorausgang positiv oder negativ ist. Der Ausgang des Komparators wird dann durch ein hochfrequent getaktetes D-Flip-Flop zwischengespeichert und rückgekoppelt an einen anderen Eingangskanal des Integrators, um den Integrator in Richtung eines 0-Volt-Ausgangs zu treiben. Die Grundschaltung sieht so aus:

Schematische Darstellung

Der Operationsverstärker ganz links ist der (Summierungs-)Integrator. Der nächste Operationsverstärker, in den der Integrator einspeist, ist der Komparator oder 1-Bit-ADC. Als nächstes kommt das D-Flip-Flop, das den Ausgang des Komparators bei jedem Taktimpuls zwischenspeichert und entweder ein "High"- oder "Low"-Signal an den nächsten Komparator an der Spitze der Schaltung sendet.

Dieser letzte Komparator ist erforderlich, um die 0V/5V-Ausgangsspannung des Flip-Flops mit einfacher Polarität mit Logikpegel in ein +V/–V-Spannungssignal umzuwandeln, das an den Integrator zurückgeführt wird. Wenn der Integratorausgang positiv ist, gibt der erste Komparator ein „High“-Signal an den D-Eingang des Flip-Flops aus.

Beim nächsten Taktimpuls wird dieses „high“-Signal von der Q-Leitung in den nichtinvertierenden Eingang des letzten Komparators ausgegeben. Dieser letzte Komparator, der eine Eingangsspannung sieht, die größer als die Schwellenspannung von 1/2 +V ist, sättigt sich in positiver Richtung und sendet ein volles +V-Signal an den anderen Eingang des Integrators.

Dieses +V-Rückkopplungssignal neigt dazu, den Integratorausgang in eine negative Richtung zu treiben. Wenn diese Ausgangsspannung jemals negativ wird, sendet die Rückkopplungsschleife ein Korrektursignal (-V) zurück an den oberen Eingang des Integrators, um ihn in eine positive Richtung zu treiben.

Dies ist das Delta-Sigma-Konzept in Aktion:Der erste Komparator erkennt einen Unterschied (Δ) zwischen dem Integratorausgang und null Volt. Der Integrator summiert (Σ) der Ausgang des Komparators mit dem analogen Eingangssignal.

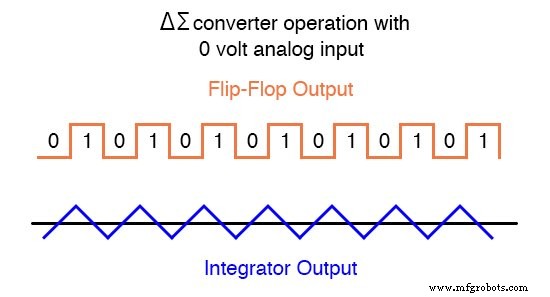

Funktionell führt dies zu einem seriellen Bitstrom, der vom Flip-Flop ausgegeben wird. Wenn der analoge Eingang null Volt beträgt, neigt der Integrator nicht dazu, positiv oder negativ zu steigen, außer als Reaktion auf die Rückkopplungsspannung.

In diesem Szenario oszilliert der Flip-Flop-Ausgang ständig zwischen „high“ und „low“, während das Rückkopplungssystem hin und her „jagt“ und versucht, den Integratorausgang auf null Volt zu halten:

Ausgangswellenformen

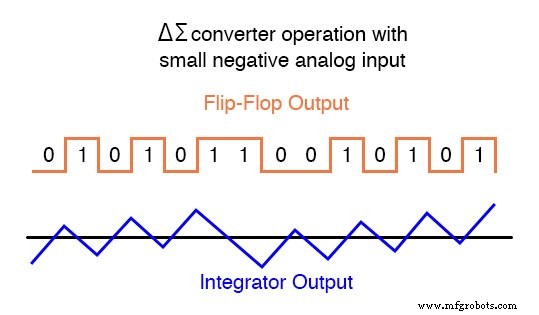

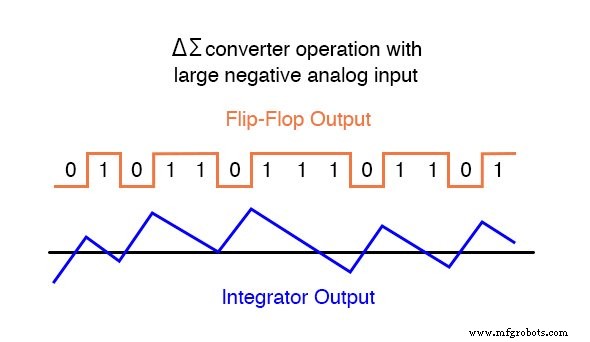

Wenn wir jedoch eine negative analoge Eingangsspannung anlegen, neigt der Integrator dazu, seinen Ausgang in eine positive Richtung zu erhöhen. Die Rückkopplung kann nur um eine feste Spannung über eine feste Zeit zum Anstieg des Integrators beitragen, und daher wird der Bitstrom, der vom Flip-Flop ausgegeben wird, nicht ganz gleich sein:

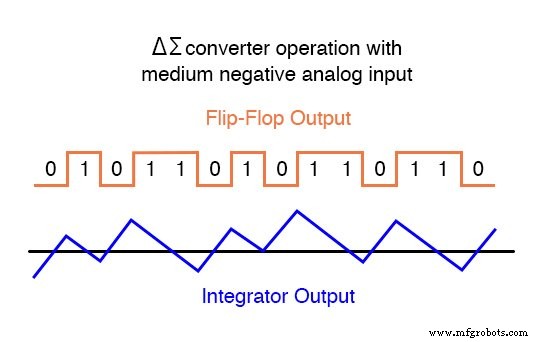

Durch Anlegen eines größeren (negativen) analogen Eingangssignals an den Integrator erzwingen wir, dass sein Ausgang steiler in positiver Richtung ansteigt. Daher muss das Rückkopplungssystem mehr Einsen als zuvor ausgeben, um den Integratorausgang wieder auf null Volt zu bringen:

Mit zunehmender Größe des analogen Eingangssignals steigt auch das Auftreten von Einsen im digitalen Ausgang des Flip-Flops:

Eine parallele Binärzahlausgabe wird von dieser Schaltung erhalten, indem der serielle Bitstrom zusammen gemittelt wird. Zum Beispiel könnte eine Zählerschaltung so ausgelegt sein, dass sie die Gesamtzahl der Einsen-Ausgaben des Flip-Flops in einer gegebenen Anzahl von Taktimpulsen sammelt. Dieser Zählerstand würde dann die analoge Eingangsspannung anzeigen.

Es gibt Variationen zu diesem Thema, die mehrere Integratorstufen und/oder Komparatorschaltungen verwenden, die mehr als 1 Bit ausgeben, aber ein allen ΔΣ-Wandlern gemeinsames Konzept ist das der Überabtastung . Überabtastung liegt vor, wenn mehrere Abtastwerte eines analogen Signals von einem ADC (in diesem Fall ein 1-Bit-ADC) genommen werden und diese digitalisierten Abtastwerte gemittelt werden.

Das Endergebnis ist eine effektive Erhöhung der Anzahl der aus dem Signal aufgelösten Bits. Mit anderen Worten, ein 1-Bit-ADC mit Oversampling kann die gleiche Aufgabe erfüllen wie ein 8-Bit-ADC mit einmaliger Abtastung, wenn auch mit einer langsameren Rate.

VERWANDTES ARBEITSBLATT:

- Arbeitsblatt zur Analog-zu-Digital-Konvertierung

Industrietechnik