PCB-Layout-Einfluss der EMV-Leistung elektronischer Produkte

Masse in PCB

• Einfluss von Common-Code-Interferenzen auf das PCB-Innensignal

Die inneren gedruckten Leitungen der Leiterplatte (PCB) weisen parasitäre Parameter relativ zur Bezugsmasseplatine auf, und wenn Funktionssignale innerhalb der Leiterplatte übertragen werden, ist derselbe Äquipotentialknoten im selben Netzwerk in der Schaltung nicht mehr äquipotential. Der Strom i innerhalb der Leiterplatte beginnt am Quellenende, führt eine Reihe von Trägern zurück zur Signalquelle und bildet ein Signal. Darüber hinaus tendiert i dazu, mit niedriger Impedanz entlang des Pfades zu fließen, so dass i normalerweise mit der Stabilität der Impedanz unveränderlich bleibt.

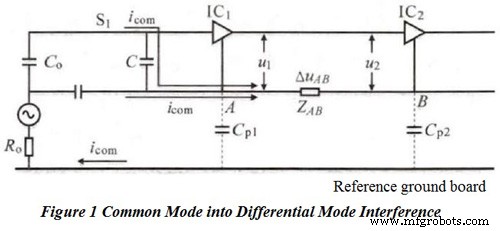

Abbildung 1 zeigt den Prozess, wenn Gleichtaktstörungen in Gegentaktstörungen innerhalb der Leiterplatte umgewandelt werden. id bezieht sich auf den Gegentaktstrom innerhalb des PCB-Flusses während icom bezieht sich auf den Gleichtaktstrom, der entweder außerhalb der Leiterplatte beginnt und durch die Bezugserdungsplatine in die Leiterplatte fließt oder im Inneren der Leiterplatte beginnt und durch die Bezugserdungsplatine in die Innenseite der Leiterplatte zurückkehrt. Hochfrequenz-icom hat zwei Pfade:der erste führt von Punkt A nach Punkt B innerhalb der Leiterplatte, beginnend bei GND; die zweite ist von Punkt A nach Punkt B, ausgehend von Port S1 zur PCB-Innenseite durch Kapazität C. Erdungsimpedanz ZAB führt zur Erzeugung von ΔuAB , also wenn ein normales Signal an IC2 weitergegeben wird , findet eine Verformung statt, um ein Signal zu erzeugen, und eine Gleichtaktstörung wird in eine Gegentaktstörung umgewandelt, die einen Einfluss auf ein normales Signal basierend auf der Formel u2 erzeugt =u1 -ΔuAB .

Daher sobald icom durch E/A-Port oder Weltraumstrahlung in das Innere der Leiterplatte eindringt, kann die Differenzfilterkapazität auf den Signalleitungen der Leiterplatte nur die Störungsumgehung auf GND drücken. Voraussetzung für dieses Ergebnis ist, dass GND bei Signalrückfluss als niederohmig angesehen wird und Strom immer in Richtung niederohmiger fließt.

• Schlüssel der EMV-Designimplementierung:Erdungsimpedanz in PCB

Der Grund für die EMV-Erzeugung durch hochfrequente Signale liegt darin, dass der Signalbezugspegel GND seine Eigenschaft der Niederohmigkeit nicht einhält. Mit der Erhöhung der Impedanz ZGND des Referenzpegels sinkt auch die Qualität der Signalübertragung. Um das Problem der hochfrequenten Störungen zu lösen, werden im EMV-Design gängige Methoden wie Filter, Masse und Abschirmung eingesetzt, die eng mit "Masse" verbunden sind.

Der Filter kann als Kondensator gegen Masse betrachtet werden, mit zwei Strukturen, von denen eine den X-Kondensator mit der Signalbezugserde und die andere das Signal mit dem Metallgehäuse durch den Y-Kondensator oder eine andere Masseverbindung innerhalb der Leiterplatte verbinden soll. Die Abschirmung kann als Ergebnis der Ausdehnung der Leiterplattenmasse in den Weltraum angesehen werden. Der Zweck des Filters oder der Abschirmung besteht darin, hochfrequente Gleichtaktstörungen mit niedriger Impedanz durch den Bypass passieren zu lassen, um zu vermeiden, dass sie in das Normalbetriebssignal fließen. Ebenso funktionieren alle diese Methoden nur, wenn die Erdung eine niedrige Impedanz hat.

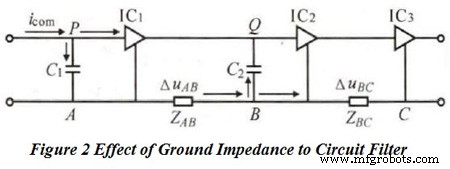

Abbildung 2 zeigt die Wirkung der Erdimpedanz auf den Schaltungsfilter. icom fließt gemäß der Sequenz von IC1 →IC2 →IC1 und wenn es zu Punkt P fließt, icom fließt in Zweigschaltungen von IC1 und C1 durch die es von Punkt A nach B fließt. Ist die Impedanz zwischen Punkt A und B, also ZAB , ist weit geringer als die Impedanz zwischen Punkt P und IC1 . In diesem Moment icom fließt von Punkt P nach A, IC1 Filter realisiert werden. Wenn icom zu Punkt B fließt, treten Abzweigungen auf, die B→C und B→Q sind. Wenn das PCB-Layout nicht gut kontrolliert wird, ist die Impedanz zwischen Punkt B und C, also ZBC , ZBC>>ZC2 +ZQ . ZQ bezieht sich auf die Impedanz zwischen Punkt Q und IC2 . icom fließt zurück zu IC2 Eingangsport durch C2 als Kapazität, die ursprünglich nur für IC2 verwendet wurde spielt eine Rolle bei der Signalinvasionsinterferenz.

Um Referenzpegel niederohmig herzustellen, wird dieser meist als Fläche ausgeführt. Im Allgemeinen können Leiter, deren Längen-Breiten-Verhältnis kleiner als 5 ist, in der Technik als niederohmig angesehen werden. Die Impedanz gedruckter Leitungen wird nicht durch ihren Längen- oder Dickengrad bestimmt. In den traditionellen PCB-Designprinzipien wird die Einzelpunkterdung analoger Schaltungen dringend empfohlen, so dass das PCB-Layoutprinzip der digitalen Schaltungsmehrpunkterdung und der gemischten Erdung digitaler Modulschaltungen für den Umgang mit EMV-Problemen nicht mehr praktikabel ist.

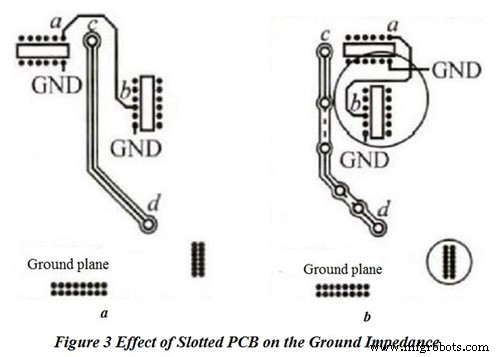

Da alle Rückflüsse aller Signale über eine integrierte Erdung mit niedriger Impedanz verfügen müssen, können 4-Layer- oder Multi-Layer-Platinen mit integrierter Massefläche die Anforderung erfüllen, kostengünstige Einzelplatinen jedoch nicht. Wenn aus Kostengründen eine zweilagige Platine verwendet werden muss, sollte eine relativ integrierte Masseebene für Signale innerhalb der Leiterplatte entworfen werden. In der praktischen Anwendung wird die Erdungsimpedanz der Leiterplatte sowohl durch ihre Form als auch durch Durchgangslöcher, Risse und Schlitze der Signalleitung beeinflusst. Die Abbildungen 3a und 3b zeigen jeweils ein schlechtes und ein ausgezeichnetes Design der Erdungsebene mit niedriger Impedanz.

In dieser Abbildung befinden sich alle Komponenten auf der Vorderseite der Leiterplatte, während sich die Masseebene auf der Rückseite befindet. Chips werden durch gedruckte Linien ab auf der Vorderseite und cd durch gedruckte Linien auf der Rückseite verbunden. Unter dem Druck hochfrequenter Gleichtaktstörungen von außen führt die durch cd gebildete Schlitzbildung zu einer Erhöhung von ZGND von gedruckten Linien Rückfluss. ZGND schwankt im Prozess der Signalübertragung, was zu einer geringen Signalqualität führt. Daher können Schichten von gedruckten Leitungen zwischen cd immer wieder durch Löcher im Prozess des PCB-Layout-Designs ausgetauscht werden, so dass ZGND wird verringert. Außerdem zwei ICS mit empfindlichen Signalen können so angeordnet werden, dass GND lokal zu einer relativ integrierten Masseebene wird, um sicherzustellen, dass das Signal nicht in den Prozess der Signalübertragung eingegriffen wird. Beachten Sie, dass Durchgangslöcher nicht mit viel Dichte angeordnet werden können, da sonst auch Risse auf der Masseebene verursacht werden, was zur Eskalation von ZGND führt .

Stapeldesign von Leiterplatten

Das EMV-Design eignet sich am besten für 4-lagige Leiterplatten. Aus Sicht der EMS ist entweder die Metallhülle oder die Metallhüllenabschirmung von lokal empfindlichen Schaltungen in der Lage, Interferenzprobleme zu lösen. Aus der Perspektive der EMI erfüllen 4-Lagen-Platinen manchmal nicht die Anforderung der Strahlungsemissionsbegrenzung und die Anzahl der Lagen sollte erhöht werden, da Multilayer-Platinen Signale mit hohem du erzeugen können /dt und di /dt Stellen Sie eine kleinere Signalschleifenfläche während des Übertragungsprozesses sicher und bieten Sie einen Rückfluss mit niedriger Impedanz für Hochgeschwindigkeitssignale.

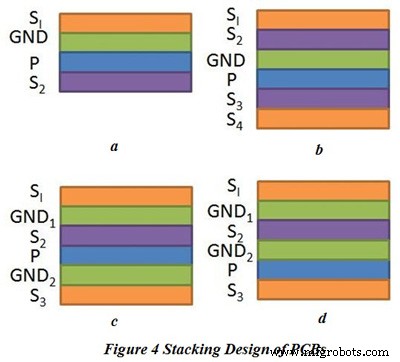

Das Grundprinzip des PCB-Stacking-Designs besteht darin, die Hochgeschwindigkeits-Signalschicht und die Leistungsebene neben der Masseebene anzuordnen. Abbildung 4 zeigt das Stapeldesign von 4-Lagen- und 6-Lagen-Platten. S1 in Abbildung 4a bezieht sich auf die Hochgeschwindigkeits-Signalschicht, während die Abbildungen 4b, 4c und 4d drei gewöhnliche 6-Schicht-PCB-Designs zeigen.

Unter den 3 6-Lagen-PCB-Designs ist Design b das schlechteste und S2 Schicht sollte Hochgeschwindigkeitssignalschicht sein. S2 Schicht in Design c und d ist eine Hochgeschwindigkeits-Signalschicht. Design c ist das beste, da jede Signalschicht eng an die Masseebene angrenzt, um den kürzesten Signalrückflusspfad und S2 sicherzustellen und P-Schichten sind durch GND1 abgeschirmt und GND2 . Verglichen mit Design c, S3 in Design d ist weit von der GND-Schicht entfernt und P kann nur den einseitigen Effekt anstelle des doppelseitigen Effekts erreichen, der durch Design c verursacht wird.

Äquivalente Antenne in Leiterplatten

Die grundlegende Funktion der Antenne besteht darin, drahtlose Funkwellen auszustrahlen und zu empfangen. Bei der Bestrahlung kann hochfrequenter Strom in elektromagnetische Wellen umgewandelt werden; Beim Empfang werden elektromagnetische Wellen in hochfrequenten Strom umgewandelt. Die Strahlung im EMV-Bereich bezieht sich hauptsächlich auf Fernfeldstrahlung. Die Bildung der Antenne hängt von zwei Grundbedingungen ab:der HF-Signalquelle und einer bestimmten Länge der mit der HF-Signalquelle verbundenen Leiter. Auf dem Gebiet der Technik wird angenommen, dass ein Antenneneffekt auftritt, wenn die Länge des Leiters der Formel entspricht, die l =λ/20 ist. Bei l=(λ/4)n ist der Antenneneffekt mit n als natürlicher Zahl am größten.

Wenn das Signal innerhalb der Leiterplatte übertragen wird, hat die innere Schleife den gleichen Effekt wie die Rahmenantenne. Je größer die Schleifenfläche ist, desto größer ist der Antenneneffekt. Eine strenge PCB-Schleifensteuerung kann Gegentaktstörungen effektiv stoppen, was in der Praxis machbar ist. Eine zunehmende Länge der gedruckten Leitungen führt jedoch zu einem offensichtlichen Stabantenneneffekt, daher sollte die Länge der Verbindungssignale im Prozess des PCB-Layouts so weit wie möglich gekürzt werden.

Bei relativ hohem ZGND findet auf dem Rückflusspfad von hohen du/dt-Signalen statt, die innerhalb der PCB, Gleichtakttreiberquelle ucom übertragen werden findet mit icom statt fließt an ZGND vorbei , zusammen mit angeschlossenen gedruckten Leitungen oder E/A-Stallen, die nach außen strahlen können.

Wenn Leiterplatten relativ klein sind, können die inneren gedruckten Leitungen aufgrund der Längenbeschränkung die Antennenstrahlungsanforderungen nicht erreichen. Unter dieser Bedingung kann das E/A-Kabel als Erweiterung gedruckter Leitungen angesehen werden, die Strahlungsanforderungen können erfüllt werden. Auch wenn keine direkte Verbindung zu stabilen I/Os besteht, sollte die Nebensprechkopplung zwischen I/O-Kabeln gestoppt werden.

Übersprechen in Leiterplatten und seine Abhilfemaßnahmen

• Kopplung zwischen gedruckten Leiterplattenleitungen und Bezugserde

Da es bei EMV hauptsächlich um hochfrequente Gleichtaktsignale geht, sind Verteilungsparameter weder innerhalb noch außerhalb der Leiterplatte zu vermeiden. Zwischen Leiterplatte und Bezugsmasse tritt eine kapazitive Kopplung auf, deren Flächenkapazität sich auf engstem Raum aus Plattenkapazität und Eigenkapazität zusammensetzt. Die Plattenkapazität ist direkt proportional zur Größe der Leiterplatte und indirekt proportional zum Abstand zwischen Leiterplatte und Masse. Die natürliche Kapazität auf kleinstem Raum ist direkt proportional zum äquivalenten Durchmesser der gedruckten Leitungen innerhalb der Leiterplatte. Daher besteht unabhängig davon, wo die Leiterplatte platziert ist, selbst weit entfernt von der Erde in der Unendlichkeit, immer eine verteilte Kapazität zwischen den innen gedruckten Leitungen und der Erde. In einer PCB beträgt die verteilte Kapazität einer relativ integrierten GND-Ebene zur Bezugsmasseplatine ungefähr 10 pF, und die verteilte Kapazität von innen gedruckten Leitungen zur Bezugsmasseplatine liegt ungefähr im Bereich von 0,001 pF bis 0,1 pF oder weniger. Die verteilte Kapazität von gedruckten Leitungen in der Mitte der Leiterplatte ist viel geringer als die von gedruckten Leitungen am Rand der Leiterplatte.

• Kupplung innerhalb der Leiterplatte

a. Theorie der Kopplung innerhalb der Leiterplatte und ihr Einfluss auf das Signal

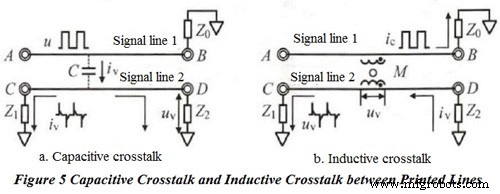

Die Kopplung innerhalb der Leiterplatte besteht aus kapazitiver Kopplung und induktiver Kopplung, deren Theorie in Abbildung 5 dargestellt ist.

In dieser Figur sind sowohl AB als auch CD parallel gedruckte Linien mit geringem Abstand zwischen zwei Linien. Z0 bezieht sich auf den Träger der Signalleitung 1, während Z1 und Z2 beziehen sich jeweils auf Träger der Signalleitung 2. In Fig. 5a ist, wenn die Signalspitzenspannung auf der gedruckten Leitung AB u ist, die Signalanstiegszeit Δt ist und die Kreisfrequenz ω ist, die Spannung von Z 2 wird uv sein =[Z1 Z2 /(Z1 +Z2 )]cΔu/Δt. Obwohl c einen sehr niedrigen Wert hat, kann der Wert von Δu/dt sehr hoch sein und ihr Produkt kann nicht vermieden werden. In Fig. 5b, wenn der Spitzenstrom des Signals auf AB gleich Ic ist , die Signalanstiegszeit ist Δt und die Winkelfrequenz ist ω, die gegenseitige Induktivität m zwischen 2 gedruckten Linien wird durch CD hindurchgehen, auf der die Induktionsspannung uv ist =mωic . Obwohl der Wert von m so klein ist, kann die Signalfrequenz erhöht werden. Daher kann ihr Produkt nicht vermieden werden.

Als Ergebnis hängen sowohl die kapazitive Kopplung als auch die induktive Kopplung mit den verteilten Parametern c oder m zweier gedruckter Linien zusammen. Während des PCB-Layouts können die Werte von c und m reduziert werden, indem der Abstand zwischen parallelen Linien vergrößert wird. In der praktischen Schaltung macht die kapazitive Kopplung den größten Teil der digitalen Schaltung aus, und wenn die Leiterplattenebene nicht glatt ist oder Schlitze oder Risse vorhanden sind, hat das induktive Übersprechen einen größeren Einfluss als das kapazitive Übersprechen. Wenn jedoch die Fläche der Leiterplatte begrenzt ist, kann das Übersprechen nicht allein durch Vergrößern des Abstands zwischen parallelen Leitungen behandelt werden. Um die kleinsten verteilten Parameter zwischen zwei benachbarten parallelen Linien aufrechtzuerhalten, sollte das integrierte Ebenendesign im projektiven Bereich angeordnet sein und es ist am besten, Bodenschichten oben und unten zu haben.

b. Einfluss des Erdungskabels der Abschirmung zur Verringerung des Übersprechens

Der Grad des Übersprechens wird durch viele Elemente wie Signalfrequenz, Signalanstiegsflankenzeit, Abstand zwischen Signalleitungen, Treiberport und elektrische Eigenschaften des Empfangsports und Anzahl der PCB-Lagen bestimmt. Übersprechen kann verringert werden, indem eine integrierte Erdungsebene unter gedruckten Leitungen platziert wird, und zwischen den Signalen kann ein Erdungsdraht der Abschirmung hinzugefügt werden.

Beim PCB-Layout können zwei Aspekte hilfreich sein, um das Übersprechen zu unterbinden. Erstens sollten der empfindliche innere Kreislauf und der äußere Kreislauf gestoppt werden. Zweitens sollte das Übersprechen zwischen der inneren Schaltung oder der Rauschschaltung und anderen Signalen gestoppt werden. Beim praktischen PCB-Layout sollten detaillierte Tests in derselben Schicht oder zwischen verschiedenen Schichten in der Leiterplatte durchgeführt werden, um festzustellen, ob ein Übersprechrisiko besteht oder nicht.

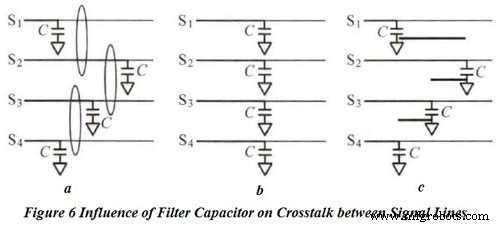

Während des Vorgangs des PCB-Layouts sollten einige Signalleitungen mit demselben Attribut dem Routing mit derselben Zeit und derselben Richtung mit Dichte folgen. Wenn der begrenzte Platz auf der Leiterplatte dazu führt, dass Filterkomponenten nicht auf derselben Leitung platziert werden können, kommt es tendenziell zu Übersprechen zwischen Signalen. Diese Situation ist in Abbildung 6 unten dargestellt.

c. Einfluss des Erdleiters der Abschirmung auf den Randeffekt

Wenn hochempfindliche Signalleitungen oder Signalleitungen mit hohem du/dt, di/dt entlang der Leiterplattenkante angeordnet sind, unterliegen sie einem höheren EMV-Risiko als diejenigen, die in der Mitte der Leiterplatte angeordnet sind. Es ist einfacher für Kantensignalleitungen, hochfrequente Störungen oder äußere Strahlung durch größere parasitäre Kapazitäten zu empfangen.

Aufgrund der Begrenzung des PCB-Bereichs ist es äußerst schwierig, das PCB-Layout gemäß den 20H-Prinzipien in der Designdatei zu erstellen. „Packet“ kann verwendet werden, um Störungen und äußere Strahlung zu reduzieren. Paketleitungen müssen keine besonderen Anforderungen wie Dicke und Form erfüllen. Wenn eine Signalleitung zu nahe an der Leiterplattenkante liegt, um Kupfer zu plattieren, kann normalerweise eine Erdungsleitung im Bereich von 7 bis 10 mils als Abschirmung hinzugefügt werden.

d. Gegenseitige Interferenz zwischen digitalen und analogen Schaltungen

Wenn eine Leiterplatte digitale Hochgeschwindigkeitsschaltungen und analoge Signale mit niedrigem Pegel enthält, wird bei einem schlechten Leiterplattenlayout normalerweise ein Übersprechen auf analoge Signale durch digitales Rauschen erzeugt. Die gegenseitige Interferenz zwischen digitalen und analogen Schaltungen wird durch die folgenden Gründe verursacht. Erstens wird Übersprechrauschen durch parasitäre Kapazität und parasitäre Induktivität verursacht. Zweitens führt die schlechte Entkopplung von Leistungswelligkeit und digitaler Chipleistung zu Leistungsrauschen. Drittens verursachen Erdungsimpedanz und Systemerdungsstelle Rauschen. Das Problem des Rauschens sollte in der Reihenfolge Leistung, Signal und Masse behandelt werden.

Hilfreiche Ressourcen:

• Die umfassendste Einführung von automatisierten EMI- und EMV-Tools

• Sicherstellung des Ersterfolgs im PCB-EMV-Design

• PCB-Partitionierungsdesignregeln zur EMV-Verbesserung

• PCB Design für Hochfrequenzschaltung und elektromagnetische Kompatibilität

• Drei Designüberlegungen zur Gewährleistung der EMV von Laptop-Leiterplatten

• PCB-Fertigungsservice mit vollem Funktionsumfang von PCBCart – Mehrere Mehrwertoptionen

• Erweiterter PCB-Montageservice von PCBCart - Beginnen Sie ab 1 Stück

Industrietechnik

- Grundlagen des PCB-Layouts

- PCB-Layout-Software

- Überlegungen zum PCB-Layout

- Eine Kurzanleitung zum PCB-Layout für Anfänger

- Überlegungen zum Impedanzdesign für starrflexible PCB

- Hochgeschwindigkeits-Layout-Tipps

- Unterdrückungsmethode der Signalreflexion im Hochgeschwindigkeits-PCB-Layout

- Ersterfolg im PCB-EMV-Design sichern

- Impedanzkontrolle von Vias und ihr Einfluss auf die Signalintegrität im PCB-Design

- Meisterfreundliche PCB-Layout-Richtlinien