Impedanzkontrolle von Vias und ihr Einfluss auf die Signalintegrität im PCB-Design

Vias spielen eine Rolle als Leiter, die Leiterbahnen über verschiedene Schichten einer mehrschichtigen PCB (Printed Circuit Board) verbinden. Bei niedriger Frequenz beeinträchtigen Vias die Signalübertragung nicht. Wenn die Frequenz ansteigt (über 1 GHz) und die ansteigende Signalflanke steiler wird (höchstens 1 ns), können Vias jedoch nicht einfach als Funktion der elektrischen Verbindung betrachtet werden, sondern der Einfluss von Vias auf die Signalintegrität muss sorgfältig berücksichtigt werden. Vias verhalten sich wie Haltepunkte mit diskontinuierlicher Impedanz auf der Übertragungsleitung und verursachen Signalreflexionen. Dennoch konzentrieren sich Probleme, die durch Vias verursacht werden, mehr auf parasitäre Kapazität und parasitäre Induktivität. Der Einfluss der parasitären Via-Kapazität auf die Schaltung besteht hauptsächlich darin, die Anstiegszeit von Signalen zu verlängern und die Laufgeschwindigkeit der Schaltung zu verringern. Eine parasitäre Induktivität kann jedoch den Beitrag der Bypass-Schaltung schwächen und die Filterfunktion des gesamten Stromversorgungssystems verringern. Dieser Artikel demonstriert, wie sich die Via-Impedanzsteuerung auf die Signalintegrität auswirkt, und gibt einige Ratschläge zum Schaltungsdesign.

Einfluss von Vias auf die Impedanzkontinuität

Gemäß der TDR-Kurve (Zeitbereichsreflektometer) zum Zeitpunkt des Vorhandenseins und Fehlens eines Durchgangs tritt eine offensichtliche Signalverzögerung in der Situation des Fehlens eines Durchgangs auf. Bei fehlender Durchkontaktierung beträgt die Zeitspanne der Signalübertragung zum zweiten Testloch 458 ps, während die der Signalübertragung zum zweiten Testloch bei vorhandener Durchkontaktierung 480 ps beträgt. Via führt also Signale um 22ps zu verzögern.

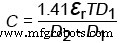

Die Signalverzögerung resultiert hauptsächlich aus der parasitären Kapazität von Vias, die durch die folgende Formel berechnet wird:

In dieser Formel D2 bezieht sich auf den Pad-Durchmesser (mm) auf dem Boden, D1 zum Paddurchmesser (mm) des Vias, T zur Leiterplattendicke (mm), εr zur Dielektrizitätskonstante des Substrats und C zur parasitären Kapazität (pF) der Durchkontaktierung.

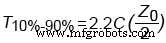

Die Länge des Vias in dieser Diskussion beträgt 0,96 mm mit einem Via-Durchmesser von 0,3 mm, einem Pad-Durchmesser von 0,5 mm und einer Dielektrizitätskonstante von 4,2, wobei die berechnete parasitäre Kapazität in der oben genannten Formel mit ungefähr 0,562 pF ermittelt wird. Wenn es sich um eine Signalübertragungsleitung mit einem Widerstand von 50 Ω handelt, verursacht diese Durchkontaktierung Änderungen in der Anstiegszeit von Signalen mit dem Änderungsbetrag, der durch die folgende Formel berechnet wird:

Basierend auf der oben eingeführten Formel beträgt die durch die Via-Kapazität verursachte Variation der Anstiegszeit 30,9 ps, was 9 ps länger ist als das getestete Ergebnis (22 ps), was darauf hinweist, dass eine Variation zwischen dem theoretischen und dem praktischen Ergebnis auftritt.

Zusammenfassend lässt sich sagen, dass die durch die parasitäre Via-Kapazität verursachte Signalverzögerung nicht so offensichtlich ist. Beim Hochgeschwindigkeits-Schaltungsdesign sollte jedoch besonders auf die Lagenkonvertierung mit mehrfach aufgebrachten Vias beim Tracing geachtet werden.

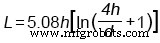

Verglichen mit der parasitären Kapazität führt die parasitäre Induktivität von Vias zu mehr Schäden an der Schaltung. Die parasitäre Induktivität von Vias kann durch die folgende Formel ermittelt werden:

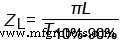

In dieser Formel bezieht sich L auf die parasitäre Induktivität (nH) des Vias, h auf die Länge (mm) des Vias und d auf den Via-Durchmesser (mm). Die durch die parasitäre Induktivität hervorgerufene äquivalente Impedanz kann durch die folgende Formel berechnet werden:

Die Anstiegszeit der Testsignale beträgt 500 ps und die äquivalente Impedanz beträgt 4,28 Ω. Aber die Impedanzänderung als Ergebnis von Durchkontaktierungen erreicht mehr als 12 Ω und zeigt an, dass der gemessene Wert extreme Abweichungen vom theoretisch berechneten Wert aufweist.

Einfluss des Via-Durchmessers auf die Impedanzkontinuität

Gemäß einer Reihe von Experimenten kann geschlussfolgert werden, dass je größer der Durchkontaktierungsdurchmesser ist, desto mehr Unstetigkeit wird die Durchkontaktierung verursachen. Bei Hochfrequenz- und Hochgeschwindigkeits-PCB-Designprozessen wird die Impedanzänderung normalerweise innerhalb des Bereichs von ±10 % gesteuert, oder es wird möglicherweise eine Signalverzerrung erzeugt.

Einfluss der Pad-Größe auf die Impedanzkontinuität

Die parasitäre Kapazität hat einen extrem großen Einfluss auf Resonanzpunkte innerhalb des Hochfrequenzsignalbands, und die Bandbreite wird zusammen mit der parasitären Kapazität unter einer Verschiebung leiden. Das führende Element, das die parasitäre Kapazität beeinflusst, ist die Pad-Größe, die einen äquivalenten Einfluss auf die Signalintegrität hat. Je größer der Pad-Durchmesser ist, desto weniger Impedanz wird nach vorne gebracht.

Wenn sich der Pad-Durchmesser im Bereich von 0,5 mm bis 1,3 mm ändert, wird die durch Vias verursachte Impedanzdiskontinuität konstant reduziert. Wenn die Pad-Größe von 0,5 mm auf 0,7 mm zunimmt, weist die Impedanz eine relativ große Änderungsamplitude auf. Wenn die Pad-Größe weiter zunimmt, wird die Via-Impedanzänderung glatt. Daher gilt:Je größer der Pad-Durchmesser ist, desto geringer ist die Impedanzdiskontinuität, die durch Vias hervorgerufen wird.

Rückweg für Via-Signale

Das Grundprinzip des Rücksignalflusses besteht darin, dass der Rücksignalstrom mit hoher Geschwindigkeit entlang des Pfades mit der niedrigsten Induktivität fließt. Da eine Leiterplatte mehr als eine Erdungsebene enthält, fließt der Rücksignalstrom direkt entlang eines Pfads unterhalb der Signalleitungen an der Erdungsebene, die der Signalleitung am nächsten ist. Wenn alle Signalströme von einem Punkt zum anderen entlang derselben Ebene fließen und Signale von einem Punkt zum anderen durch eine Durchkontaktierung fließen, kann der Rücksignalstrom nicht springen, wenn die Masseverbindung besteht. nicht erreicht.

Beim Hochgeschwindigkeits-PCB-Design kann ein Rückweg zum Via-Signalstrom bereitgestellt werden, um Impedanzfehlanpassungen zu eliminieren. Um die Durchkontaktierung herum kann die Erdungsdurchkontaktierung so ausgelegt werden, dass sie einen Rückweg für den Signalstrom mit einer zwischen der Signaldurchkontaktierung und der Erdungsdurchkontaktierung erzeugten Induktivitätsschleife bereitstellt. Sogar eine Impedanzdiskontinuität entsteht durch den Einfluss von Durchkontaktierungen, Strom kann mit verbesserter Signalqualität zur Induktivitätsschleife fließen.

Signalintegrität von Vias

S-Parameter können verwendet werden, um den Einfluss von Vias auf die Signalintegrität zu bewerten, die Eigenschaften aller Bestandteile im Kanal darstellen, einschließlich Verlust, Dämpfung und Reflexion usw. In Übereinstimmung mit einer Reihe von Experimenten, die in diesem Artikel genutzt werden, wird angezeigt, dass Erdungs-Vias geeignet sind des Reduzierens von Übertragungsverlusten, und je mehr Erdungsdurchkontaktierungen um Durchkontaktierungen herum angeordnet werden, desto geringer wird der Übertragungsverlust sein. Das Erden von Vias, die um Vias herum hinzugefügt werden, ist in der Lage, den durch Vias verursachten Verlust bis zu einem gewissen Grad zu verringern.

Gemäß der oben in diesem Artikel gezeigten Diskussion können zwei Schlussfolgerungen gezogen werden:

a. Durch Vias verursachte Impedanzsprünge werden durch Via-Durchmesser und Pad-Größe beeinflusst. Je größer der Via-Durchmesser und der Pad-Durchmesser werden, desto schwerwiegender wird die erregte Impedanzdiskontinuität sein. Durch Durchkontaktierungen verursachte Impedanzunterbrechungen nehmen normalerweise ab, wenn die Padgröße zunimmt.

b. Das Hinzufügen von Erdungs-Durchkontaktierungen ist in der Lage, die Durchkontaktierungs-Diskontinuität, die innerhalb des Bereichs von ±10 % kontrolliert werden kann, offensichtlich zu verbessern. Darüber hinaus kann das Hinzufügen von Erdungsdurchkontaktierungen die Signalintegrität offensichtlich erhöhen.

Benötigen Sie einen PCB-Fertigungsservice mit strenger Impedanzkontrolle? PCBCart kann das!

PCBCart ist in der Lage, Leiterplatten mit kontrollierter Impedanz gemäß Ihren Anforderungen herzustellen. Unsere Impedanztoleranz liegt zwischen ±5 % und ±10 %. Klicken Sie auf die Schaltfläche unten, um Online-Herstellungskosten für Leiterplatten mit Impedanzkontrolle zu erhalten.

Hilfreiche Ressourcen

• Elemente, die die charakteristische Impedanz von PCB und Lösungen beeinflussen

• Impedanzkontrolle beim PCB-Design von digitalen Hochgeschwindigkeitsschaltungen

• PCBCart bietet PCB-Fertigungsservices mit allen Funktionen

• PCB-Design Dateianforderungen für eine effiziente Herstellung von Leiterplatten

• So bewerten Sie einen Leiterplattenhersteller oder einen Leiterplattenbestücker

Industrietechnik

- Signalintegrität &PCB

- PCB-Materialien und Design für Hochspannung

- Flex- und Starrflex-Biegefähigkeiten im PCB-Design

- Was ist PCB via Tenting?

- Schritte und Verfahren zum Schutz Ihres PCB-Designs

- Überlegungen zum Impedanzdesign für starrflexible PCB

- Auswirkung von schlecht ausgeführten, mit Lötmasken verschlossenen Vias auf Via-Kupfer von PCB und Lösungen

- Rückschläge und Lösungen im HF-PCB-Design

- 3 Routing-Techniken beim PCB-Design von Hochgeschwindigkeits-Signalschaltungen

- Differentiale isometrische Verarbeitung und Simulationsverifizierung von Hochgeschwindigkeits-PCB-Design