Impedanzsteuerung beim PCB-Design von digitalen Hochgeschwindigkeitsschaltungen

Impedanzsteuerungstechnologien sind sehr wichtig beim Entwurf digitaler Hochgeschwindigkeitsschaltkreise, bei denen effektive Methoden angewendet werden müssen, um die hervorragende Leistung von Hochgeschwindigkeits-PCBs sicherzustellen.

Impedanzberechnung und Impedanzsteuerung von Hochgeschwindigkeitsübertragungsleitungen auf PCB

• Äquivalentes Modell auf Übertragungsleitungen

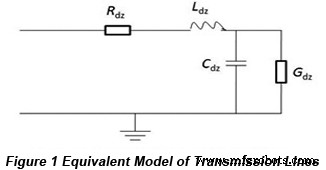

Abbildung 1 zeigt den äquivalenten Effekt von Übertragungsleitungen auf PCBs, bei denen es sich um eine Struktur handelt, die Tandem- und Mehrfachkondensatoren, Widerstände und Induktoren (RLGC-Modell) umfasst.

Der typische Wert des Tandemwiderstands liegt im Bereich von 0,25 bis 0,55 Ohm/Fuß, und der Widerstandswert mehrerer Widerstände bleibt normalerweise recht hoch. Mit parasitären Widerständen, Kapazitäten und Induktivitäten, die in PCB-Übertragungsleitungen hinzugefügt werden, wird die Gesamtimpedanz auf Übertragungsleitungen als charakteristische Impedanz (Z0 ). Der Wert der charakteristischen Impedanz ist unter der Bedingung relativ klein, dass der Leitungsdurchmesser groß ist, die Leitung nahe an Strom/Masse liegt oder die Dielektrizitätskonstante hoch ist. Abbildung 3 zeigt das Ersatzmodell der Übertragungsleitung mit einer Länge von dz, aus der sich der Wellenwiderstand der Übertragungsleitung als Formel ableiten lässt: . In dieser Formel bezieht sich L auf die Induktivität jeder Längeneinheit auf der Übertragungsleitung, während C sich auf die Kapazität jeder Längeneinheit auf der Übertragungsleitung bezieht.

. In dieser Formel bezieht sich L auf die Induktivität jeder Längeneinheit auf der Übertragungsleitung, während C sich auf die Kapazität jeder Längeneinheit auf der Übertragungsleitung bezieht.

• Berechnungsformel für Impedanz und Verzögerung von Übertragungsleitungen auf PCB

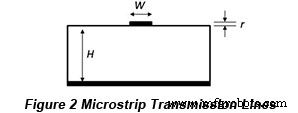

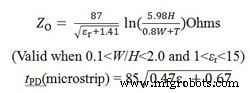

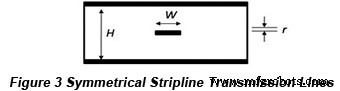

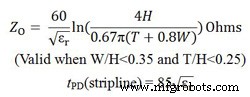

| Übertragungsleitungen auf PCB | Berechnungsformel für Impedanz und Verzögerung |

|  |

|  |

In den obigen Formeln Z0 bezieht sich auf die Impedanz (Ohm), W bezieht sich auf die Breite der Leitungen (Zoll), T bezieht sich auf die Dicke der Leitungen (Zoll), H bezieht sich auf den Abstand zum Boden (Zoll), bezieht sich auf die relative Dielektrizitätskonstante des Substrats, und tPD bezieht sich auf die Verzögerungszeit (ps/inch).

• Layoutregeln für die Impedanzsteuerung von Übertragungsleitungen

Basierend auf der obigen Analyse ist die Einheitsverzögerung von Impedanz und Signal nicht relativ zur Frequenz der Signale, sondern hängt mit der Platinenstruktur, der relativen Dielektrizitätskonstante des Platinenmaterials und den physikalischen Eigenschaften des Routings zusammen. Diese Schlussfolgerung ist äußerst wichtig für das Verständnis von Hochgeschwindigkeits-Leiterplatten und für das Hochgeschwindigkeits-Leiterplattendesign. Darüber hinaus ist die Übertragungsgeschwindigkeit der Signalübertragungsleitung in der Außenschicht viel schneller als in der Innenschicht, sodass diese Elemente bei der Anordnung der Schlüsselleitungen berücksichtigt werden müssen.

Impedanzkontrolle ist die wesentliche Voraussetzung für die Umsetzung der Signalübertragung. Gemäß der Platinenstruktur und der Impedanzberechnungsformel von Übertragungsleitungen hängt die Impedanz jedoch nur vom PCB-Material und der PCB-Schichtstruktur ab, wobei die Leitungsbreite und die Routing-Merkmale für dieselbe Leitung unverändert bleiben. Daher ändert sich die Impedanz einer Leitung auf verschiedenen PCB-Schichten nicht, was beim Hochgeschwindigkeits-Schaltungsdesign nicht zulässig ist.

Für diesen Artikel wurde eine Hochgeschwindigkeits-PCB mit hoher Dichte entwickelt, und die meisten Signale an Bord haben Impedanzanforderungen. Beispielsweise sollte die CPCI-Signalleitung eine Impedanz von 65 Ohm, ein Differenzsignal von 100 Ohm und andere Signale jeweils alle 50 Ohm haben. Je nach Leiterplatten-Routingraum muss ein mindestens zehnlagiges Routing verwendet und ein 16-lagiger PCB-Designplan festgelegt werden.

Da die Gesamtdicke der Platte 2 mm nicht überschreiten darf, gibt es einige Schwierigkeiten beim Stapeln, wobei einige Probleme berücksichtigt werden:

1). Jede Signalschicht hat benachbarte Bildebenen, um die Impedanz und Signalqualität zu schützen.

2). Neben jeder Leistungsebene befindet sich eine vollständige Erdungsschicht, sodass die Leistung der Leistung gut gewährleistet werden kann.

3). Das Stapeln von Brettern erfordert ein Gleichgewicht, wobei ein Verziehen des Bretts vermieden wird.

Die Dielektrizitätskonstante des Mediums wird auf 4,3 eingestellt. Basierend auf dem obigen Stacking-Design sollten die Linienbreite und der Abstand zwischen den Linien entsprechend dem Berechnungsergebnis eingestellt werden, um die Anforderung an die Signalimpedanz sicherzustellen. Die Linienbreite wird als folgendes Ergebnis erhalten:

1). Die Breite der Signalleitung auf der Oberflächenschicht beträgt 5 mils mit einer Impedanz von 58,7 Ohm.

2). Die Breite der CPCI-Signalleitung auf der Oberflächenschicht beträgt 4,5 mils mit einer Impedanz von 61,7 Ohm.

3). Die Breite der Signalleitung in der inneren Schicht beträgt 4,5 mils mit einer Impedanz von 50,2 Ohm.

4). Die Breite der Linien im BGA-Bereich in der Innenschicht und der Oberflächenschicht beträgt 4 mils mit einer Oberflächenschichtimpedanz von 64,6 Ohm und einer Innenschichtimpedanz von 52,7 Ohm.

5). Die Breite der Mikrostreifen-Differentialleitung in der Innenschicht beträgt 5 mil, der Abstand zwischen den Leitungen 6 mil und die Impedanz 100,54 Ohm.

6). Die Breite der Streifenleitungs-Differentialleitung in der inneren Schicht beträgt 4,5 mil mit einem Abstand zwischen den Leitungen von 10 mil und einer Impedanz von 96,6 Ohm.

Der Abstand zwischen den Linien wird wie folgt eingestellt:

1). Der Abstand zwischen den Signalleitungen (5 mils) auf der Oberflächenschicht beträgt 5,0 mils.

2). Der Abstand zwischen den CPCI-Signalleitungen (4,5 mils) auf der Oberflächenschicht beträgt 9,0 mils.

3).. Der Abstand zwischen den Signalleitungen (4,5 mils) auf der inneren Schicht beträgt 7,0 mils.

4). Der Abstand zwischen den Linien auf der Oberflächenschicht und der Innenschicht beträgt 4,0 mils.

5). Der Abstand zwischen Differentialsignalleitungen auf der Innenschicht und zwischen ihnen und anderen Signalleitungen sollte mindestens 25 mil betragen.

6). Der Abstand zwischen Differentialsignalleitungen auf der Oberflächenschicht und zwischen ihnen und anderen Signalleitungen sollte mindestens 20 mil betragen.

Nach dem PCB-Druck wird die Impedanz der Testplatine mit dem POLAR-Cits500-Impedanztester mit den Ergebnissen in der folgenden Tabelle getestet. Die Daten zeigen, dass die Impedanz im Prozess des Designs und der Herstellung von Hochgeschwindigkeits-Leiterplatten im Bereich von 50 Ohm-%, 60 Ohm-% und 100 Ohm-% kontrolliert werden muss.

| Voreingestellte Impedanz (Ohm) | Praktische Impedanz (Ohm) |

| 50 | 47,52–52,33 |

| 60 | 57,65–61,35 |

| 100 | 93,65–106,35 |

LVDS und seine Impedanzkontrolle auf PCBs

• LVDS

LVDS ist eine Art serieller Hochgeschwindigkeitssignalübertragungspegel mit den Vorteilen hoher Übertragungsgeschwindigkeit, geringem Stromverbrauch, starker Entstörungsfähigkeit, großer Übertragungsentfernung und praktikabler Anpassung. Die Anwendungsgebiete von LVDS umfassen Computer, Kommunikation und Konsum.

• Impedanzdesign von LVDS

LVDS weist einen Spannungshub von nur 350 MV mit der längsten Übertragungsdistanz von über 10 Metern auf. Um sicherzustellen, dass Signale bei der Signalübertragung in Übertragungsleitungen nicht durch reflektierte Signale beeinflusst werden, muss die Impedanz der Übertragungsleitungen mit einer Einzelleitungsimpedanz von 50 Ohm und einer Differenzimpedanz von 100 Ohm unter Kontrolle sein. In der praktischen Anwendung kann die Impedanz durch Einstellen angemessener Stapeldicken- und Mediumparameter, Anpassen der Linienbreite und des Abstands zwischen Linien und Berechnen der Impedanz einzelner Linien und differentieller Linien mit Hilfe einiger Hochgeschwindigkeits-Simulationsanalysewerkzeuge kontrolliert werden.

Meistens ist es jedoch relativ schwierig, die Anforderungen der Einzelleitungsimpedanz und der differentiellen Impedanz zu erfüllen. Einerseits wird der Einstellbereich der Linienbreite W und des Linienabstands S durch den physikalischen Designraum gesteuert. Beispielsweise wird das Routing und die Linienbreite in den Randverbindern mit BGA oder DIP von Padgröße und -abstand beeinflusst. Andererseits beeinflusst die Änderung von W und S das Ergebnis von Einzelleitungs- und Differenzimpedanz. Bisher war es einfach und bequem, das Verhältnis zwischen voreingestellter Linienbreite und Linienabstand herauszufinden.

• LVDS-Routing-Regeln

Im Allgemeinen wird das differenzielle Signalrouting gemäß den Impedanzdesignregeln implementiert, wodurch die LVDS-Qualität sichergestellt werden kann. Beim praktischen Routing sollte LVDS den folgenden Regeln entsprechen:

1). Differentialpaare sollten so kurz wie möglich sein, Leitungen sollten gerade sein und die Anzahl der Durchgangslöcher sollte verringert werden. Der Abstand zwischen Signalleitungen in differentiellen Paaren sollte gleich sein. All diese Regeln tragen dazu bei, lange Streckenführungen und zahlreiche Abzweigungen zu vermeiden. Bei Abbiegungen sollte eine 45-Grad-Abbiegung anstelle von 90 Grad verwendet werden.

2). Der Abstand zwischen differentiellen Paaren sollte über das 10-fache beibehalten werden, um das Übersprechen zwischen den Leitungen zu verringern. Bei Bedarf können Erdungsdurchgangslöcher zur Isolierung zwischen Differentialpaaren platziert werden.

3). LVDS kann nicht über die Oberfläche aufgeteilt werden. Obwohl zwei differentielle Signale wechselseitige Rückpfade sind, kann der Signalrückpfad nicht als Ergebnis einer oberflächenübergreifenden Teilung abgeschnitten werden. Trotzdem führen Übertragungsleitungen aufgrund fehlender Bildebenen möglicherweise zu Impedanzsprüngen.

4). Vermeiden Sie unterschiedliche Signale zwischen den Schichten. Während der Leiterplattenherstellung ist die Stapelausrichtungsgenauigkeit zwischen Schichten viel geringer als die Ätzgenauigkeit in derselben Schicht plus der mittlere Verlust während des Stapelns, was alles zu einer Änderung der differentiellen Impedanz zwischen differentiellen Paaren führt.

5). Beim Impedanzdesign sollte die Kopplungsmethode verwendet werden.

6). Es sollte eine geeignete PCB-Stapelstruktur festgelegt werden, um die Isolierung zwischen Spannungspegelsignalen und LVDS sicherzustellen. Wenn möglich, können Signale wie Hochgeschwindigkeits-TTL/CMOS auf verschiedene Schichten gelegt werden, die durch Masse- und Leistungsschichten vom LVDS-Routing isoliert sind.

7). Differenzsignalpaare sollten mit der Länge des Routings kompatibel sein.

Hilfreiche Ressourcen

• Elemente, die die charakteristische Impedanz von Leiterplatten und Lösungen beeinflussen

• Überlegungen zum Impedanzdesign für starrflexible Leiterplatten

• Wie man die Impedanz von Hochgeschwindigkeits-Leiterplattenleistung analysiert und verhindert

• Impedanzkontrolle von Durchkontaktierungen und ihr Einfluss auf die Signalintegrität im PCB-Design

• Vollfunktions-PCB-Fertigungsservice von PCBCart – mehrere Mehrwertoptionen

• Erweiterter PCB-Bestückungsservice von PCBCart – ab 1 Stück

Industrietechnik

- PCB-Layout-Software

- Ursachen von PCB-Korrosion

- Überlegungen zum PCB-Layout

- Überlegungen zum Impedanzdesign für starrflexible PCB

- Rückschläge und Lösungen im HF-PCB-Design

- 3 Routing-Techniken beim PCB-Design von Hochgeschwindigkeits-Signalschaltungen

- Hochgeschwindigkeits-Layout-Tipps

- Signalintegritätsanalyse und PCB-Design auf gemischten Hochgeschwindigkeits-Digital-Analog-Schaltkreisen

- Hochgeschwindigkeits-PCB-Design-Herausforderungen zur Signalintegrität und ihre Lösungen

- Impedanzkontrolle von Vias und ihr Einfluss auf die Signalintegrität im PCB-Design