Entwurf und Implementierung von FDR-Verbindungsschalttafeln mit hoher Dichte

Heutzutage hat sich die Übertragungsrate von Hochleistungs-Computerverbindungsnetzwerken mit der Anwendung von serieller Hochgeschwindigkeitsübertragung zu FDR (Fourteen Data Rate, 14 Gb/s) entwickelt, der 4. Generation der primären SDR (Single Data Rate, 2,5 Gb/s). s), DDR (Double Data Rate, 5 Gb/s) und QDR (Quad Data Rate, 10 Gb/s). Das Design von PCB (Printed Circuit Board) mit Verbindungs- und Schaltplatinen und Schnittstellenkarten, die für die Bildung des Internets unerlässlich sind, ist in das FDR-Hochgeschwindigkeits- und Hochfrequenzfeld eingetreten. Da die Anstiegszeit des FDR-Signals drastisch auf die Größenordnung von 10 ps reduziert wurde, ist eine Reihe von Problemen bezüglich der Signalintegrität zu den Schlüsselmerkmalen geworden, um die Möglichkeit der Implementierung von Funktionen und des zuverlässigen Betriebs zu bestimmen, wie z. B. Dämpfung, Übersprechen, Reflexion, elektromagnetische Interferenz usw Basierend auf den Merkmalen von FDR-Verbindungschips, einschließlich mehrerer Ports, mehrerer Kanäle, mehrerer Leistungskategorien und eines hohen Energieverbrauchs, müssen immer mehrere Verbindungschips auf einer einzigen Verbindungsplatine integriert werden, um die Durchsatzrate zu erhöhen. Auf einer Platine mit begrenztem Platz müssen einerseits einige Anforderungen erfüllt werden, darunter Komponentenlayout und Wärmeableitung, Routing mit hoher Dichte, Langstreckenübertragung über die Rückseite der Platine und Integrität aller Arten von Signalen. Auf der anderen Seite müssen einige Elemente berücksichtigt werden, darunter der PCB-Designzeitraum, Einschränkungen der PCB-Fertigungstechnik und Kostenkontrolle. Daher ist es extrem schwierig für die Designimplementierung und die Simulationsverifizierung. Basierend auf einem PCB-Designbeispiel für FDR-Verbindung und Schaltplatine stellt dieser Artikel einige Optimierungsmethoden in Bezug auf die Auswahl des Substratmaterials, das Stapeldesign, die Routing-Regeln und das Anti-Interferenz-Design vor, um das Integritätsproblem aller Arten von Signalen zu lösen den Prozess des FDR-Hochgeschwindigkeits-PCB-Designs.

Dämpfungsattribut und Auswahl des Substratmaterials

Bei FDR-Hochfrequenzsignalen ist der Übertragungsleitungsverlust das Problem bezüglich der Signalintegrität. Wenn FDR-Signale von einem Sendeterminal zu einem Empfangsterminal entlang Verbindungskanälen übertragen werden, hat, weil die Hochfrequenzdämpfung viel größer als die Niederfrequenzdämpfung ist, eine ernsthafte Verformung der am Empfangsterminal ankommenden Signalwellenform stattgefunden. Die Verformung wird hauptsächlich in zwei Aspekte eingeteilt:Der Spannungshub von Signalen hat stark abgenommen, während eine starke Verschlechterung bis zur Signalanstiegsflanke stattgefunden hat. Ersteres begrenzt die Übertragungsdistanz von Signalen, während letzteres zu Interferenzen zwischen Codes führt. Der Übertragungsleitungsverlust A kann als Summe der Leitungsverluste Acond betrachtet werden und dielektrischer Verlust Adiel wie in Formel (1) gezeigt:A =Adiel + ABedingung .

Leitungsverlust bezieht sich auf den Verlust, der durch den Serienwiderstand am Kupferleiter zwischen Signalweg und Rückweg verursacht wird. Im Hochfrequenzbereich lässt der Skin-Effekt Strom an der Oberfläche der umgebenden Kupferleiter fließen. Mit zunehmendem äquivalenten Serienwiderstand von Kupferleitern steigt der Leiterverlust mit steigender Frequenz, die positiv proportional zur Quadratwurzel der Frequenz ist, was in Formel (2) dargestellt ist: .

.

Der dielektrische Verlust bezieht sich auf den Verlust, der durch das Medium des Substratmaterials erzeugt wird, hauptsächlich bestimmt durch die Eigenschaft des Materials und unabhängig von der geometrischen Konstruktion, einschließlich der Leiterbreite, positiv proportional zur Frequenz, was in Formel (3) gezeigt ist: .

.

Basierend auf Formel (2) ist die Erhöhung der Linienbreite in der Lage, Leiterverluste zu reduzieren. Beim praktischen PCB-Design kann die Breite der Leiter jedoch aufgrund der Begrenzung des Abstands zwischen Pins, der Platine, der Anzahl der Signalschichten und der Impedanz niemals unendlich breit sein. Die üblicherweise angewendete Leiterbreite/-abstand/-breite im FDR-Design beträgt normalerweise 7 mil/7 mil/7 mil oder 8 mil/10 mil/8 mil. Bei gleicher Leiterbreite ist der Leiterverlust positiv proportional zur Leiterlänge, ohne Bezug zum Material. Um den Gesamtübertragungsverlust zu reduzieren, muss daher nur der dielektrische Verlust berücksichtigt werden. Basierend auf Formel (3) ist der dielektrische Verlust proportional zum Verlustfaktor und die Anwendung kleiner Verlustfaktoren kann zur Reduzierung des dielektrischen Verlusts hilfreich sein, was zu einem Verlust der Gesamtübertragung führt.

Tabelle 1 listet die Attributparameter von drei gewöhnlichen Hochgeschwindigkeitsplatinenmaterialien und Verlustwerten auf, die gemäß den Formeln (1), (2) und (3) berechnet wurden, wenn die Übertragungsrate 14 Gb/s, die Leiterbreite 8 mil und die Impedanz 50 Ω beträgt>

| Plattenmaterialparameter | FR4 | Nelco4000-13SI | Megtron6 |

| [email protected] | 0,02 | 0,008 | 0,004 |

| [email protected] | 4.10 | 3.200 | 3.600 |

| Acond @7GHz/Zoll | 0,24 | 0,240 | 0,240 |

| Eindiel @7GHz/Zoll | 0,65 | 0,230 | 0,120 |

| [email protected]/in | 0,89 | 0,470 | 0,360 |

| [email protected]/30in | 27.00 | 14.000 | 11.000 |

| Relative Kosten | 1,00 | 3.500 | 8.000 |

Es kann angegeben werden, dass bei einer Übertragungsrate von 14 Gb/s und einer Übertragungslänge von 30 Zoll der Gesamtübertragungsverlust von Nelco4000-13SI ungefähr 14 dB beträgt, während die Spannungshubdämpfung, der ein typischer FDR-Chip standhalten kann, im Bereich von 20 dB bis liegt 25dB. Daher kann diese Art von Platinenmaterial im Design von FDR-Verbindungsschaltplatinen mit einer Übertragungsdistanz von weniger als 30 Zoll verwendet werden. Die Gesamtübertragungsdämpfung von FR4 beträgt jedoch ungefähr 27 dB, und FR4 kann nicht für FDR-Designs für große Entfernungen angewendet werden, aber FDR-Verbindungsschnittstellenkarten mit kurzer Übertragungsentfernung dürfen FR4 auswählen, um die Kosten zu senken. Was Megtron6 betrifft, dessen Gesamtübertragungsdämpfung am kleinsten ist, weist es die höchsten Kosten auf, und seine Anwendung in FDR führt zu einer Erhöhung der Systemarchitekturgebühren. Zusammenfassend lässt sich sagen, dass das Platinenmaterial für Hochfrequenz-Leiterplatten die Grundlage ist und die Auswahl des Platinenmaterials die Übertragungslänge von Signalen bestimmt.

Layout und Stapeldesign

Für das PCB-Design müssen zunächst die Leiterplattenstruktur und der Stapel berücksichtigt werden. Normalerweise wurden das Muster und die Form der Leiterplatte bestimmt, und die Bestimmung der Stapelzahl liegt in der Signalfrequenz, der Leiterplattenstiftdichte, den Herstellungskosten der Leiterplatte, der Herstellungsdauer und den Zuverlässigkeitsanforderungen. FDR-Verbindungsschalttafeln haben eine hohe Frequenz und Dichte, und die Anwendung von Mehrschichtplatinen ist der notwendige Schritt, um Interferenzen zu reduzieren. Außerdem ist die Bestimmung der Stapelzahl entscheidend.

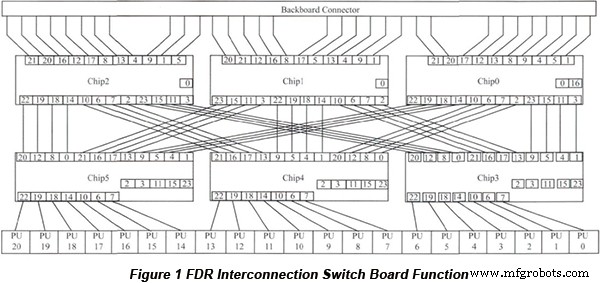

Es gibt 24 Ports auf dem FDR-Verbindungschip und jeder Port verfügt über 8 Tx-Kanäle und 8 Rx-Kanäle in der Betriebsmethode der Kopplung. 6 Verbindungschips und 3 Downlink-Chips werden von der FDR-Verbindungsplatine angewendet, und auf 32 Ports wird über den Backboard-Anschluss zugegriffen. 3 Uplink-Chips greifen über optische QSFP-Fasern (Quad Small Form-factor Pluggable) auf 21 Ports zu. Uplink-Chip und Downlink-Chip sind über 4 Ports miteinander verbunden, was in Abbildung 1 dargestellt ist.

FDR verfügt über das BGA-Gehäuse (Ball Grid Array) mit einer Fläche von 50 mm x 50 mm, 1157 Pins und einem Abstand von 1,0 mm, und P/N-Pins an den Ports von Tx und Rx sind gemäß 3 konzentrischen Kreisen verteilt. Theoretisch können 3 Signalschichten aufgebracht werden, um alle Pins an allen Ports aus dem BGA herauszuführen. Unter Berücksichtigung der folgenden beiden Elemente können zwei Signalschichten verwendet werden, um auf eine Gruppe von Stiften aus konzentrischen Kreisen zuzugreifen.

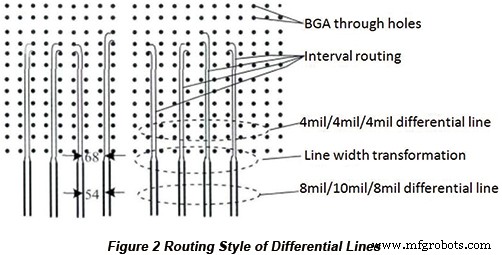

a. Aufgrund der Begrenzung des Abstands beträgt die Linienbreite / der Abstand / die Breite der Differenzlinien 4 mil / 4 mil / 4 mil und wird auf 8 mil / 10 mil / 8 mil erweitert, die aus BGA kommen, und der Abstand zwischen den Differenzlinienpaaren sollte nicht kleiner sein als 50 Mio. Daher muss ein Differenzleitungspaar eine Breite von 2 mm einnehmen und 48 Signalpaare befinden sich entlang der Kante mit der größten Dichte. Daher ist es schwierig, diese Methode zu implementieren.

b. Der Abstand zwischen den BGA-Pins beträgt 1 mm. Wenn eine Signalschicht angewendet wird, um auf eine Gruppe konzentrischer Kreissignale zuzugreifen, beträgt der Abstand zwischen differentiellen Leitungspaaren unter BGA nur 14 mil, was weit von den erforderlichen 50 mil entfernt ist. Darüber hinaus beträgt die maximale Parallelführungslänge nur 20 mm, wodurch ein gewisses Übersprechen erzeugt wird.

Um die oben erwähnten negativen Faktoren zu vermeiden, werden zwei Signalschichten angewendet, um auf eine Gruppe konzentrischer Kreissignale zuzugreifen, und das Differenzsignal an jeder Signalschicht muss gemäß einem Abstand von 50 mil aus dem BGA herausgeführt werden. Daher sind bei FDR-Verbindungsplatinen mindestens 6 Lagen erforderlich, um alle aus dem BGA herausgeführten Differenzsignale herzustellen. Unter Berücksichtigung der Konnektivitäts- und Routing-Menge der Platine und genügend Platinenfläche für den Austauschkopplungskondensator werden 8 interne Signale und ein Stapel mit 22 Schichten angelegt.

Nebensprechanalyse und Reduzierungsmaßnahmen

Übersprechen ist die erste Überlegung in Bezug auf das Design von Schaltungen mit hoher Geschwindigkeit und hoher Dichte. Wenn sich Spannung und Strom in der Angriffsleitung ändern, findet eine elektromagnetische Kopplung durch gegenseitige Kapazität und gegenseitige Induktivität zwischen Angriffsleitung und Opferleitung statt. Das Nebensprechen, das entlang der Opferleitung zum Sendeanschluss fließt, wird Nebensprechen nahe dem Anschluss genannt, während das Nebensprechen, das entlang der Opferleitung zum Empfangsanschluss fließt, Nebensprechen des fernen Anschlusses genannt wird. Im Allgemeinen sollte die Gesamtrauschspannung auf der Opferleitung auf weniger als 5 % der Signalspannung geregelt werden. Es ist am besten, das Crosstalk-Budget der Single-Edge-Offensivlinie innerhalb von 1 % zu kontrollieren, wobei andere Rauschquellen und Offensivlinien um zwei Seiten der Opferlinie berücksichtigt werden.

Zu den wichtigsten Punkten in Bezug auf die Verringerung des Übersprechens gehören:

a. Der Abstand zwischen Offensive Line und Victim Line sollte vergrößert und die Parallelführungslänge verringert werden.

b. Die integrierte Masse wird als Rückweg der Signale angelegt. Gemäß dem empirischen Gesetz beträgt für die Streifenleitung von 50 Ω, wenn der Abstand das Dreifache der Leitungsbreite beträgt, das Nahnebensprechen ungefähr 0,5 %. Bei einer Mikrostreifenleitung von 50 Ω beträgt das Nahnebensprechen ungefähr 1 %, wenn der Abstand das Dreifache der Leitungsbreite beträgt. Das Nebensprechen am fernen Ende auf Streifenleitungen oder vollständig eingebetteten Mikrostreifenleitungen ist nahezu null und die Polarität des Nebensprechens am fernen Ende von Mikrostreifen-Übertragungsleitungen ist negativ und relativ groß, da der Einfluss der induktiven Kopplung größer ist als die der kapazitiven Kopplung.

• Intervall-Routing

Bei diesem Design beträgt die differentielle Impedanz der Hochgeschwindigkeits-Differentialleitung 100 Ω. Basierend auf dem Feldlöser Si9000 wird die Linienbreite/der Abstand/die Linienbreite mit 8 mil/10 mil/8 mil berechnet. Je breiter die Leitung ist, desto geringer ist die Dämpfung und der Abstand von 10 mil dient dazu, die differentielle Impedanz von 100 Ω aufrechtzuerhalten. Diese Art von Differenzleitung wird außerhalb des BGA-Chipbereichs aufgebracht. Um das Übersprechen zu verringern, beträgt der Abstand zwischen zwei Differenzleitungspaaren nicht weniger als 80 mil. The spacing between pins of interconnection chip in this article is 1mm and the through hole size limitation of BGA makes the line width/spacing/line width of the differential line in the BGA chip area 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

Industrietechnik

- So dokumentieren Sie Kabel und Kabelbäume

- Was sind Power Hammers? - Arten, Design und Betrieb

- Kundenspezifische Hightech-Leiterplatten

- Richtlinien für das HF- und Mikrowellendesign

- PCB-Materialien und Design für Hochspannung

- Flex- und Starrflex-Biegefähigkeiten im PCB-Design

- Rückschläge und Lösungen im HF-PCB-Design

- Wolfram

- Der Design- und Implementierungsprozess der Anlagenautomatisierung

- Der Aufstieg von Verbindungsleiterplatten mit hoher Dichte