Elemente, die ein hervorragendes PCB-Pad-Design für QFN gewährleisten

Mit der Entwicklung von Gehäusetechnologien für elektronische Komponenten in Richtung Miniatur, geringes Gewicht und hohe Leistung war es ein Entwicklungstrend elektronischer Komponenten, die Funktionsdichte der Komponenten zu erhöhen und den Abstand zwischen Eingangsanschlüssen und Ausgangsanschlüssen zu verringern, was am besten durch die automatische Montagetechnologie dargestellt wird B. durch SMT (Surface Mount Technology). Um die Oberflächenmontage von Bauteilen zu realisieren, besteht der erste Schritt darin, entsprechende Pads auf der Leiterplatte herzustellen, so dass eine strukturierte Leiterplatte erhalten werden kann. Dann wird die Schablonendrucktechnologie angewendet, um Lötpaste auf der Oberfläche von PCB-Pads zu bedecken. Schließlich wird ein Erhitzen durchgeführt, um die Lötpaste in eine Flüssigkeit umzuwandeln, die eine Flüssigkeitsbrücke zwischen den Stiften der Komponenten und dem PCB-Pad bildet. Unter dem Einfluss des Lötstopplacks auf der Leiterplatte wird das Schmelzen der Lötpaste im entsprechenden Lötpadbereich begrenzt, um eine Brückenbildung zwischen den Lötstellen zu verhindern, so dass eine automatische Bestückung des Chips auf der Leiterplatte implementiert wird. Entsprechend den verschiedenen Gehäusetypen werden hauptsächlich kreisförmige und rechteckige Lötpads ausgewählt, dh BGA- (Ball Grid Array) und QFN-Gehäuse (Quad Flat No-Lead). Wenn Sie mehr über BGA erfahren möchten, genügen VIER Schritte.

QFN-Wiki

Im Vergleich zu anderen Komponenten mit unterschiedlichen Gehäusetypen ist das QFN-Gehäuse so konzipiert, dass es direkt auf ein PCB- oder FPC-Substrat gelötet werden kann. Es ist in der Lage, aufgrund seiner freiliegenden Metallpads an der Unterseite eine bessere Wärmeableitung zu bieten. Darüber hinaus bietet das QFN-Gehäuse eine hervorragende elektrische Leistung, da seine Pins kürzer sind als die von Komponenten mit erweitertem Gehäuse. Daher ist es von großer Bedeutung, QFN-Pads auf der Leiterplatte so zu entwerfen, dass eine hohe Zuverlässigkeit und Leistung der Leiterplatte aufrechterhalten und sichergestellt werden kann.

Benetzungswinkel

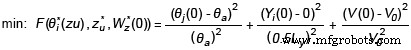

Da die Größe der QFN-Stifte und der Abstand zwischen den Stiften relativ klein sind, kann es aufgrund der genauen Menge an Zinnpastenbeschichtung zu Lötstellenbrücken oder Pseudolötungen kommen. Also ein angemessenes Design auf der Pad-Größe der Leiterplatte basierend auf der Dicke der Schablone (h0 ) ist sehr hilfreich für die Erfolgsrate des Lötens. Angenommen, der Benetzungswinkel von Lötzinn auf dem Lötpad (θa ) beträgt 30° und der Benetzungswinkel von Lötzinn auf dem Lötstopplack (θr ) beträgt 160°. Wenn die Rauheit der Pad-Oberfläche vernachlässigt wird, kann der Benetzungswinkel ungefähr als Fortschreit- oder Rückzugswinkel der dreiphasigen Kontaktlinie angesehen werden. In Übereinstimmung mit dem praktischen Löthandwerk von QFN-Komponenten ist eine vernünftige Kontrolle der Temperaturkurven des Reflow-Lötens unter idealen Bedingungen mit vollständig geschmolzenem Lötzinn und benetzter Pad-Oberfläche in der Lage, sowohl die Löteffizienz sicherzustellen als auch den Komponenten zu helfen, ein automatisches Lötgleichgewicht zu erreichen. Wenn das Pad vernünftig gestaltet ist, erfüllt der ideale Zustand der Lötstellen nicht nur die Anforderungen an die elektrische Leistung der Leiterplatte und die mechanische Verbindung, sondern vermeidet auch das Versagen von Lötstellen wie Brückenbildung und Pseudolöten. Vor diesem Hintergrund muss der Zustand von Lötstellen folgenden Formeln entsprechen:

a. Wenn Lötverbindungen innerhalb des QFN vollständig auf dem PCB-Pad verteilt sind, θa ≤θj (Zu )≤θr , θj (0)=30°, x3 (0)=x4 (0)=Dx4

b. Wenn Zinn außerhalb des QFN in das Seitenpad hineinwächst,

(1) θj (Zu )=θs3 +90°, θ4 (0) =30°, θ3 (0)=30°,

(2) x3 (0)=x4 (0)=Dx4 (0), x3 (Zu )=0.

Pad-Design

In dieser Formel θs3 gleich θa ist beides sind die Benetzungswinkel von Lötzinn auf dem Seitenpad.

In vertikaler Richtung lautet die Gleichung des statischen Gleichgewichts der Brückenflüssigkeit:

Pd Ly (x3 (0)-x4 (0)+Lx )+Wz -[T(x3 (0)-x4 (0)+Lx )(sinθ2 (0)+sinθ1 (0))+TLy (sinθ3 (0)+sinθ4 (0))]-ρgV0 =0

Die Druckintensität an der Unterseite von Lötstellen (Pd ) ist:Pd =[T(x3 (0)-x4 (0)+Lx )(sinθ2 (0)+sinθ1 (0))+TLy (sinθ3 (0)+sinθ4 (0)) + ρgV0 -Wz ]/[Ly (x3 (0)-x4 (0)+Lx )]

In diesen Formeln bezieht sich ρ auf die Flüssigkeitsdichte von Lötzinn; T bezieht sich auf die Oberflächenspannung der Lötstellenflüssigkeit; x3 (0) und x4 (0) bezieht sich auf den Schlupf von zwei Enden von flüssigen Lötverbindungen an der unteren Lötpadflüssigkeit; θ1 (0) und θ2 (0) bezieht sich auf Kontaktwinkel auf beiden Seiten, die durch die Flüssigkeits-Gas-Grenzfläche auf beiden Seiten der Lötverbindungen und der unteren Pad-Oberfläche gebildet werden, während θ 3 (0) und θ4 (0) sich auf Kontaktwinkel an beiden Enden beziehen, die durch die Flüssigkeits-Gas-Grenzfläche auf beiden Seiten gebildet werden; V0 bezieht sich auf das Volumen der Lötstelle; Wz bezieht sich auf die aufgebrachte Kraft des Pads am Ende des Chips und der Lötstelle in vertikaler Richtung.

Unter der Grenze der Formeln (1) und (2) können Rahmenkurven von Lötstellen Randbedingungen am oberen Ende von Lötstellen äquivalent zu Anfangsbedingungen machen, basierend auf der effektiven Methode der Lösung des Anfangswerts. Da die Lösung für den Anfangswert die Anforderung, dass z gleich 0 ist, nicht erfüllen kann, wird sie in ein äquivalentes Problem in Bezug auf die Zielfunktionsminimierung umgewandelt, die in Gleichung (3) angezeigt wird.

Diese minimierte Zielfunktion kann angewendet werden, um die ideale Entwurfsgröße des Pads Dx4 zu bestimmen .

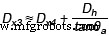

Darüber hinaus müssen geometrische Merkmale des Zinnwickelwinkels des PCB-Pads berücksichtigt werden. In diesem Licht sollte die Ausdehnungsgröße des Pads der ungefähren Gleichung unten entsprechen:

In dieser Gleichung Dh bezieht sich auf die Dicke des freigelegten Seitenpolsters außerhalb des Chips. Durch die Optimierung impliziter Variablen wird die erwartete Fehleranforderung durch die Zielfunktion und die Designgröße der Pads innen und außen (Dx4) erfüllt &Dx3 ) berechnet werden, wobei der Seitenwert am unteren Ende erfüllt werden muss.

Dieses Verfahren stellt sicher, dass ein für QFN geeignetes Pad gut entworfen werden kann, um die hohe elektrische Leistung sowohl dieses Bauteils als auch der Leiterplatte zu erreichen. Dann ist PCBCart mit professioneller und qualifizierter Montagefähigkeit in der Lage, Ihr ideales Design in die Realität umzusetzen.

Hilfreiche Ressourcen

• Einführung in die Via-in-Pad (VIP)-Technologie

• Designanforderungen für SMT-Leiterplatten, Teil 1:Bondpad-Design einiger gewöhnlicher Komponenten

• Designanforderungen für SMT-Leiterplatten, Teil 2:Einstellungen für Pad-Trace-Verbindung, Durchgangslöcher, Testpunkt, Lötmaske und Siebdruck

• Schablonendesign-Anforderung an QFN-Komponenten für optimale Leistung von PCBA

• Vollfunktions-PCB-Fertigungsservice von PCBCart - Mehrfachnutzen- zusätzliche Optionen

• Erweiterter PCB-Bestückungsservice von PCBCart – ab 1 Stück

Industrietechnik

- PCB-Layout-Software

- PCB-Materialien und Design für Hochspannung

- Leiterplattenfertigung für 5G

- Wichtige Überlegungen zur Leiterplattenbestückung

- Notfallverfahren für führende PCB-Defekte

- Überlegungen zum Impedanzdesign für starrflexible PCB

- PCB-Design für Hochfrequenzschaltung und elektromagnetische Kompatibilität

- PCB-Designanforderung für Smartphones

- Ersterfolg im PCB-EMV-Design sichern

- Drei Designüberlegungen zur Sicherstellung der EMV von Laptop-PCB