Embedded Design mit FPGAs:Hardwareressourcen

Anmerkung des Herausgebers:Da immer fortschrittlichere Algorithmen für intelligente Produktdesigns entstehen, haben Entwickler oft Schwierigkeiten, eingebettete Systeme zu implementieren, die die entsprechenden Verarbeitungsanforderungen dieser Algorithmen erfüllen. FPGAs können die erforderliche Leistung liefern, aber das Entwerfen mit FPGAs galt lange Zeit als auf FPGA-Programmierexperten beschränkt. Heute jedoch hat die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Entwicklungsumgebungen die FPGA-Entwicklung allgemein zugänglich gemacht. In diesem Auszug, Kapitel 4 aus dem Buch Architecting High-Performance Embedded Systems, bietet der Autor einen umfassenden Überblick über FPGA-Geräte, Implementierungssprachen und den FPGA-Entwicklungsprozess sowie eine detaillierte Anleitung, wie Sie mit der Implementierung eigener FPGAs beginnen können Entwurf. Der vollständige Auszug wird in der folgenden Reihe von Raten präsentiert:

Anmerkung des Herausgebers:Da immer fortschrittlichere Algorithmen für intelligente Produktdesigns entstehen, haben Entwickler oft Schwierigkeiten, eingebettete Systeme zu implementieren, die die entsprechenden Verarbeitungsanforderungen dieser Algorithmen erfüllen. FPGAs können die erforderliche Leistung liefern, aber das Entwerfen mit FPGAs galt lange Zeit als auf FPGA-Programmierexperten beschränkt. Heute jedoch hat die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Entwicklungsumgebungen die FPGA-Entwicklung allgemein zugänglich gemacht. In diesem Auszug, Kapitel 4 aus dem Buch Architecting High-Performance Embedded Systems, bietet der Autor einen umfassenden Überblick über FPGA-Geräte, Implementierungssprachen und den FPGA-Entwicklungsprozess sowie eine detaillierte Anleitung, wie Sie mit der Implementierung eigener FPGAs beginnen können Entwurf. Der vollständige Auszug wird in der folgenden Reihe von Raten präsentiert:

1:Hardwareressourcen (dieser Artikel)

2:Implementierungssprachen

3:Entwicklungsprozess

4:Ein Projekt erstellen

5:Implementierung

Adaptiert aus Architecting High-Performance Embedded Systems, von Jim Ledin.

Entwicklung Ihres ersten FPGA-Programms

Dieses Kapitel beginnt mit einer Diskussion über den effektiven Einsatz von FPGA-Bauelementen in eingebetteten Echtzeitsystemen und wird mit einer Beschreibung der in Standard-FPGAs enthaltenen Funktionselemente fortgesetzt. Die Palette der FPGA-Designsprachen, einschließlich Hardware Beschreibungssprachen (HDLs ), Blockdiagrammmethoden und gängige Softwareprogrammiersprachen, einschließlich C und C++, wird vorgestellt. Das Kapitel fährt mit einem Überblick über den FPGA-Entwicklungsprozess fort und endet mit einem vollständigen Beispiel eines FPGA-Entwicklungszyklus, beginnend mit einer Aufstellung der Systemanforderungen und endend mit einem funktionalen System, das in einem kostengünstigen FPGA-Entwicklungsboard implementiert ist.

Nach Abschluss dieses Kapitels wissen Sie, wie FPGAs in Echtzeit-Embedded-Systemarchitekturen eingesetzt werden können, und kennen die Komponenten, aus denen eine integrierte FPGA-Schaltung besteht. Sie haben die Programmiersprachen kennengelernt, die beim Design von FPGA-Algorithmen verwendet werden, und verstehen die Abfolge der Schritte zur Entwicklung einer FPGA-basierten Anwendung. Sie haben auch ein vollständiges FPGA-Entwicklungsbeispiel auf einem kostengünstigen Entwicklungsboard mit kostenlosen FPGA-Softwaretools durchgearbeitet.

In diesem Kapitel werden wir die folgenden Themen behandeln:

- Einsatz von FPGAs in Echtzeit-Embedded-System-Designs

- FPGA-Implementierungssprachen

- Der FPGA-Entwicklungsprozess

- Entwicklung Ihres ersten FPGA-Projekts

Technische Anforderungen

Die Dateien für dieses Kapitel sind verfügbar unter https://github.com/PacktPublishing/Architecting-High-Performance-Embedded-Systems.

Einsatz von FPGAs in Echtzeit-Embedded-System-Designs

Wie wir in den Elementen von FPGAs gesehen haben Abschnitt von Kapitel 1 , Hochleistungsarchitektur Eingebettete Systeme , enthält ein typisches FPGA-Gerät eine große Anzahl von Lookup-Tabellen, Flip-Flops, Block-RAM-Elementen, DSP-Slices und anderen Komponenten. Obwohl es aufschlussreich sein kann, die detaillierten Fähigkeiten jeder dieser Komponenten zu verstehen, sind solche Bedenken während des FPGA-Entwicklungsprozesses nicht unbedingt aufschlussreich. Die wichtigste Einschränkung ist, dass eine bestimmte FPGA-Teilenummer eine endliche Anzahl von jedem dieser Elemente enthält und ein Design diese Grenzen nicht überschreiten kann, wenn es auf dieses bestimmte FPGA-Modell ausgerichtet ist.

Produktiver ist es stattdessen, den FPGA-Entwicklungsprozess aus der Perspektive der Anforderungserklärung des eingebetteten Systems zu betrachten. Sie können mit der Entwicklung des FPGA-Designs beginnen, das auf ein etwas willkürlich gewähltes FPGA-Modell ausgerichtet ist. Im Laufe der Entwicklung erreichen Sie möglicherweise eine Ressourcengrenze oder identifizieren eine FPGA-Funktion, die das Design erfordert und die im derzeit angestrebten FPGA nicht vorhanden ist. An diesem Punkt können Sie ein anderes, leistungsfähigeres Ziel auswählen und die Entwicklung fortsetzen.

Wenn sich die Entwicklung des Designs dem Abschluss nähert, stellen Sie möglicherweise fest, dass das ursprünglich ausgewählte Ziel-FPGA übermäßige Ressourcen enthält und das Design durch die Auswahl eines kleineren FPGA verbessert werden könnte, mit potenziellen Vorteilen in Bezug auf niedrigere Kosten, weniger Pins, kleinere Gehäusegröße, und reduzierter Stromverbrauch.

In jeder dieser Situationen ist es im Allgemeinen einfach, das Ziel-FPGA auf ein anderes Modell innerhalb derselben Familie umzustellen. Die bisher erstellten Entwicklungstools und Designartefakte sollten mit dem neu ausgerichteten FPGA-Modell vollständig wiederverwendbar sein. Wenn es notwendig wird, auf eine andere FPGA-Familie desselben Anbieters oder auf ein Modell eines anderen Anbieters umzusteigen, ist der Wechsel wahrscheinlich mit mehr Aufwand verbunden.

Der Sinn dieser Diskussion besteht darin, zu betonen, dass es nicht allzu wichtig ist, zu Beginn einer Entwicklung von Hochleistungs-Embedded-Systemen ein spezifisches FPGA-Modell zu identifizieren. Stattdessen sollten sich frühe Überlegungen darauf konzentrieren, die Entscheidung, ein FPGA als Teil des Designs zu verwenden, zu validieren, und dann, wenn das FPGA der beste Designansatz ist, mit der Auswahl eines geeigneten FPGA-Anbieters und einer geeigneten Gerätefamilie fortfahren.

Beispielprojekte in diesem Buch basieren auf der Xilinx Vivado-Familie von FPGA-Entwicklungstools. Obwohl für einige Xilinx-FPGA-Familien eine Vivado-Lizenz erworben werden muss, werden die FPGA-Geräte in Artix-7, mit denen wir arbeiten werden, von Vivado kostenlos unterstützt. Die Artix-7 FPGA-Familie kombiniert die Attribute hoher Leistung, niedrigem Stromverbrauch und reduzierten Gesamtsystemkosten. Ähnliche FPGA-Gerätefamilien und Entwicklungstool-Suiten sind von anderen FPGA-Anbietern erhältlich.

Die FPGA-Entwicklung ist ein ziemlich aufwendiger Prozess, bei dem eine Vielzahl von Analyse- und Designdateneingaben erforderlich sind. Um diese Themen nicht zu abstrakt zu diskutieren und konkrete Ergebnisse in Form von Beispielprojekten zu präsentieren, verwenden wir im gesamten Buch Vivado. Sobald Sie mit den hier besprochenen Tools und Techniken vertraut sind, sollten Sie sie mit ähnlichen Tools anderer Anbieter anwenden können.

In den folgenden Abschnitten werden einige wichtige Unterscheidungsmerkmale der FPGA-Familien und einzelner Modelle innerhalb dieser Familien erörtert, darunter die Menge des Block-RAM, die Menge und die Arten der verfügbaren E/A-Signale, spezialisierte On-Chip-Hardwareressourcen und die Einbeziehung von ein oder mehrere Hardware-Prozessorkerne im FPGA-Paket.

Block RAM und verteilten RAM

RAM blockieren wird verwendet, um Speicherbereiche in einem FPGA zu implementieren. Ein bestimmter Speicherbereich wird in Form der Breite in Bit (typischerweise 8 oder 16 Bit) und der Tiefe angegeben, die die Anzahl der Speicherorte im Speicherbereich definiert.

Die Gesamtmenge an Block-RAM in einem FPGA wird normalerweise in Kilobit angegeben (KB ). Die Menge des verfügbaren Block-RAM variiert zwischen den FPGA-Familien und zwischen den Modellen innerhalb einer bestimmten Familie. Erwartungsgemäß verfügen größere und teurere Teile im Allgemeinen über eine größere Menge an Ressourcen, die als Block-RAM verwendet werden können.

In Xilinx-FPGAs und in unterschiedlichem Maße in FPGAs anderer Anbieter ist zusätzlich zum Block-RAM eine eigene Speicherkategorie namens Distributed RAM verfügbar. Verteilter RAM ist aus den Logikelementen aufgebaut, die in Nachschlagetabellen verwendet werden, und verwendet die Schaltung dieser Geräte um, um winzige RAM-Segmente zu bilden, die jeweils 16 Bit enthalten. Diese Segmente können bei Bedarf zu größeren Speicherblöcken zusammengefasst werden.

Block-RAM wird tendenziell für Zwecke verwendet, die traditionell mit RAM verbunden sind, wie zum Beispiel die Implementierung von Prozessor-Cache-Speicher oder als Speicherpuffer für E/A-Daten. Verteilter RAM kann für Zwecke wie die temporäre Speicherung von Zwischenberechnungsergebnissen verwendet werden. Da verteilter RAM auf einer Nachschlagetabellen-Schaltung basiert, reduziert die Verwendung von verteiltem RAM in einem Design die verfügbaren Ressourcen zum Implementieren von Logikoperationen.

Block-RAM kann einen einzelnen Port oder zwei Ports haben. Single-Port-Block-RAM repräsentiert das allgemeine Nutzungsmuster eines Prozessors, der RAM während des Betriebs liest und schreibt.

Dual-Port-Block-RAM bietet zwei Lese-/Schreib-Ports, die beide gleichzeitig aktiv im gleichen Speicherbereich lesen oder schreiben können.

Dual-Port-Block-RAM ist ideal für Situationen, in denen Daten zwischen Teilen eines FPGAs mit unterschiedlichen Taktraten übertragen werden. Beispielsweise kann ein E/A-Subsystem eine Taktfrequenz von mehreren Hundert MHz haben, wenn es einen eingehenden Datenstrom empfängt. Das E/A-Subsystem schreibt eingehende Daten in den Block-RAM, wenn sie über einen der Hochgeschwindigkeits-E/A-Kanäle des FPGAs eintreffen. Ein separates Subsystem innerhalb des FPGA, das mit einer anderen Taktgeschwindigkeit läuft, kann Daten vom zweiten Port des Block-RAM lesen, ohne den Betrieb des I/O-Subsystems zu stören.

Block-RAM kann auch im First-in-First-out-Verfahren betrieben werden (FIFO ) Modus. Im Beispiel des ankommenden seriellen Datenstroms kann das I/O-Subsystem Datenwörter in den FIFO einfügen, wenn sie ankommen, und das verarbeitende Subsystem kann sie in derselben Reihenfolge auslesen. Block-RAM im FIFO-Modus liefert Signale, die anzeigen, ob der FIFO voll, leer, fast voll oder fast leer ist. Die Definitionen von fast vollständig und fast leer sind Sache des Systemdesigners. Wenn Sie fast leer zuweisen bedeutet, dass weniger als 16 Elemente im FIFO verbleiben, können Sie sicher sein, dass Sie immer dann, wenn das FIFO nicht anzeigt, dass es fast leer ist, 16 Elemente ohne weitere Prüfung der Datenverfügbarkeit lesen können.

Wenn Block-RAM im FIFO-Modus verwendet wird, ist es wichtig, dass die Logik, die Elemente in den FIFO einfügt, niemals versucht, zu schreiben, wenn der FIFO voll ist, und dass die Logik, die aus dem FIFO liest, nie versucht, zu lesen, wenn der FIFO leer ist. Wenn eines dieser Ereignisse eintritt, verliert das System entweder Daten oder versucht, undefinierte Daten zu verarbeiten.

FPGA-E/A-Pins und zugehörige Funktionen

Da FPGAs für den Einsatz in Hochleistungsanwendungen gedacht sind, sind ihre I/O-Pins im Allgemeinen in der Lage, eine Vielzahl von Hochgeschwindigkeits-I/O-Standards zu implementieren. Während der Implementierung eines Designs mit einer FPGA-Entwicklungstoolsuite muss der Systementwickler Aufgaben ausführen, die das Zuweisen von Funktionen zu bestimmten Pins auf dem FPGA-Paket und die Konfiguration jedes dieser Pins für den Betrieb mit dem entsprechenden Schnittstellenstandard umfassen. Es müssen zusätzliche Schritte durchgeführt werden, um Eingangs- und Ausgangssignale innerhalb des FPGA-Modellcodes den richtigen Gehäusepins zuzuordnen.

Auf Pin-Ebene sind einzelne I/O-Signale entweder Single-Ended oder Differential.

Ein Single-Ended-Signal ist auf Masse bezogen. Traditionelle Transistor-Transistor-Logik (TTL ) und Komplementärer Metalloxid-Halbleiter (CMOS ) digitale Signale arbeiten über einen Bereich von 0-5 VDC relativ zur Erde.

Moderne FPGAs unterstützen in der Regel nicht den Legacy-Signalbereich von 5 VDC, sondern unterstützen stattdessen TTL- und CMOS-Signale, die über einen reduzierten Spannungsbereich betrieben werden, wodurch der Stromverbrauch reduziert und die Geschwindigkeit verbessert wird. Niederspannungs-TTL (LVTTL ) Signale arbeiten über einen Bereich von 0-3,3 VDC. Niederspannungs-CMOS (LVCMOS )-Signale sind mit Signalisierungsspannungen von 1,2, 1,5, 1,8, 2,5 und 3,3 V wählbar. Diese Signaltypen heißen LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25 und LVCMOS33. Andere hochleistungsfähige Single-Ended-Signaltypen sind verfügbar, einschließlich Hochgeschwindigkeits-Transceiver-Logik (HSTL ) und Terminated Logic der Stub-Serie (SSTL ).

Single-Ended-Signale werden häufig für Niederfrequenzzwecke verwendet, z. B. zum Lesen von Tastereingängen und zum Leuchten von LEDs. Single-Ended-Signale werden auch in vielen Kommunikationsprotokollen mit niedrigerer Geschwindigkeit wie I2C und SPI verwendet. Ein wichtiger Nachteil von Single-Ended-Signalen besteht darin, dass jedes Rauschen, das in die das Signal tragenden Drähte und Leiterbahnen der gedruckten Schaltung eingekoppelt wird, das Potenzial hat, den Eingang zum Empfänger zu verfälschen. Dieses Problem kann durch die Verwendung von Differenzsignalen erheblich reduziert werden.

Für die höchsten Datenübertragungsraten ist die differentielle Signalisierung der bevorzugte Ansatz.

Differentialsignale Verwenden Sie ein Paar I/O-Pins und treiben Sie entgegengesetzte Signale auf die beiden Pins.

Mit anderen Worten, ein Pin wird auf eine höhere Spannung und der andere Pin auf eine niedrigere Spannung angesteuert, um ein 0-Datenbit darzustellen, und die Pinspannungen werden umgekehrt, um ein 1-Bit darzustellen. Der Differenzempfänger subtrahiert die beiden Signale, um zu bestimmen, ob das Datenbit 0 oder 1 ist. Da die beiden Drähte oder Spuren, die das Differenzsignal tragen, physisch sehr nahe beieinander liegen, wird jedes Rauschen, das in eines der Signale einkoppelt, mit dem anderen gekoppelt auf ganz ähnliche Weise. Die Subtraktionsoperation entfernt den Großteil des Rauschens und ermöglicht einen zuverlässigen Betrieb bei viel höheren Datenübertragungsraten als bei Single-Ended-Signalen.

Eine Reihe von differentiellen Signalstandards werden von Standard-FPGAs unterstützt. Es sind mehrere differentielle Versionen von HSTL und SSTL mit unterschiedlichen Signalspannungspegeln für jede definiert.

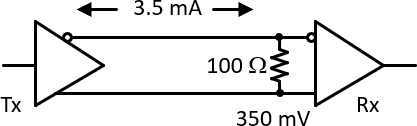

Niederspannungs-Differentialsignalisierung (LVDS ) wurde 1994 als Standard eingeführt und wird weiterhin in einer Vielzahl von Anwendungen verwendet. Ein LVDS-Signalsender erzeugt einen konstanten Strom von 3,5 mA und ändert die Richtung des Stroms, der durch den Widerstand am Empfänger fließt, um Zustandsänderungen zu erzeugen, die 0- und 1-Datenwerte darstellen, wie in Abbildung 4.1 . gezeigt :

Abbildung 4.1 – LVDS-Schnittstelle

Bei der LVDS-Kommunikation ist es wie bei den anderen differentiellen und single-ended Signalisierungsstandards wichtig, dass die Impedanz des Kommunikationspfads zwischen Sender und Empfänger genau der Abschlussimpedanz entspricht, die im Fall von LVDS 100 Ohm beträgt. Wenn die Impedanz des Kommunikationskanals nicht mit der Abschlussimpedanz übereinstimmt, können Reflexionen auf der Leitung auftreten, die einen zuverlässigen Datenempfang verhindern.

Die Impedanz von differentiellen Signalspurpaaren ist eine Funktion der Geometrie der Paarspuren und ihrer Beziehung zur Masseebene. Wie wir in Kapitel 6 sehen werden , Schalten mit KiCad entwerfen , ist es einfach, Leiterplatten zu entwerfen, die die Anforderungen von Hochgeschwindigkeits-Differentialsignalisierungsstandards erfüllen.

Spezialisierte Hardwareressourcen

FPGAs enthalten im Allgemeinen eine Auswahl dedizierter Hardwareressourcen für Funktionen, die häufig benötigt werden und entweder effizienter in Hardware implementiert werden als synthetisierte FPGA-Funktionen zu verwenden, oder mit FPGA-Komponenten nicht zu implementieren sind. Einige Beispiele für diese Ressourcen sind wie folgt:

- Schnittstellen zu externem dynamischem RAM (DRAM ) zum Speichern großer Mengen dieser Schnittstellen unterstützen im Allgemeinen einen gängigen DRAM-Standard wie DDR3.

- Analog-Digital-Wandler.

- Phasenregelkreise, die zum Erzeugen mehrerer Taktfrequenzen verwendet werden.

- Digitale Signalverarbeitung multiplizieren-akkumulieren (MAC ) Hardware.

Diese Hardwareressourcen ermöglichen die Entwicklung komplexer Systeme mit weitreichenden Fähigkeiten. Für Funktionen wie den MAC-Betrieb wird dedizierte Hardware bereitgestellt, da die Hardwareleistung deutlich besser ist als die synthetisierte äquivalente Funktionalität mit FPGA-Logikressourcen.

Prozessorkerne

Einige FPGA-Familien enthalten Hardware-Prozessorkerne, um die höchste Software-Ausführungsgeschwindigkeit mit den Leistungsvorteilen von FPGA-implementierten Algorithmen zu kombinieren. Die Zynq-7000-Familie von Xilinx integriert beispielsweise einen Hardware-ARM-Cortex-A9-Prozessor zusammen mit einem traditionellen FPGA-Fabric.

FPGA-Designs, die keinen Hardwareprozessor erfordern, können einen Prozessor implementieren, der die FPGA-Ressourcen verwendet, die als Softprozessor bezeichnet werden . Softprozessoren sind hochgradig konfigurierbar, obwohl sie im Allgemeinen nicht in der Lage sind, die Leistung eines in Hardware implementierten Prozessors zu erreichen.

Im nächsten Abschnitt werden die wichtigsten Programmiersprachen und Dateneingabemethoden vorgestellt, die zur Entwicklung von FPGA-Algorithmen verwendet werden.

Nachdruck mit Genehmigung von Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin ist CEO von Ledin Engineering, Inc. Jim ist ein Experte für Design, Entwicklung und Test von eingebetteter Software und Hardware. Er ist auch in der Cybersicherheitsbewertung von eingebetteten Systemen und in Penetrationstests versiert. Er hat einen B. S. Abschluss in Luft- und Raumfahrttechnik von der Iowa State University und einen M.S. Abschluss in Elektro- und Computertechnik vom Georgia Institute of Technology. Jim ist ein registrierter professioneller Elektroingenieur in Kalifornien, ein Certified Information System Security Professional (CISSP), ein Certified Ethical Hacker (CEH) und ein Certified Penetration Tester (CPT).

Jim Ledin ist CEO von Ledin Engineering, Inc. Jim ist ein Experte für Design, Entwicklung und Test von eingebetteter Software und Hardware. Er ist auch in der Cybersicherheitsbewertung von eingebetteten Systemen und in Penetrationstests versiert. Er hat einen B. S. Abschluss in Luft- und Raumfahrttechnik von der Iowa State University und einen M.S. Abschluss in Elektro- und Computertechnik vom Georgia Institute of Technology. Jim ist ein registrierter professioneller Elektroingenieur in Kalifornien, ein Certified Information System Security Professional (CISSP), ein Certified Ethical Hacker (CEH) und ein Certified Penetration Tester (CPT). Verwandte Inhalte:

- Open-Source-Tools vereinfachen die FPGA-Programmierung

- Implementierung von Gleitkomma-Algorithmen in FPGAs oder ASICs

- Einsatz von FPGAs für Deep Learning

- Softwaretools migrieren GPU-Code auf FPGAs für KI-Anwendungen

- FPGAs ersetzen ASICs in bildbasierten ADAS von Subaru Eyesight

- Wie Flash-basierte FPGAs die Anforderungen an die funktionale Sicherheit vereinfachen

- Die Vorteile von Instant-on-FPGAs nutzen

- FPGA-Konfiguration mit Hochgeschwindigkeits-NOR-Flash

- Wie sich die FPGA-Technologie weiterentwickelt, um neue Systemanforderungen der mittleren Preisklasse zu erfüllen

Für mehr Embedded, abonnieren Sie den wöchentlichen E-Mail-Newsletter von Embedded.

Eingebettet

- So vermeiden Sie kostspielige Überraschungen beim Design von vernetzter Hardware

- Was ist Embedded System Design:Schritte im Designprozess

- Vereinfachung der IoT-Entwicklung mit Eclipse IoT

- Entwicklung von Zustandsautomaten mit testgetriebener Entwicklung

- Umwandeln von Big Data in Smart Data mit eingebetteter KI

- Cypress:ModusToolbox Suite erleichtert die Komplexität des IoT-Designs

- Gitter:MachX03D FPGA verbessert die Sicherheit mit Hardware-Root-of-Trust-Funktionen

- Design-Kit misst den Blutdruck mit optischem Sensor

- Java 9 – Verbesserung „Try With Resources“.

- Alles drin mit Additiv