Die Optimierung des Spacer-Engineerings für einen kondensatorlosen DRAM basierend auf dem Dual-Gate-Tunneling-Transistor

Zusammenfassung

Der auf dem Dual-Gate-Tunnel-FET (DGTFET) basierende DRAM hat die Vorteile einer kondensatorlosen Struktur und einer hohen Haltezeit. In diesem Artikel wird die Optimierung der Spacer-Technik für DGTFET-DRAM systematisch mit dem Silvaco-Atlas-Tool untersucht, um seine Leistung weiter zu verbessern, einschließlich der Reduzierung des Lesestroms „0“ und der Verlängerung der Retentionszeit. Die Simulationsergebnisse zeigen, dass Abstandshalter an der Source- und Drain-Seite die Low-k- bzw. High-k-Dielektrika verwenden sollten, die den Lesestrom „1“ verbessern und den Lesestrom „0“ reduzieren können. Durch die Anwendung dieser optimierten Spacer-Technik erreicht der DGTFET-DRAM die optimale Leistung – einen extrem niedrigen Lesestrom von „0“ (10 −14 A/μm) und eine lange Retentionszeit (10s), was den statischen Stromverbrauch und die dynamische Bildwiederholfrequenz verringert. Und der niedrige Strom „0“ verbessert auch sein Stromverhältnis (10 7 ) von „1“ zu „0“ lesen. Darüber hinaus offenbart die Analyse zur Skalierbarkeit deren inhärente Schwäche, die die weitere Untersuchungsrichtung für DGTFET-DRAM bietet.

Hintergrund

Mit der Schrumpfung der Gerätegeometrie hat der dynamische Direktzugriffsspeicher (DRAM) mit 1 Transistor (1T) – 1 Kondensator (1C) Schwierigkeiten beim Herunterskalieren, da es für den Kondensator schwierig ist, seine Größe zu reduzieren [1,2,3] . Die Speicherindustrie hat einige effektive Methoden für das Packen von Speicher mit höherer Dichte vorgeschlagen, wie zum Beispiel neue Materialien und neuartige Bauelementstrukturen [4, 5]. Der 1T DRAM mit der kondensatorlosen Struktur wurde erstmals in den frühen 90er Jahren beschrieben [6, 7] und erregt immer mehr Aufmerksamkeit. In 1T DRAM wird der Zustand 1 (Trägerspeicher) auf vier Wegen erreicht:Stoßionisation [8], Bipolartransistor [9], Band-zu-Band-Tunneln (BTBT) [10] und Gate-Tunneln [11].

Der Tunnel-Feldeffekttransistor (TFET) auf Basis des BTBT wurde aufgrund des höheren Schaltverhältnisses und des extrem niedrigen Sperrstroms als potentielle Alternative für MOSFETs angesehen [12,13,14]. Die Vorteile von TFET – geringer Sperrstrom und schwache Temperaturabhängigkeit – sind für DRAM außerordentlich vorteilhaft. Insbesondere kann der niedrige Sperrstrom den Lesestrom „0“ und den statischen Stromverbrauch reduzieren. Gegenwärtig arbeiten einige Gruppen an der Untersuchung von TFET-DRAM [15,16,17,18,19,20]. Es wird berichtet, dass TFET-DRAM den niedrigen Lesestrom „0“ und eine hohe Retentionszeit (RT) aufweist. Unter diesen TFET-DRAMs ist der Dual-Gate-TFET-(DGTFET)-DRAM am bekanntesten [19, 20]. Beim DGTFET DRAM basieren sowohl die Schreib- als auch die Leseoperationen auf dem BTBT. Untersuchungen haben gezeigt, dass der Lesestrom von „0“ von DGTFET-DRAM bis zu 1 nA/μm erreichen kann, was viel weniger ist als der von herkömmlichen 1T1C-DRAM. Und die RT von 2 s ist dem Zielwert von 64 ms weit überlegen, der im Computersystem normalerweise auf die dynamische Aktualisierungszeit eingestellt wird [21]. Die RT des DGTFET DRAM ist immer noch größer als 300 ms, wenn die Temperatur auf 85 °C erhöht wird, was seine Praktikabilität unter rauen Bedingungen ermöglicht. Darüber hinaus zeigt beim DGTFET-DRAM die Eliminierung eines Kondensators mit größerer Größe auch seine Wettbewerbsfähigkeit bei der Packung mit hoher Dichte. Diese Vorteile zeigen vollständig, dass es notwendig ist, DGTFET-DRAM zu studieren. Obwohl diese Untersuchungen gezeigt haben, dass DGTFET eine überlegene Leistung als herkömmlicher 1T1C-DRAM aufweist, sind die Ergebnisse (RT und Lesen des Stroms „0“) nicht optimal, da die Gerätekonfiguration des DGTFET nicht optimiert ist.

In diesem Artikel wird die Spacer-Technik von DGTFET optimiert, damit DGTFET die optimale Leistung erhält. Bei TFETs haben die Spacer-Dielektrika den starken Einfluss auf BTBT [22, 23]. Beim DGTFET sind die Spacer an der Source- und Drain-Seite gegenüber Tunnelübergängen geschlossen, sodass sie die Leistung des DGTFET-DRAM stark beeinflussen. Dieses Papier analysiert systematisch die Einflüsse des Spacer-Dielektrikums (Low-k- oder High-k-Dielektrika) in jedem Spacer auf DGTFET-DRAM und schlägt eine optimierte Spacer-Technik vor. Durch die Optimierung des Spacer-Engineerings wird der Lesestrom „0“ auf 10 –14 . gesenkt A/μm und RT können bis zu 10 s betragen. Schließlich wird in dieser Arbeit auch die Skalierbarkeit von DGTFET DRAM mit der optimierten Spacer-Technik diskutiert.

Gerätestruktur und Simulationsverfahren

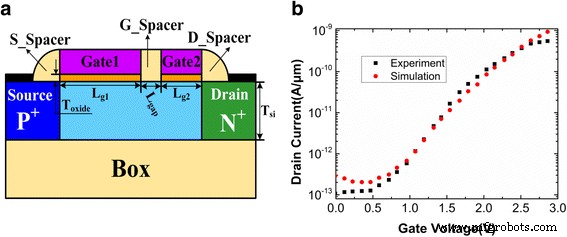

Der DGTFET mit einer P-I-N-Konfiguration ist in Fig. 1a veranschaulicht. Die Source- und Drain-Regionen sind P + Doping (10 20 /cm 3 ) und N + Doping (10 20 /cm 3 ), bzw. Die intrinsische Kanalregion ist in zwei Teile unterteilt:Gate1-Region mit dem N + Polysilizium und Gate2-Region mit dem P + Polysilizium. Es gibt eine kurze Lücke zwischen Gate1 und Gate2. Das P + Polysilizium-Gate2 kann die physikalische Quelle für die Ladungsspeicherung erstellen und beibehalten und den herkömmlichen TFET-basierten DRAM ersetzen, der ein P + . verwendet Taschenbereich als Speicherbereich. Während für ein N + Polysilizium Gate1 ist die Lochkonzentration im Unterlappungsbereich zwischen Gate1 und Gate2 gering, was für den Lesevorgang hilfreich ist. Also ein P + Polysilizium-Gate2 ist dafür ausgelegt, einen tieferen Speicherbereich zu schaffen, der eine längere Aufbewahrungszeit ermöglichen könnte, während ein N + Polysilizium-Gate1 wird ausgewählt, um den Tunnelmechanismus während des Lesevorgangs zu steuern [20]. In 1a beziehen sich S_Spacer und D_Spacer auf die Spacer an der Source- bzw. Drainseite. Der G_spacer bezieht sich auf den Abstandshalter zwischen Gate1 und Gate2. Das Standardmaterial der Abstandshalter ist SiO2 . Die Standardgeräteparameter sind wie folgt:Dicke des Siliziumfilms (Tsi ) ist 20 nm, Länge des Gate1 (Lg1 .) ) beträgt 400 nm, Länge des Gate2 (Lg2 .) ) beträgt 200 nm, Länge der Gatelücke (Lgap ) beträgt 50 nm und die Dicke des Gate-Oxids HfO2 (TOxid ) beträgt 3 nm.

a Schema einer Dual-Gate-TFET (DGTFET) DRAM-Zelle. b Vergleich zwischen simulierter Übertragungscharakteristik mit experimentellen Ergebnissen für SOI-TFET [25]

Die Simulationen des DGTFET DRAM werden in Silvaco Atlas mit einem nicht-lokalen BTBT-Modell durchgeführt. Das nichtlokale BTBT-Tunnelmodell berücksichtigt die räumliche Variation der Energiebänder und die Erzeugung/Rekombination des entgegengesetzten Trägertyps [24]. Die Parameter des Tunnelmodells werden gemäß den experimentellen Ergebnissen von SOI TFET [25] kalibriert. Die Masse des Elektronen- und Lochtunnels wird auf 0,22 m0 . eingestellt und 0,52 m0 , wobei m0 ist die Ruhemasse des Elektrons. Die simulierte Übertragungscharakteristik von SOI-TFET stimmt mit experimentellen Ergebnissen überein, wie in Abb. 1b gezeigt, die die in dieser Arbeit verwendeten Modelle autorisiert. Aufgrund der starken Dotierung in Source- und Drain-Gebieten werden auch das Bandgap-Verengungsmodell und die Fermi-Dirac-Statistik berücksichtigt. Darüber hinaus werden auch die Shockley-Read-Hall-Rekombination sowie Dotierungs- und elektrische feldabhängige Mobilitätsmodelle angewendet. Alle Modellparameter stimmen mit denen in [19, 20] überein. Da die Trägerlebensdauer die Trägererzeugung/-rekombination während des Haltebetriebs bestimmt, beeinflusst sie die RT des DGTFTET DRAM. Entsprechend der unterschiedlichen Ladungsträgerlebensdauern zwischen 1 μs und 10 ns in [26,27,28] werden die Elektronen- und Lochlebensdauern auf 100 ns festgelegt. Scharfetter-Relation und Schenk-Modelle werden verwendet, um die Dotierung bzw. die Temperaturabhängigkeit der Lebensdauer zu berücksichtigen.

Ergebnisse und Diskussion

Bedienmechanismus

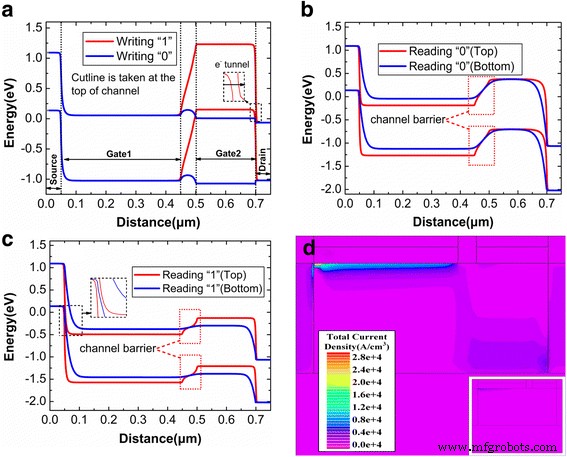

Beim DGTFET-DRAM werden die Schreib- und Lesevorgänge durch BTBT an den Drain- bzw. Source-Tunnelübergängen gesteuert. Abbildung 2 zeigt die Energiebänder während der verschiedenen Operationen. Wie in Abb. 2a gezeigt, baut das Gate2 mit negativer Vorspannung während des Schreibens von „1“ das Energieband des Kanals unter Gate2 erheblich auf, so dass eine extrem kleine Tunnelbarriere auf der Drain-Seite erzeugt wird. Somit tunneln die Elektronen zur Drainseite und die Löcher sammeln sich in der tiefen Potentialmulde (1,2 V) an, wie in Abb. 3a gezeigt. Während des Schreibens von „0“ bewirkt das Gate2 mit positiver Vorspannung, dass sich die Löcher aus diesem Potentialtopf ausstoßen und an der Drain-Seite rekombinieren [29]. Abbildung 2b, c zeigt die Energiebänder nach dem Lesen von „1“ bzw. „0“. Abbildung 2b zeigt, dass zwischen Gate1 und Gate2 eine Kanalbarriere vorhanden ist, die jedoch am unteren Ende des Kanals nicht vorhanden ist. Außerdem ist der Tunnelabstand auf der Quellenseite am oberen Ende des Kanals kleiner. Dies zeigt, dass sich beim Lesen von „1“ ein geneigter Leitungspfad (von der vorderen Schnittstelle für Gate1 zur hinteren Schnittstelle für Gate2) ausbildet, was auch durch die Stromdichte von Abb. 2d demonstriert werden kann. Beim Lesen von „0“ ist in Abb. 2c die offensichtliche Kanalbarriere zu finden, die den lesenden „0“-Strom hemmt. Der Einschub von Abb. 2d zeigt, dass Elektronen, die aus dem Sourcebereich tunneln, diese Kanalbarriere nicht überwinden können, um den höheren Messwert „0“ zu bilden.

Energiebänder von der Quelle bis zur Senke. a Energiebänder nach dem Schreiben von „1“ mit negativem Gate2-Bias und nach dem Schreiben von „0“ mit positivem Gate2-Bias. b Energiebänder am oberen und unteren Rand des Kanals nach dem Lesen von „1“. c Energiebänder am oberen und unteren Rand des Kanals nach dem Lesen von „0“. d Gesamtstromdichte nach dem Lesen von „1“

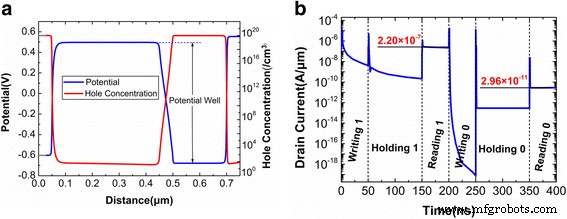

a Potential- und Lochkonzentration auf der Oberfläche des Kanals nach dem Schreiben von „1“. b Transiente Reaktion des Drainstroms für DGTFET DRAM betrieben in Tabelle 1

Eine richtige Programmierbedingung ist für DGTFET DRAM wichtig. An Gate2 sollte eine größere negative Vorspannung angelegt werden, damit der gesättigte BTBT beim Schreiben von „1“ induziert wird. Während des Haltens von „1“ wird an Gate2 eine kleine negative Vorspannung angelegt, um Löcher im Potenzialtopf für lange Zeit zu halten. Bei Lesevorgängen verstärkt die höhere Gate1-Vorspannung den BTBT während des Lesens von „1“, was jedoch für das Lesen des Stroms „0“ nachteilig ist. Das Gate2 mit der entsprechenden Vorspannung kann nicht nur den Lesestrom „1“ erhöhen, sondern auch den Lesestrom „0“ schwächen. Unter Anwendung der optimierten Programmierbedingung in Tabelle 1 ist das Einschwingverhalten des DGTFET-DRAM mit den Standardparametern in Fig. 3b gezeigt. Die Schreib- und Lese- sowie Haltezeiten sind auf 50 ns bzw. 100 ns eingestellt. Das erhaltene aktuelle Verhältnis von Messwert „1“ zu Messwert „0“ beträgt etwa 10 4 , die dieselbe ist wie in [17, 19, 20].

Auswirkung von Spacer-Dielektrika

Beim DGTFET-DRAM beeinflusst die Verwendung von Low-k- oder High-k-Dielektrika in drei Abstandshaltern (S_Spacer, G_Spacer und D_Spacer) seine Leistung. In diesem Design wählen die Low-k- und High-k-Dielektrika das SiO2 und HfO2 , bzw. Wenn jeder Abstandhalter SiO2 . verwendet oder HfO2 , wird es insgesamt acht Kombinationen der Spacer-Technik geben. Für eine umfassendere Analyse sind die Leistungseigenschaften von DGTFET DRAM mit jeder Kombination, einschließlich des Lesens von „1“ (I 1 ) und „0“ (I 0 ) Ströme sowie Stromverhältnis (I 1 / Ich 0 ) werden aus den Übergangsreaktionen extrahiert, wie in Tabelle 2 gezeigt. Um die RT zu bewerten, werden diese Parameter auch extrahiert, wenn die Haltezeit auf 2 s erhöht wird, was in den folgenden Abschnitten erörtert wird. In Tabelle 2 stehen die Buchstaben „S“ und „H“ für SiO2 und HfO2 , und drei Buchstaben jeder Abkürzung stehen jeweils für S_Spacer, G_Spacer und D_Spacer.

Aus Tabelle 2 kann die optimale Abstandshaltertechnik ausgewählt werden. Das Ich 1 sind ungefähr 10 −7 A/μm und 10 −9 A/μm bei SiO2 und HfO2 werden jeweils in S_Spacer verwendet. Wenn der D_Spacer das HfO2 . anwendet , das Ich 0 ist niedrig auf etwa 10 −14 A/μm. Daher besteht die optimale Abstandshalterkonfiguration des DGTFET-DRAM darin, dass auf der Source- und der Drain-Seite Dielektrika mit niedrigem k und hohem k verwendet werden sollten. Die konkreten Gründe werden in den folgenden Abschnitten systematisch analysiert.

Auswirkungen des S_Spacer-Dielektrikums

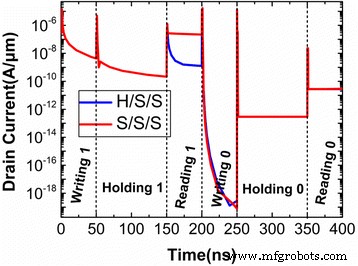

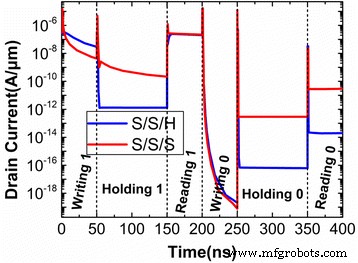

Um die Einflüsse von S_Spacer zu analysieren, werden die Einschwingvorgänge der Drain-Ströme für H/S/S und S/S/S in Abb. 4 verglichen. Es kann beobachtet werden, dass der Messwert „1“ um etwa zwei . verbessert wird Größenordnungen, wenn das SiO2 wird als S_Spacer-Dielektrikum gewählt.

Transiente Reaktionen der Drain-Ströme für H/S/S und S/S/S betrieben in Tabelle 1

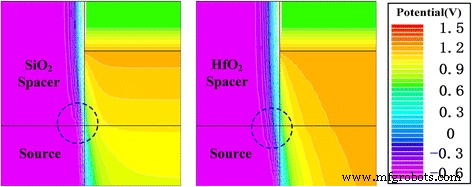

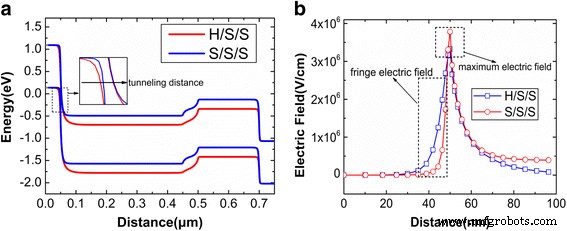

Abbildung 5 zeigt die möglichen Konturen von S/S/S und H/S/S. Am Source-Tunnelübergang ist der Oberflächenverarmungsbereich von H/S/S im Vergleich zu dem von S/S/S offensichtlich erweitert, wie in dem Kreis in Fig. 5 gezeigt. Der erweiterte Oberflächenverarmungsbereich erhöht die Tunnelbarrierenbreite. Abbildung 6a zeigt die Energiebänder nach dem Lesen von "1". Wie im lokal vergrößerten Bereich dieser Figur gezeigt, ist der Tunnelabstand (siehe die Pfeile) von H/S/S offensichtlich größer als der von S/S/S, was durch den erweiterten Oberflächenverarmungsbereich verursacht wird. Außerdem ist nach dem Lesen von "1" das elektrische Feld am oberen Ende des Source-Tunnelübergangs in Fig. 6b gezeigt. Es kann festgestellt werden, dass das elektrische Randfeld von H/S/S größer ist als das von S/S/S, was der Hauptgrund für die Ausdehnung des Oberflächenverarmungsbereichs ist. Kurz gesagt, S_Spacer mit High-k (HfO2 ) Dielektrikum erzeugt das größere elektrische Randfeld, so dass der Oberflächenverarmungsbereich am Source-Tunnelübergang erweitert wird, was den Tunnelabstand der Elektronen erhöht und den Lesestrom „1“ verringert. Außerdem ist aus Fig. 6b zu entnehmen, dass das maximale elektrische Feld von S/S/S größer ist als das von H/S/S. Die exponentielle Beziehung zwischen BTBT-Rate und elektrischem Feld macht den Tunnelstrom von S/S/S viel größer als den von H/S/S [30]. Daher ist der S_Spacer mit dem Low-k-Dielektrikum (SiO2 ) wirkt sich positiv auf den Strom „1“ aus.

Mögliche Konturen von S/S/S (links) und H/S/S (rechts) nach dem Lesen von „1“

a Energieband von Quelle zu Senke und b elektrisches Feld an der Spitze des Source-Tunnelübergangs

In Fig. 6a hat das Dielektrikum S_Spacer auch den Einfluss auf das Energieband des Kanalbereichs. In Fig. 6b ist das elektrische Feld von S/S/S im Kanalbereich größer, so dass sein Kanalpotential geringer ist als das von H/S/S. Als Ergebnis ist das höhere Energieniveau in S/S/S zu finden. Dies kann jedoch keine Auswirkungen auf die Tunnelbarriere und das Lesen des Stroms „1“ haben.

Auswirkungen des D_Spacer-Dielektrikums

Anschließend wird in dieser Arbeit auch der D_Spacer untersucht. Beibehaltung der Konstanten S_Spacer und G_Spacer (SiO2 in diesen beiden Spacern verwendet wird), sind die unterschiedlichen transienten Drainströme, die durch die verschiedenen D_Spacer-Dielektrika verursacht werden, in 7 dargestellt. Abgesehen vom Lesen von „1“ und Schreiben von „0“ hängen die anderen Operationen offensichtlich vom D_Spacer-Dielektrikum ab. Dies liegt daran, dass D_Spacer weit vom Leitweg „1“ (unterer Kanal unter Gate2) entfernt ist. Aus dem vorherigen Betriebsmechanismus kann gelernt werden, dass Schreib- und Haltevorgänge von Gate2 gesteuert werden, sodass das Dielektrikum D_Spacer die Einflüsse auf diese beiden Vorgänge ausüben kann.

Transiente Reaktionen der Drain-Ströme für S/S/H und S/S/S betrieben in Tabelle 1

Während des Haltevorgangs werden die beim Schreiben von "1" angesammelten Löcher aus der Potentialmulde entfernt und auf der Drain-Seite wieder zusammengeführt. Der Haltestrom „1“ kommt also hauptsächlich vom SRH-Rekombinationsstrom. Aufgrund der stärkeren Steuerbarkeit von Gate2 über den Kanal in S/S/S hat S/S/S die größere Rekombinationsrate und hält den Strom „1“. Aber es ist viel weniger als der BTBT-Strom während des Lesens von „1“, sodass der höhere Haltestrom „1“ nicht im Lesen des Stroms „1“ widergespiegelt werden kann.

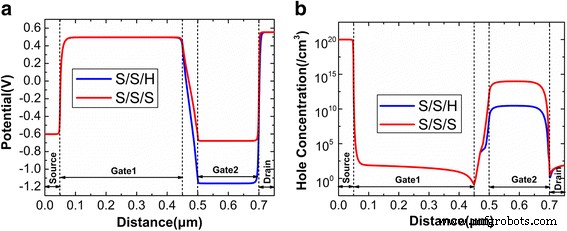

Während des Schreibens von "1" beeinflusst das Dielektrikum D_Spacer die Potentialtopftiefe signifikant. Die Potentialkontur in Abb. 8a zeigt, dass D_Spacer mit HfO2 Dielektrikum erzeugt einen tieferen Potentialtopf. Dies impliziert, dass der effektive BTBT zwischen Drain und Kanal in einen tieferen Kanalbereich ausgedehnt wird. Daher ist der Schreibstrom „1“ von S/S/H höher als der von S/S/S. Während „0“ gehalten wird, wird zwar eine kleine negative Vorspannung (− 0,2 V) an Gate2 angelegt, kann aber auch das Energieband des Kanals unter Gate2 aufbauen, was den BTBT auf der Drain-Seite induziert. Durch die vorherige Analyse kann man erfahren, dass D_Spacer mit SiO2 Dielektrikum verstärkt den BTBT am Drain-Tunnelübergang während des Haltens von "0", was durch die höhere Lochkonzentration für S/S/S demonstriert werden kann, wie in 8b gezeigt. Daher der D_Spacer mit SiO2 Dielektrikum ergibt den höheren Haltestrom „0“.

a Mögliche Kontur nach dem Schreiben von „1“. b Lochkonzentration nach dem Halten von „0“

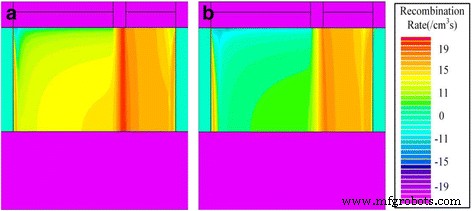

Da die Kanalbarriere zwischen Gate1 und Gate2 beim Lesen von „0“ verhindert, dass die Elektronen zur Drain-Seite fließen, wird die Differenz des Lesens von „0“-Strom für S/S/H und S/S/S hauptsächlich durch den Rekombinationsstrom verursacht . Je mehr Löcher sich während des Haltens von „0“ für S/S/S ansammeln, so dass das fallende Energieband die Rekombinationsrate von S/S/S größer macht als die von S/H/S während des Lesens von „0“, wie gezeigt in Fig. 9. Als Ergebnis, wenn der D_Spacer SiO2 . verwendet , sollte der höhere Messwert „0“ dem höheren Rekombinationsstrom zugeschrieben werden, der durch die mehr akkumulierten Löcher während des Haltens von „0“ verursacht wird.

Rekombinationsrate von a S/S/S und b S/S/H nach dem Lesen von „0“

Zusammenfassend lässt sich sagen, dass die optimale Spacer-Technik für DGTFET-DRAM darin besteht, dass die Spacer auf der Source- und Drain-Seite die Low-k- bzw. High-k-Dielektrika verwenden sollten. Aus Tabelle 2 ist ersichtlich, dass G_Spacer keinen Einfluss auf den DGTFET DRAM hat, wenn die anderen Spacer unverändert bleiben. Dies liegt daran, dass BTBTs, die die Schreib- und Lesevorgänge dominieren, frei von dem Einfluss von G_Spacer sind.

Aufbewahrungszeit

Wie zuvor erläutert, verschlechtern die Lochrekombination und -erzeugung während des Haltens von "1" bzw. "0" den Zustand "1" bzw. "0". Als Ergebnis ist es notwendig, die Leistungsverschlechterung des DGTFET-DRAM bei längerer Haltezeit zu untersuchen. In Tabelle 2 ist das I 1 und ich 0 mit zunehmender Haltezeit stark abbauen. In allen Geräten ich 1 /Ich 0 ist immer noch größer als 10 4 für Gerät mit optimaler Abstandstechnik (S/S/H und S/H/H), wenn die Haltezeit auf 2 s ansteigt.

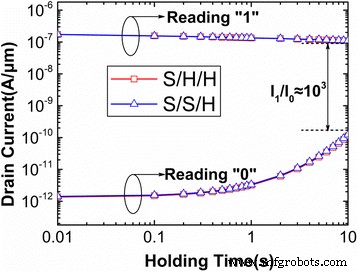

Im Allgemeinen ist die Haltezeit erforderlich, um den maximalen Erfassungsspielraum zu reduzieren (Unterschied zwischen I 1 und ich 0 ) um 50 % wird als RT bewertet. In diesem Design wird eine strengere RT als maximale Haltezeit definiert, wenn die I 1 /Ich 0 ist höher als 10 3 . Abbildung 10 zeigt die Variation des Lesestroms mit der Haltezeit für S/S/H und S/H/H. Es kann festgestellt werden, dass das aktuelle Verhältnis von S/H/S und S/H/H bis zu 10 3 . beträgt wenn die Haltezeit auf 10 s ansteigt. Als Ergebnis kann die RT von DGTFET DRAM mit optimaler Spacer-Technik bis zu 10 s erreichen. Dies ist weit über dem Zielwert von 64 ms. Tabelle 3 vergleicht die Leistungseigenschaften in dieser Arbeit mit denen in [17,18,19,20]. In [19, 20] beträgt das aktuelle Verhältnis nur 10 2 , und die RT ist viel kleiner als 10 s. Darüber hinaus ist der Ablesestrom „0“ in dieser Arbeit zwei Größenordnungen niedriger als in [19, 20]. Die Versuchsergebnisse zu FD-SOI-TFET-DRAM zeigen auch, dass deren Messwert „0“ Strom und RT schlechter sind als in dieser Arbeit. Diese überlegene Leistung zeigt, dass DGTFET ein Ersatz für DRAM mit geringem Stromverbrauch ist. Die Optimierung der Spacer-Technik führt dazu, dass der DGTFET-DRAM einen niedrigen Lesestrom „0“ und eine hohe RT erreicht, was für die Reduzierung des statischen und dynamischen Stromverbrauchs hilfreich ist.

Variation des Lesestroms mit der Haltezeit für S/S/H und S/H/H

Skalierbarkeit des DGTFET-DRAM

Obwohl der DGTFET-DRAM das Problem der Speicherzellendichte aufgrund des Eliminierens des Kondensators mit der großen Größe löst, ist es notwendig, seine Skalierbarkeit zu untersuchen. Das Ziel der Skalierbarkeit besteht darin, die RT höher als 2 s zu halten. Tabelle 4 extrahiert die Leistungseigenschaften von S/S/H mit der Abnahme von L g1 , L g2 , und L Lücke . In Tabelle 4 stehen die drei Zahlen jeder Abkürzung für L g1 , L Lücke , und L g2 .

Aus Tabelle 4 ist ersichtlich, dass I 1 nimmt extrem ab, wenn Lg1 von 200 nm auf 100 nm reduziert. Die Skalierung von Lg1 über 100 nm verengt die vom n-Typ induzierte Barriere, was zu einer verringerten Steuerbarkeit des Gates und einem verschlechterten I . führt 1 . Das Ich 0 steigt signifikant mit abnehmendem L g1 und L g2 . Die Reduzierung von L g2 verringert die Breite der Kanalbarriere zwischen Gate1 und Gate2, was dazu führt, dass ein Teil der Elektronen die Barriere passiert, um das höhere I . zu bilden 0 . Darüber hinaus ist das kontinuierliche Herunterskalieren von L g1 schwächt die Fähigkeit von Gate1, die Tunnelelektronen auf der Oberfläche des Kanals während des Lesens von „0“ einzuschränken. In Tabelle 4 ist das L Lücke hat keinen offensichtlichen Einfluss auf das Ich 1 , aber das Ich 0 steigt leicht mit abnehmendem L Lücke . L . reduzieren Lücke unter 20 nm ermöglicht ein stärkeres Tunneln in Richtung Gate2, wodurch der Zustand „0“ verschlechtert und somit die Retentionszeit verkürzt wird.

Um sicherzustellen, dass das I 1 /Ich 0 und Aufbewahrungszeit sind größer als 10 2 bzw. 2 s das minimale L g1 , L g2 , und L Lücke werden als 200, 150 bzw. 20 nm angesehen. Diese minimale Gerätegröße ist etwas kleiner als die in [17,18,19,20], wie in Tabelle 3 gezeigt. Die minimale Größe des DGTFET-DRAM ist jedoch immer noch größer als die des 20 nm/18 nm-Knotens 1T1C-DRAM [31 ], was der inhärente Nachteil von DGTFET DRAM ist. Aber seine Vorteile von kondensatorlos, geringer Leistung und hoher RT können mit Hilfe der Optimierung der Spacer-Technik nicht ignoriert werden. Die Reduzierung der Größe von DGTFET-DRAM über 100 nm hinaus wird der Schwerpunkt unserer Arbeit in Zukunft sein.

Schlussfolgerungen

In diesem Artikel wird die Optimierung des Spacer-Engineerings für DGTFET-DRAM mit dem Silvaco-Atlas-Tool untersucht. Die Spacer auf der Source- und Drainseite haben den Haupteinfluss auf die Leistung von DGTFET DRAM. Das vergrößerte elektrische Randfeld durch den Source-Spacer mit HfO2 macht den Oberflächenverarmungsbereich am Source-Tunnelübergang erweitert, was den Lesestrom „1“ verringert. Wenn das SiO2 Dielektrikum wird im Drain-Spacer verwendet, der stärkere BTBT induziert beim Halten von „0“ mehr Löcher, was den Rekombinationsstrom beim Lesen von „0“ erhöht. Daher besteht die optimale Spacer-Technik darin, dass Low-k- und High-k-Dielektrika in Drain- bzw. Source-Spacern verwendet werden sollten. Durch die Optimierung der Spacer-Technik erhält der DGTFET DRAM herausragende Vorteile – extrem niedriger Lesestrom „0“ und höhere Retentionszeit (10s) im Vergleich zu anderen verwandten Arbeiten. Darüber hinaus zeigt die Analyse zur Skalierbarkeit, dass die minimale Gerätegröße immer noch größer ist als die des neuesten 20 nm/18 nm Node 1T1C DRAM. Dieser inhärente Mangel weist darauf hin, dass die Reduzierung der Größe des DGTFET-DRAM über 100 nm hinaus der Schwerpunkt unserer Arbeit für DGTFET-DRAM in Zukunft sein wird.

Abkürzungen

- DGTFET:

-

Dual-Gate-Tunneleffekttransistor

- DRAM:

-

Dynamischer Arbeitsspeicher

Nanomaterialien

- Der Unijunction-Transistor (UJT)

- Sensorbasierte Projektideen für Ingenieurstudenten im Abschlussjahr

- Zuverlässigkeitstechnische Prinzipien für den Anlagenbauer

- IBM-Wissenschaftler erfinden ein Thermometer für die Nanoskala

- Der Wert von Cloud-basiertem Slicing und Dateimanagement für den 3D-Druck

- Hochreflektierende Dünnschicht-Optimierung für Vollwinkel-Mikro-LEDs

- Das beste Level für Optimierung und Organisation in der Smart Factory

- So finden Sie die kundenspezifischen technischen Lösungen, nach denen Sie suchen

- Ein Mangel an Diversität könnte für die wachsende Qualifikationslücke in der Branche verantwortlich sein

- Danke für die Erinnerungen!