So verwenden Sie eine Case-When-Anweisung in VHDL

Die Case-When-Anweisung bewirkt, dass das Programm abhängig vom Wert eines Signals, einer Variablen oder eines Ausdrucks einen von mehreren verschiedenen Pfaden nimmt. Es ist eine elegantere Alternative zu einer If-Then-Elsif-Else-Anweisung mit mehreren Elsifs.

Andere Programmiersprachen haben ähnliche Konstrukte und verwenden Schlüsselwörter wie switch , Fall , oder auswählen . Unter anderem werden Case-When-Anweisungen häufig zur Implementierung von Multiplexern in VHDL verwendet. Lesen Sie weiter oder sehen Sie sich das Video an, um herauszufinden, wie!

Dieser Blogpost ist Teil der Reihe Basic VHDL Tutorials.

Die grundlegende Syntax für die Case-When-Anweisung lautet:case <expression> is

when <choice> =>

code for this branch

when <choice> =>

code for this branch

...

end case;

Die <expression> ist normalerweise eine Variable oder ein Signal. Die Case-Anweisung kann mehrere when enthalten Auswahlmöglichkeiten, aber nur eine Auswahl wird ausgewählt.

Die <choice> kann ein eindeutiger Wert wie "11" sein :when "11" =>

Oder es kann ein Bereich wie 5 to 10 sein :when 5 to 10 =>

Es kann mehrere Werte wie 1|3|5 enthalten :when 1|3|5 =>

Und vor allem der others Auswahl. Es wird ausgewählt, wenn keine andere Auswahl getroffen wurde:when others =>

Die others Wahl ist äquivalent zu Else Verzweigung in der If-Then-Elsif-Else-Anweisung.

Übung

In diesem Video-Tutorial lernen wir, wie man einen Multiplexer mit der Case-When-Anweisung in VHDL erstellt:

Der endgültige Code, den wir in diesem Tutorial erstellt haben:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T14_CaseWhenTb is

end entity;

architecture sim of T14_CaseWhenTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output1 : unsigned(7 downto 0);

signal Output2 : unsigned(7 downto 0);

begin

-- Stimuli for the selector signal

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

-- MUX using if-then-else

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

if Sel = "00" then

Output1 <= Sig1;

elsif Sel = "01" then

Output1 <= Sig2;

elsif Sel = "10" then

Output1 <= Sig3;

elsif Sel = "11" then

Output1 <= Sig4;

else -- 'U', 'X', '-' etc.

Output1 <= (others => 'X');

end if;

end process;

-- Equivalent MUX using a case statement

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output2 <= Sig1;

when "01" =>

Output2 <= Sig2;

when "10" =>

Output2 <= Sig3;

when "11" =>

Output2 <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output2 <= (others => 'X');

end case;

end process;

end architecture;

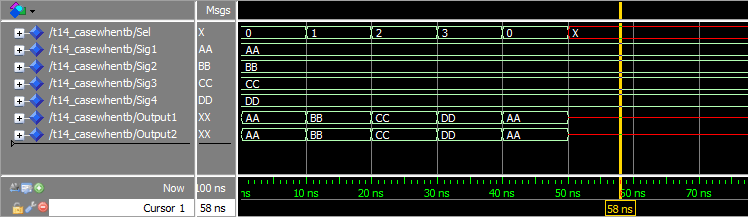

Das Wellenformfenster in ModelSim, nachdem wir auf Ausführen gedrückt und die Zeitachse vergrößert haben:

Die Ausgabe an die Simulatorkonsole, wenn wir in ModelSim die Run-Taste gedrückt haben:

VSIM 2> run # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb

Analyse

Zuerst haben wir einen Prozess mit If-Then-Elsif-Else erstellt, der eines der Signale Sig1 weiterleiten würde , Sig2 , Sig3 , oder Sig4 , basierend auf dem Wert des Auswahlsignals Sel .

Dann haben wir einen Prozess erstellt, der genau dasselbe tat, indem wir die Case-When-Anweisung verwendeten. Wir können aus der Wellenform ersehen, dass die Ausgangssignale der beiden Prozesse Output1 sind und Output2 , verhalten sich genauso.

In unserem Beispiel der Sel Signal hat nur vier gültige Werte. Aber wenn es eine größere Anzahl von Möglichkeiten gegeben hätte, können wir leicht erkennen, dass die Case-When-Anweisung dazu beitragen kann, den Code lesbarer zu machen. Dies ist die von den meisten VHDL-Designern bevorzugte Methode zum Erstellen einer solchen Komponente.

Verständnis des Multiplexers war der Bonuspunkt dieser Übung. Multiplexer, kurz MUX’s, sind zentrale Komponenten im digitalen Design. Es ist einfach ein Schalter, der einen von mehreren Eingängen auswählt und an den Ausgang weiterleitet.

So leitet unser MUX das gewählte Eingangssignal weiter:

Wir haben den others verwendet -Klausel, um alle Werte von Sel abzufangen die keine Einsen oder Nullen waren. Wie wir im std_logic-Tutorial gelernt haben, können diese Signale eine Reihe von Werten haben, die nicht '0' sind oder '1' . Es ist eine gute Designpraxis, mit diesen Werten umzugehen, indem Sie 'X' ausgeben . Dies weist auf einen unbekannten Wert dieses Signals hin und wird auch in der nachgeschalteten Logik sichtbar sein.

Wir können aus der Wellenform ersehen, dass bei Sel Signal wurde rot, Output1 und Output2 ebenfalls geändert in "XX" . Dies ist when others => in Aktion.

Außerdem zeigt die Konsolenausgabe in ModelSim eine Warnung wegen Sel Signal auf "UU" gesetzt . Die Meldungen „** Warning:NUMERIC_STD.“=“:Metawert erkannt, FALSE zurückgeben“ erscheinen bei 50 ns Simulationszeit, genau dann, wenn die Signale rot werden.

Imbiss

- Case-When kann anstelle mehrerer If-Then-Elsif-Anweisungen verwendet werden

- Der

when others =>kann verwendet werden, um eine Standardauswahl zu implementieren - Multiplexer werden vorzugsweise mit Case-When-Anweisungen erstellt

Weiter zum nächsten Tutorial »

VHDL

- Prozeduranweisung – VHDL-Beispiel

- Wie verwenden wir Molybdän?

- So erstellen Sie eine Liste von Zeichenfolgen in VHDL

- So stoppen Sie die Simulation in einer VHDL-Testbench

- So erstellen Sie einen PWM-Controller in VHDL

- So generieren Sie Zufallszahlen in VHDL

- So verwenden Sie eine Prozedur in einem Prozess in VHDL

- So verwenden Sie eine unreine Funktion in VHDL

- So verwenden Sie eine Funktion in VHDL

- So verwenden Sie einen Cutter Grinder