So erstellen Sie eine gleichzeitige Anweisung in VHDL

Eine gleichzeitige Anweisung in VHDL ist eine Signalzuweisung innerhalb der Architektur, aber außerhalb eines normalen Prozesskonstrukts. Die gleichzeitige Anweisung wird auch als gleichzeitige Zuweisung oder gleichzeitiger Prozess bezeichnet.

Wenn Sie eine gleichzeitige Anweisung erstellen, erstellen Sie eigentlich einen Prozess mit bestimmten, klar definierten Merkmalen. Gleichzeitige Anweisungen entsprechen immer einem Prozess, der eine Sensitivitätsliste verwendet, wobei alle Signale rechts vom Signalzuweisungsoperator auf der Sensitivitätsliste stehen.

Diese Kurznotationsprozesse sind nützlich, wenn Sie eine einfache Logik erstellen möchten, die zur Zuweisung eines einzelnen Signals führt. Anstatt ein vollständiges Prozesskonstrukt mit Sensitivitätslisten und all dem abzutippen, können Sie das Zielsignal einfach direkt in der Architektur zuweisen.

Dieser Blogpost ist Teil der Reihe Basic VHDL Tutorials.

Bei richtiger Verwendung ist die Absicht des Codes immer noch ziemlich klar. Sie müssen nicht für jedes einzelne Bit, das Sie umdrehen möchten, einen Prozess erstellen.

Übung

In diesem Video lernen wir, wie man eine gleichzeitige Anweisung erstellt:

Der endgültige Code, den wir in diesem Tutorial erstellt haben:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

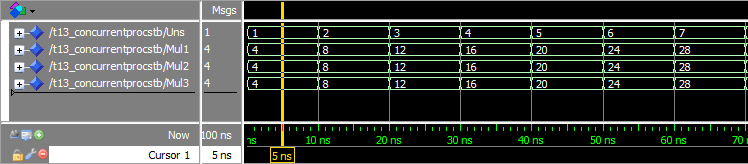

Das Wellenformfenster in ModelSim, nachdem wir auf Ausführen gedrückt und die Zeitachse vergrößert haben:

Analyse

Wir können an der Wellenform erkennen, dass Mul1 , Mul2 , und Mul3 verhalten sich genau gleich. Dies liegt daran, dass die gleichzeitige Anweisung und die beiden von uns erstellten Prozesse äquivalent sind.

Eine gleichzeitige Anweisung funktioniert genau wie ein Prozess. Alle Signale rechts von <= werden automatisch zur Vertraulichkeitsliste hinzugefügt. Das bedeutet, dass das Signal links von <= wird immer dann aktualisiert, wenn sich eines der ausgewerteten Signale ändert.

Es gibt viele Möglichkeiten, Zahlen in VHDL zu multiplizieren. In dieser Übung haben wir den Uns multipliziert Signal um 4, unter Verwendung von Bitverschiebung. Alle unsere Signale sind von unsigned Typ, was bedeutet, dass sie durch Zahlen interpretiert werden. Das Anhängen einer 0 rechts an eine Binärzahl entspricht der Multiplikation mit 2.

Dies ist eine Illustration dessen, was am Cursor in der Wellenform passiert:

Imbiss

- Eine nebenläufige Anweisung ist eine Signalzuweisung direkt im Architekturbereich

- Concurrent Statements entsprechen einem Prozess mit allen ausgewerteten Signalen auf der Sensitivitätsliste

Weiter zum nächsten Tutorial »

VHDL

- Prozeduranweisung – VHDL-Beispiel

- So erstellen Sie eine Liste von Zeichenfolgen in VHDL

- So erstellen Sie eine Tcl-gesteuerte Testbench für ein VHDL-Code-Sperrmodul

- So stoppen Sie die Simulation in einer VHDL-Testbench

- So erstellen Sie einen PWM-Controller in VHDL

- So erstellen Sie einen Ringpuffer-FIFO in VHDL

- So erstellen Sie eine selbstüberprüfende Testbench

- So erstellen Sie eine verknüpfte Liste in VHDL

- So verwenden Sie eine Prozedur in einem Prozess in VHDL

- So verwenden Sie eine Funktion in VHDL