Verwendung des gängigsten VHDL-Typs:std_logic

Der in VHDL am häufigsten verwendete Typ ist std_logic . Stellen Sie sich diesen Typ als ein einzelnes Bit vor, die digitale Information, die von einem einzigen physischen Draht übertragen wird. Die std_logic gibt uns eine feinkörnigere Kontrolle über die Ressourcen in unserem Design als integer Typ, den wir in den vorherigen Tutorials verwendet haben.

Normalerweise möchten wir, dass eine Leitung in einer digitalen Schnittstelle entweder den Wert '1' hat oder '0' . Diese beiden Werte sind die einzigen Werte, die ein Bit, eine Binärziffer, haben kann. Aber in Wirklichkeit kann ein physisches digitales Signal in einer Reihe von Zuständen sein, die der std_logic Typ leistet gute Arbeit bei der Nachahmung. Daher ist es der am häufigsten verwendete Typ in VHDL.

Dieser Blogpost ist Teil der Reihe Basic VHDL Tutorials.

Die std_logic Typ kann die folgenden Werte haben:

| ‘1‘ | Logik 1 |

| ‘0’ | Logisch 0 |

| ‘Z’ | Hohe Impedanz |

| „W“ | Schwaches Signal, kann nicht sagen, ob 0 oder 1 |

| „L“ | Schwache 0, Pulldown |

| ‘H‘ | Schwach 1, Klimmzug |

| ‘-‘ | Egal |

| ‘U‘ | Nicht initialisiert |

| „X“ | Unbekannt, mehrere Treiber |

Dies mag wie viele verschiedene Zustände für einen Typ erscheinen, der einen einzelnen Binärwert modellieren soll. Keine Sorge, wir werden in dieser Tutorial-Serie nicht alle diese Typen verwenden. Wir werden '1' verwenden und '0' Natürlich. Und wir werden auch 'U' sehen und 'X' , was uns hilft, Fehler in unserem Design zu erkennen. Die anderen Werte sind erweiterte VHDL-Funktionen, die für Dinge wie die Modellierung der Kommunikation mit beispielsweise I

2

verwendet werden können C-Geräte oder zum Erstellen von Tri-State-Bussen.

Wenn mehrere Prozesse versuchen, unterschiedliche Werte in ein Signal zu schreiben, sprechen wir von mehreren Treibern . Wenn ein std_logic Signal mehrere Treiber hat, wird es kein Kompilierungs- oder Laufzeitfehler sein, zumindest nicht im Simulator. Das liegt daran, dass std_logic ist ein aufgelöster Typ , was bedeutet, dass sein Wert durch eine Auflösungsfunktion bestimmt wird.

Der Wert von std_logic Signal mit zwei Treibern wird basierend auf dieser Auflösungstabelle bestimmt:

| U | X | 0 | 1 | Z | W | L | H | – | |

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

Übung

In diesem Video-Tutorial lernen wir, wie Sie std_logic deklarieren und anzeigen Signale in einer Wellenform:

Der endgültige Code, den wir in diesem Tutorial erstellt haben:

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

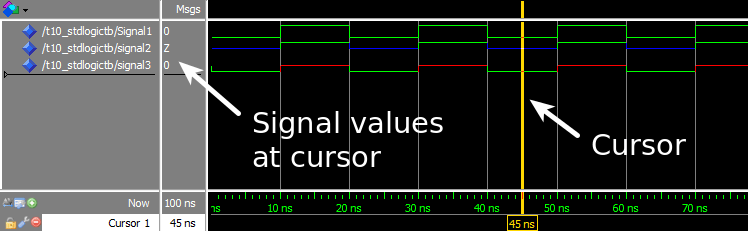

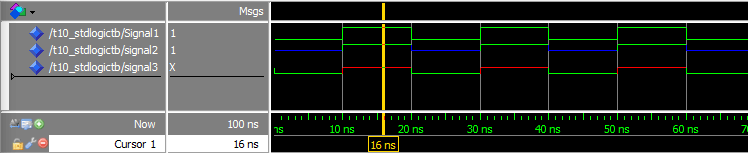

Das Wellenformfenster in ModelSim, nachdem wir auf Ausführen gedrückt und die Zeitleiste vergrößert haben:

Die Wellenform mit dem Cursor auf dem anderen Teil des sich wiederholenden Signalzyklus:

Analyse

Die Übung zeigte, wie die Auflösungsfunktion von VHDL mit dem std_logic funktioniert Typ. Bei der Arbeit mit digitaler Logik ist es oft praktischer, die Zeitachse in einer Wellenform zu studieren anstatt Ausdrucke zu verwenden. Daher haben wir in dieser Übung die ModelSim-Wellenform verwendet, um die Signalwerte zu überprüfen.

Der erste Prozess und Signal1 wird nur verwendet, um den Wert zu ändern, den der dritte Prozess auf Signal2 steuert und Signal3 .

Der zweite Prozess, Fahrer A, versucht, eine 'Z' zu fahren auf Signal2 , und ein '0' auf Signal3 ständig.

Der dritte Prozess, Fahrer B, wechselt zwischen dem Fahren von '1' und 'Z' auf beide Signal2 und Signal3 .

Wir sehen in den Wellenform-Screenshots, dass Signal1 wechselt zwischen '0' und '1' , weil es nur einen Prozess gibt, der versucht, dieses Signal zu treiben. Wir können auch sehen, dass die mehreren Treibersignale gemäß der Auflösungstabelle in den VHDL-Code-Kommentaren aufgelöst werden:

| Signal | Fahrer A | Fahrer B | Ergebnis |

|---|---|---|---|

| Signal2 | ‘Z‘ | ‘Z‘ | ‘Z‘ |

| Signal2 | ‘Z‘ | ‘1‘ | ‘1‘ |

| Signal3 | ‘0‘ | ‘Z‘ | ‘0‘ |

| Signal3 | ‘0‘ | ‘1‘ | „X“ |

Imbiss

std_logicist der gebräuchlichste Typ, der verwendet wird, um einen Einzelbitwert in VHDL zu speichern- Denken Sie an einen

std_logicSignal als physischer Draht in unserem digitalen Design - Wenn mehrere Prozesse versuchen, einen

std_logiczu steuern Signal, dessen Wert durch eine Auflösungstabelle bestimmt wird

Weiter zum nächsten Tutorial »

VHDL

- Die häufigsten Engpässe im 3D-Druck-Workflow – und wie man sie behebt

- Die häufigsten Probleme mit dem Autokühlsystem

- So nutzen Sie Ihre Daten optimal

- So erstellen Sie eine verknüpfte Liste in VHDL

- So verwenden Sie eine Prozedur in einem Prozess in VHDL

- So verwenden Sie eine unreine Funktion in VHDL

- So verwenden Sie eine Funktion in VHDL

- So verwenden Sie einen Motorheber sicher am Arbeitsplatz

- Die häufigsten Ursachen für Kranunfälle (und wie man sie vermeidet)

- Die häufigsten Anwendungen von a286