So erstellen Sie einen Signalvektor in VHDL:std_logic_vector

Der std_logic_vector Typ kann zum Erstellen von Signalbussen in VHDL verwendet werden. Die std_logic ist der am häufigsten verwendete Typ in VHDL und der std_logic_vector ist die Array-Version davon.

Während die std_logic eignet sich hervorragend zum Modellieren des Werts, der von einem einzelnen Draht übertragen werden kann, ist jedoch nicht sehr praktisch zum Implementieren von Sammlungen von Drähten, die zu oder von Komponenten gehen. Die std_logic_vector ist ein zusammengesetzter Typ, was bedeutet, dass es sich um eine Sammlung von Unterelementen handelt. Signale oder Variablen des std_logic_vector type kann eine beliebige Anzahl von std_logic enthalten Elemente.

Dieser Blogpost ist Teil der Reihe Basic VHDL Tutorials.

Die Syntax zum Deklarieren von std_logic_vector Signale ist:signal <name> : std_logic_vector(<lsb> to <msb>) := <initial_value>;

odersignal <name> : std_logic_vector(<msb> downto <lsb>) := <initial_value>;

wobei <name> ist ein willkürlicher Name für das Signal und <initial_value> ist ein optionaler Anfangswert. Die <lsb> ist der Index des niedrigstwertigen Bits und <msb> ist der Index des höchstwertigen Bits.

Die to oder downto gibt die Richtung der Reichweite des Busses an, im Grunde seine Endianness. Obwohl beide gleich gut funktionieren, deklarieren VHDL-Designer Vektoren am häufigsten mit downto . Daher empfehle ich Ihnen, immer downto zu verwenden wenn Sie Bitvektoren deklarieren, um Verwirrung zu vermeiden.

Der VHDL-Code zum Deklarieren eines Vektorsignals, das ein Byte enthalten kann:signal MySlv : std_logic_vector(7 downto 0);

Der VHDL-Code zum Deklarieren eines Vektorsignals, das ein Bit enthalten kann:signal MySlv : std_logic_vector(0 downto 0);

Der VHDL-Code zum Deklarieren eines Vektorsignals, das Null-Bits enthalten kann (ein leerer Bereich ):signal MySlv : std_logic_vector(-1 downto 0);

Übung

In diesem Video-Tutorial lernen wir, wie man std_logic_vector deklariert Signale und geben ihnen Anfangswerte. Wir lernen auch, wie man mit einer For-Schleife über die Bits in einem Vektor iteriert, um ein Schieberegister zu erstellen :

Der endgültige Code, den wir in diesem Tutorial erstellt haben:

library ieee;

use ieee.std_logic_1164.all;

entity T11_StdLogicVectorTb is

end entity;

architecture sim of T11_StdLogicVectorTb is

signal Slv1 : std_logic_vector(7 downto 0);

signal Slv2 : std_logic_vector(7 downto 0) := (others => '0');

signal Slv3 : std_logic_vector(7 downto 0) := (others => '1');

signal Slv4 : std_logic_vector(7 downto 0) := x"AA";

signal Slv5 : std_logic_vector(0 to 7) := "10101010";

signal Slv6 : std_logic_vector(7 downto 0) := "00000001";

begin

-- Shift register

process is

begin

wait for 10 ns;

for i in Slv6'left downto Slv6'right + 1 loop

Slv6(i) <= Slv6(i-1);

end loop;

Slv6(Slv6'right) <= Slv6(Slv6'left);

end process;

end architecture;

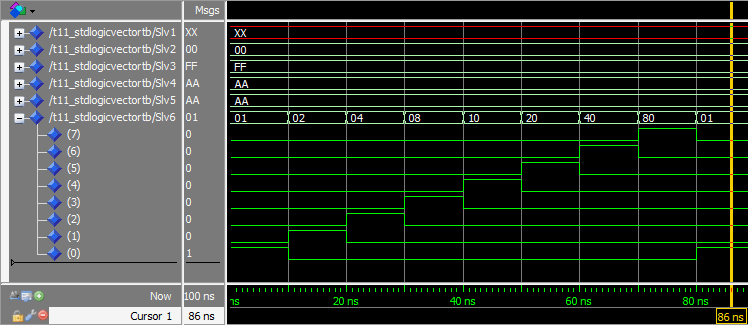

Das Wellenformfenster in ModelSim, nachdem wir auf Ausführen gedrückt und die Zeitachse vergrößert haben:

Analyse

In dieser Übung haben wir sechs std_logic_vector deklariert Busse, jeweils acht Bit lang (ein Byte).

Signal Slv1 wurde ohne Anfangswert deklariert. Der Bus hat im Wellenform-Screenshot den Wert XX. Dies liegt daran, dass der auf dem Bus angezeigte Wert hexadezimal ist und XX einen nicht hexadezimalen Wert angibt. Aber als wir den Bus in der Wellenform erweiterten, konnten wir sehen, dass die einzelnen Bits tatsächlich U’s waren.

Signal Slv2 wurde mit einem Anfangswert aus lauter Nullen deklariert. Anstatt den genauen Wert für jedes Bit anzugeben, haben wir (other => '0') verwendet anstelle des Anfangswertes. Dies wird als Aggregat bezeichnet Abtretung. Der wichtige Teil ist, dass alle Bits im Vektor auf das gesetzt werden, was Sie angeben, egal wie lang er ist.

Signal Slv3 wurde unter Verwendung einer aggregierten Zuweisung deklariert, um allen Bits den Anfangswert 1 zu geben. Wir können FF sehen, das auf diesem Signal in der Wellenform angezeigt wird, was hex für acht Einsen ist.

Signal Slv4 wurde mit einem in Hex, AA angegebenen Anfangswert deklariert. Jede Hex-Ziffer ist 4 Bit lang, daher müssen wir zwei Ziffern (AA) für unseren 8 Bit langen Vektor angeben.

Signal Slv5 deklariert genau denselben Anfangswert wie Slv4 , aber jetzt haben wir es als den Binärwert 10101010 angegeben. Wir können an der Wellenform sehen, dass beide Signale den Hex-Wert AA haben.

Signal Slv6 wurde mit einem Anfangswert aus lauter Nullen deklariert, mit Ausnahme des Bits ganz rechts, das '1' war . Wir haben einen Prozess verwendet, um ein Schieberegister zu erstellen von diesem Signal. Das Schieberegister verschiebt, wie der Name schon sagt, den Inhalt des Vektors alle 10 Nanosekunden um eine Stelle nach links.

Unser Prozess wacht alle 10 ns auf und die For-Schleife verschiebt alle Bits im Vektor um eine Stelle nach links. Das letzte Bit wird durch die Slv6(Slv6'right) <= Slv6(Slv6'left); zurück in den ersten Index geschoben Aussage. In der Wellenform sehen wir den '1' Welligkeit durch den Vektor.

Dies ist eine Visualisierung, wie der '1' propagiert durch unser Schieberegister:

Durch die Verwendung des 'left' und 'right Attribute haben wir unseren Code allgemeiner gemacht. Wenn wir die Breite von Sig6 ändern , funktioniert der Prozess trotzdem. Es ist eine gute Designpraxis, Attribute zu verwenden, wo immer Sie können, anstatt Werte fest zu codieren.

Sie fragen sich vielleicht, ob es noch mehr Attribute gibt, die Sie verwenden können, und das gibt es. Ich werde in dieser Tutorial-Reihe nicht weiter darauf eingehen, da ich sie für fortgeschrittene VHDL-Features halte.

Imbiss

- N-Bit-Vektoren sollten mit

std_logic_vector(N-1 downto 0)deklariert werden - Ein Vektor kann als Ganzes zugewiesen werden oder es kann einzeln auf Bits darin zugegriffen werden

- Alle Bits in einem Vektor können mit der Aggregatzuweisung

(others => '0')auf Null gesetzt werden - Code kann allgemeiner gestaltet werden, indem Attribute wie

'leftverwendet werden und'right

Nehmen Sie am Basic VHDL Quiz – Teil 2 teil »

oder

gehen Sie zum nächsten Tutorial »

VHDL

- Beispiele für VHDL-Konvertierungen

- Signiert vs. Unsigniert in VHDL

- So erstellen Sie eine Liste von Zeichenfolgen in VHDL

- So erstellen Sie eine Tcl-gesteuerte Testbench für ein VHDL-Code-Sperrmodul

- So stoppen Sie die Simulation in einer VHDL-Testbench

- So erstellen Sie einen PWM-Controller in VHDL

- So generieren Sie Zufallszahlen in VHDL

- So erstellen Sie einen Ringpuffer-FIFO in VHDL

- So erstellen Sie eine selbstüberprüfende Testbench

- So erstellen Sie eine verknüpfte Liste in VHDL