Neues ML-basiertes Tool bietet automatisierte Optimierung des Chipdesign-Flusses

Es ist unbestritten, dass das Chipdesign immer komplexer wird, da die Kunden mehr Funktionen und kleinere Geräte sowie einen geringeren Stromverbrauch verlangen. Um dieser Nachfrage gerecht zu werden, werden Ingenieure überlastet und benötigen Unterstützung, um mit der Nachfrage und einer zeitnahen Produktentwicklung Schritt zu halten.

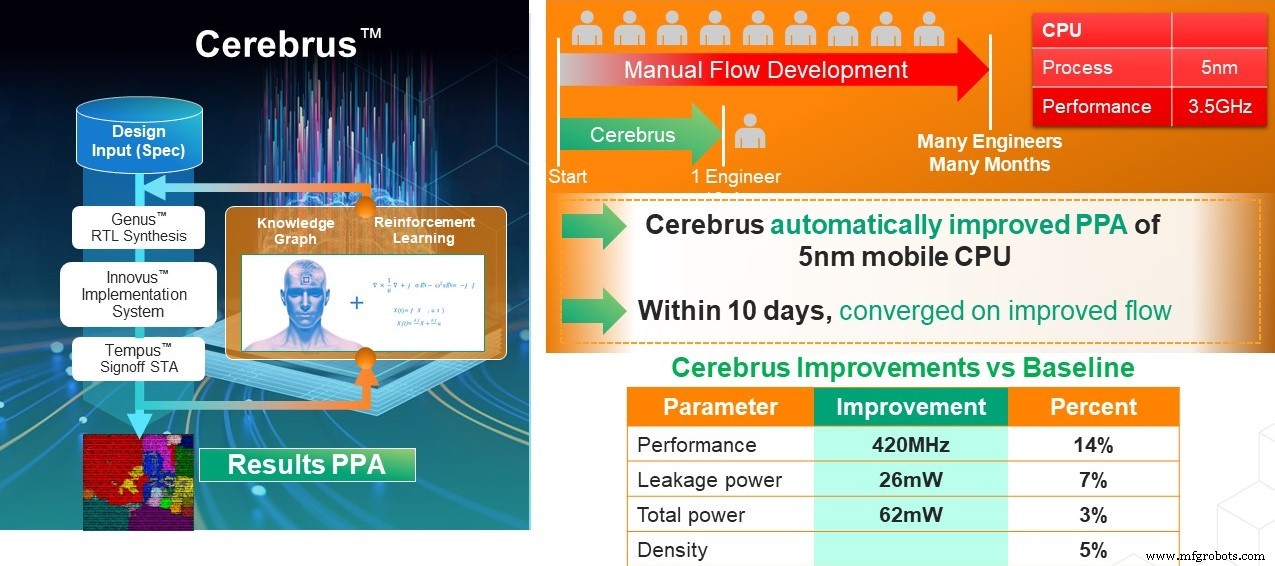

Um dies zu beheben, hat Cadence Design Systems ein neues Tool eingeführt, das maschinelles Lernen (ML) verwendet, um den Cadence RTL-to-Signoff-Implementierungsfluss voranzutreiben und eine bis zu 10-fache Produktivität und 20 % PPA (Leistung, Leistung und Fläche) bietet ) Verbesserungen für die Umsetzung. Der neue Cerebrus Intelligent Chip Explorer bietet effizientere Ressourcenverwaltungsfunktionen für On-Site- und Cloud-Computing als die traditionelle menschengesteuerte Designexploration; und verbessert PPA und Produktivität über viele Knoten und mehrere Endanwendungen hinweg, einschließlich Verbraucher, Hyperscale-Computing, 5G-Kommunikation, Automobil- und Mobildesign.

In einem Briefing mit embedded.com sagte Rod Metcalfe, Product Management Group Director bei Cadence:„Dies ist das erste digitale Full-Flow-Optimierungstool, das ML verwendet. Dies ist wichtig, da mit zunehmender Designkomplexität das Chipdesign mehr Funktionen und Intelligenz erfordert, aber die Anzahl der Ingenieure, die für diese Aufgaben zur Verfügung stehen, begrenzt ist. Wir sehen immer noch, dass Designer manuelle Flow-Entwicklung durchführen und im Kreislauf iterieren, um ihre Designziele zu erreichen:Dies erfordert einen enormen technischen Aufwand und ist nicht skalierbar. Hier kommt Cerebrus ins Spiel und nutzt massive Rechenkapazitäten, um die Produktivität für die Konstruktionsautomatisierung zu verbessern.“

Metcalfe hob ein Beispiel hervor, bei dem Cerebrus nur einen Ingenieur benötigte, um innerhalb von 10 Tagen einen verbesserten Designfluss zu erzielen, um den PPA einer mobilen 5-nm-CPU automatisch zu verbessern (siehe Grafik unten).

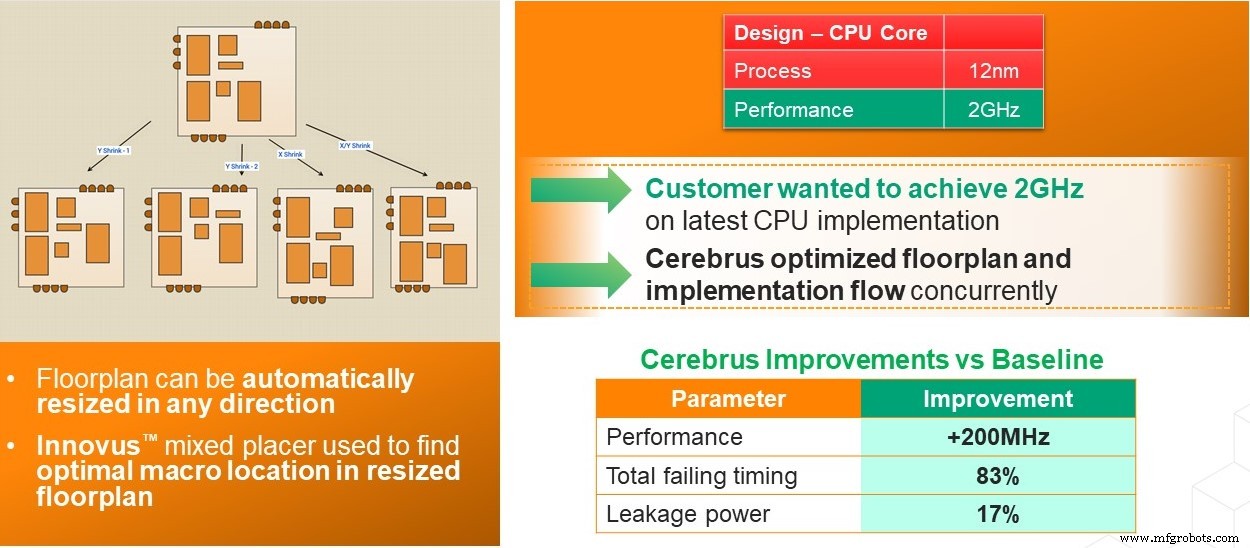

Ein weiteres Beispiel auf einer höheren Ebene ist die automatisierte Grundrissoptimierung, wie in der folgenden Grafik dargestellt:

Die Auswirkung der Verwendung eines ML-basierten Tools wie Cerebrus besteht darin, dass Designteams eine automatisierte Möglichkeit haben, historisches Designwissen wiederzuverwenden – früher hätten sie bei jedem neuen Projekt übermäßig viel Zeit mit manuellem Neulernen verbracht. Laut Cadence markiert Cerebrus daher eine Revolution der EDA-Branche mit ML-gesteuertem digitalem Chip-Design, bei dem Ingenieursteams eine größere Chance haben, mehr Einfluss in ihren Organisationen zu erzielen, da sie manuelle Prozesse entlasten können. Da die Branche weiterhin auf fortschrittliche Knoten umsteigt und die Designgröße und -komplexität zunehmen, wird Cerebrus Designern dabei helfen, PPA-Ziele effizienter zu erreichen.

Frühe Kundenempfehlungen für das Tool kamen von Renesas und Samsung Foundry.

Satoshi Shibatani, Direktor der Abteilung für digitale Konstruktionstechnologie in der gemeinsamen R&D EDA-Abteilung von Renesas, sagte:„Um die Leistung neuer Produkte, die neue Prozessknoten verwenden, effizient zu maximieren, müssen die von unserem Engineering-Team verwendeten digitalen Implementierungsabläufe kontinuierlich aktualisiert werden. Die automatisierte Optimierung des Konstruktionsflusses ist entscheidend, um die Produktentwicklung mit einem viel höheren Durchsatz zu realisieren. Cerebrus hat mit seinen innovativen ML-Funktionen und den Cadence RTL-to-Signoff-Tools eine automatisierte Flussoptimierung und Grundriss-Exploration ermöglicht und die Designleistung um mehr als 10 % verbessert.“

Sangyun Kim, Vice President for Design Technology bei Samsung Foundry, sagte:„Da wir weiterhin aktuelle Prozessknoten einsetzen, ist die Effizienz unseres Design Technology Co-Optimierungsprogramms (DTCO) sehr wichtig. . Als Teil unserer langfristigen Partnerschaft mit Cadence hat Samsung Foundry Cerebrus und den digitalen Implementierungsablauf von Cadence in mehreren Anwendungen verwendet. Wir haben bei einigen unserer kritischsten Blöcke in nur wenigen Tagen eine Leistungsreduzierung von mehr als 8 % im Vergleich zu vielen Monaten manuellen Aufwands festgestellt. Darüber hinaus verwenden wir Cerebrus für die automatische Dimensionierung von Energieverteilungsnetzen im Grundriss, was zu einem um mehr als 50 % besseren endgültigen Design-Timing geführt hat.

Die wichtigsten Funktionen und Vorteile von Cerebrus sind:

- Verstärkung ML : findet schnell Flow-Lösungen, die menschliche Ingenieure normalerweise nicht ausprobieren oder erforschen, wodurch PPA und Produktivität verbessert werden.

- Wiederverwendung von ML-Modellen :ermöglicht die automatische Anwendung von Design-Learnings auf zukünftige Designs, wodurch die Zeit für bessere Ergebnisse verkürzt wird.

- Verbesserte Produktivität :ermöglicht einem einzelnen Ingenieur die automatische Optimierung des gesamten RTL-zu-GDS-Flows für viele Blöcke gleichzeitig, sodass komplette Designteams produktiver arbeiten können.

- Massiv verteiltes Rechnen :bietet skalierbare lokale oder cloudbasierte Designexploration für eine schnellere Flussoptimierung.

- Einfache Benutzeroberfläche: Das leistungsstarke Benutzer-Cockpit ermöglicht interaktive Ergebnisanalysen und das Laufmanagement, um wertvolle Einblicke in Designmetriken zu gewinnen.

Cerebrus ist Teil des breiteren digitalen Vollflusses von Cadence und arbeitet nahtlos mit der Genus-Syntheselösung, dem Innovus-Implementierungssystem, der Tempus-Timing-Signoff-Lösung, der Joules RTL-Stromversorgungslösung, der Voltus IC-Stromintegritätslösung und dem Pegasus-Verifizierungssystem zusammen, um Kunden einen schnellen Weg zu bieten um einen Abschluss und eine bessere Vorhersehbarkeit zu entwickeln.

Eingebettet

- Aufstieg auf eine neue Stufe der Edge-KI

- Pulsic bietet eine Echtzeit-Vorschau des analogen Chip-Layouts im Schaltplaneditor

- SIMULIA Reifenentwicklung und -design

- Pennsylvania bietet neue Finanzierung an, um Studenten in Philadelphia zu helfen, Möglichkeiten in der Fertigung zu entdecken

- Konstruktion von maßgeschneiderten Preforms

- Bar/Chucker mit offener Front und mehr

- Neues Transistordesign tarnt wichtige Computerchip-Hardware zum Schutz vor Hackern

- Sandvik stellt neues Drehkonzept vor

- Die New-Line-Integrationslandschaft

- So fügen Sie ein neues Tool hinzu