Synopsys geht hyperkonvergente ICs mit einem einheitlichen Schaltungssimulationsablauf an

Da das Chipdesign immer komplexer wird und mehrere Komponenten und Technologien in hyperkonvergenten integrierten Schaltkreisen (ICs) zusammenkommen, wäre ein Einzelsystemansatz zur Analyse des Systems ein logischer Weg, um die Komplexität zu vereinfachen. Synopsys geht dies mit einem einheitlichen Schaltungssimulationsworkflow, PrimeSim Continuum, an, um sowohl die Komplexität als auch den Umfang der heutigen heterogenen Architekturchips für Speicher, künstliche Intelligenz (KI), Automobil- und 5G-Anwendungen zu bewältigen.

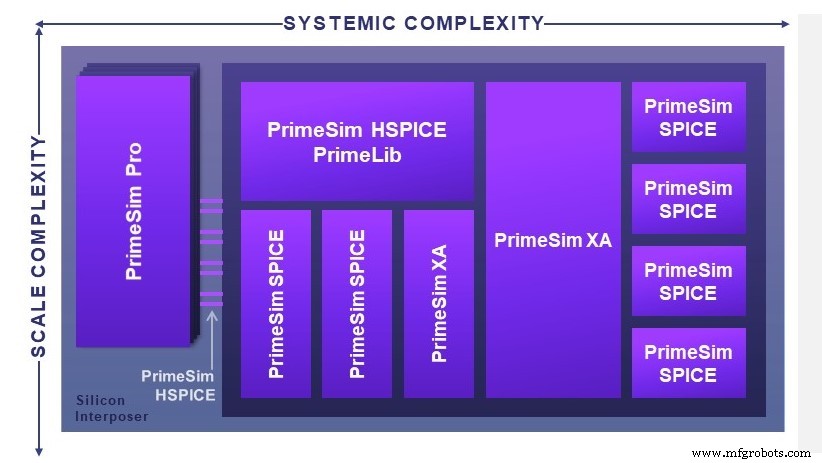

PrimeSim Continuum wurde auf der internationalen Benutzerkonferenz SNUG World vorgestellt und ist eine All-in-One-Lösung, die aus Simulations-Engines wie PrimeSim SPICE, PrimeSim Pro, PrimeSim HSPICE und PrimeSim XA besteht. Diese Designumgebung bietet ein nahtloses Simulationserlebnis für alle PrimeSim-Engines mit umfassender Analyse, verbesserter Produktivität und Benutzerfreundlichkeit. Es bildet die Grundlage der kundenspezifischen Designplattform von Synopsys.

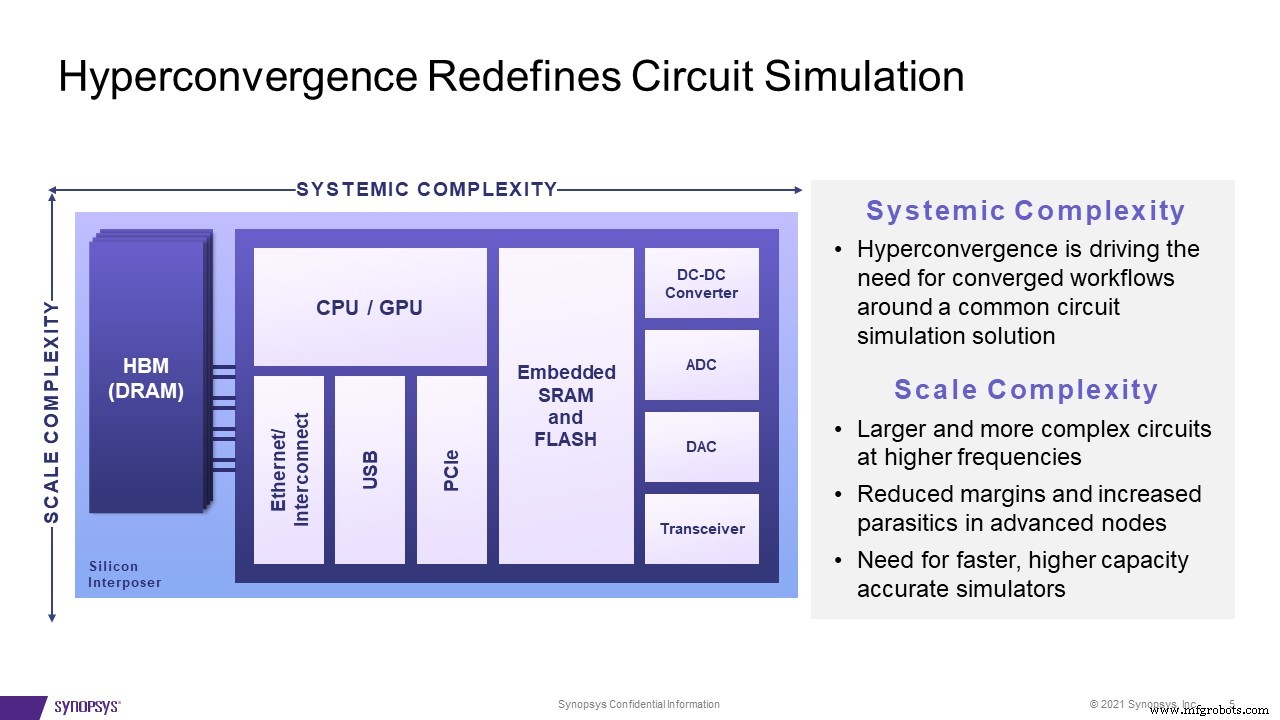

Heutige hyperkonvergente Systeme auf dem Chip (SoCs) bestehen aus unterschiedlichen Komponenten, die auf demselben Chip oder Gehäuse integriert sind. Dazu können größere und schnellere eingebettete Speicher, analoge Front-End-Geräte und komplexe I/O-Schaltungen gehören, die mit Datenraten von über 100 Gb mit dem DRAM-Stack kommunizieren, der auf demselben Siliziumstück in einem System-in-Package-Design verbunden ist. Dieser vielfältige Satz analoger, digitaler und gemischter Signalkomponenten, von denen einige auf verschiedenen Prozessknoten aufgebaut sind und möglicherweise auch vertikal mithilfe von 2,5D- oder 3D-Architekturen integriert sind, stellt eine noch größere Komplexität dar.

Diese Herausforderungen, die mit der Verifizierung dieser komplexen Designs verbunden sind, skalieren, da fortschrittliche Technologieprozessknoten erhöhte Parasiten, Prozessvariabilität und reduzierte Margen aufweisen. Dies führt zu mehr Simulationen mit längeren Laufzeiten bei höherer Genauigkeit, was sich auf die Gesamtzeit bis zum Ergebnis, die Qualität der Ergebnisse und die Kosten der Ergebnisse auswirkt.

Im Gespräch mit embedded.com sagte Hany Elhak, Group Director of Product Management bei Synopsys:„Um dieses Problem zu lösen, benötigen Sie ein System von Simulations-Engines mit einem einheitlichen Workflow. Es gibt derzeit keinen SPICE-Simulator, der mit allem fertig wird.“ Er sagte, es sei notwendig, sowohl mit der systemischen Komplexität als auch mit der Skalierungskomplexität von IC-Designs umzugehen.

Dies ist, was PrimeSim Continuum angehen soll. Es adressiert die systemische Komplexität solcher hyperkonvergenter Designs mit einem einheitlichen Workflow von Simulations-Engines in Sign-Off-Qualität, die auf analoge, Mixed-Signal-, RF- und kundenspezifische digitale Speicherdesigns abgestimmt sind. PrimeSim Continuum verwendet SPICE- und FastSPICE-Architekturen der nächsten Generation sowie heterogenes Computing, um die Nutzung von CPU- und GPU-Ressourcen zu optimieren und die Zeit bis zum Ergebnis und die Kosten der Ergebnisse zu verbessern.

Betrachten Sie als Beispiel für die Anforderungen an die Schaltungssimulation komplexer Designs das Aufkommen von Speicher mit hoher Bandbreite (HBM), der aus großen 3D-gestapelten DRAMs besteht, die mit dem SoC auf einem 3DIC oder in einem SiP integriert sind. Das HBM, das eine Hochgeschwindigkeits-Speicherschnittstelle für 3D-gestapeltes synchrones DRAM (SDRAM) bereitstellt, wird mit Hochleistungs-Grafikbeschleunigern, AI-ASICs und FPGAs in Hochleistungs-Rechenzentren und Netzwerkgeräten verwendet. In diesen Speicherchips sind mehrere DRAM-Dies vertikal mit einem Speichercontroller gestapelt, die alle durch Silizium-Durchkontaktierungen (TSVs) und Mikrohöcker auf einem Silizium-Interposer miteinander verbunden sind.

Designer müssen das gesamte in einem SiP vorhandene Speichersubsystem verifizieren, was eine komplexe mehrdimensionale Analyse auf Komponenten- und Subsystemebene erfordert. Es gibt schwierige und strengere Einschränkungen mit neuen Komplexitäten, die angegangen werden müssen, um Leistungs- und Leistungsziele zu erreichen. Tools zur Schaltungssimulation müssen Folgendes unterstützen:

- Analyse mehrerer Technologien und mehrerer Komponenten (Logik, Analog, Speicher, E/A)

- Verschiedene Arten von Analysen (analog, digital, Mixed-Signal)

- Große Kapazitäten für die Analyse auf Subsystem- und Chipebene

- Erweiterte Zuverlässigkeitsanalysen (elektrisch, thermisch, elektrothermisch, zeitlich)

- Signalintegrität

- Variabilitätsanalyse (Prozess, Struktur)

Da diese Designs auf fortschrittliche Technologieknoten skaliert werden, gibt es darüber hinaus eine erhebliche Zunahme an Simulationen, um sicherzustellen, dass das Design zuverlässig ist und die Ertragsziele erfüllt. Zu den Herausforderungen gehört beispielsweise die Messung der Signalintegrität, die über den Interposer analysiert werden muss. Probleme wie elektrothermische Belastung und größere Parasiten müssen angegangen werden, um die Chip-Zuverlässigkeit zu fördern, die eine Fertigung in großem Maßstab erfordert.

Aus der Sicht der Design Enablement stellt dies eine mehrdimensionale Herausforderung dar, die Arbeitsabläufe erfordert, die für Leistung, Leistung, Fläche (PPA) und Kostenkonvergenz optimiert sind.

Sassine Ghazi, Chief Operating Officer von Synopsys, sagte:„PrimeSim Continuum stellt einen revolutionären Durchbruch bei der Innovation von Schaltungssimulationen mit heterogener Rechenbeschleunigung auf GPU/CPU dar und setzt neue Maßstäbe für EDA-Lösungen. Unsere Kunden in allen Designsegmenten können jetzt von jahrelangen Investitionen in Forschung und Entwicklung, Innovation und Kundenzusammenarbeit mit PrimeSim Continuum-Technologien der nächsten Generation profitieren, die unsere moderne kundenspezifische Designplattform und das Verification Continuum ergänzen.“

Elhak sagte, dass Kioxia ein Beispiel für einen Early-Access-Kunden ist, der jeden Aspekt der neuen Lösung nutzt, wobei Flash-Speicher ein sehr komplexes System ist. Kioxia-Speicherdesigns integrieren komplexe Systeme, die aus Speicher-, Analog-, Mixed-Signal- und benutzerdefinierten digitalen Blöcken bestehen, die unterschiedliche Design- und Signoff-Technologien erfordern.

Shigeo (Jeff) Ohshima, Technology Executive für SSD-Anwendungstechnik bei Kioxia, sagte:„Ein konvergierter Workflow rund um eine gemeinsame Schaltungssimulationslösung ist erforderlich, um unsere Ziele hinsichtlich der Zeit bis zum Ergebnis und der Kosten der Ergebnisse zu erreichen. PrimeSim Continuums von Synopsys ist eine All-in-One-Lösung, die die besten SPICE- und FastSPICE-Technologien integriert und Genauigkeit, Geschwindigkeit und Kapazität für unsere komplexen Designs bietet. Die PrimeWave-Designumgebung bietet einen gemeinsamen Workflow für alle Simulationsdisziplinen und ermöglicht die Freigabe der Speicherdesigns von Kioxia. Effektive Zusammenarbeit und Zugang zu Technologien der nächsten Generation sind für unsere Partnerschaft mit Synopsys von grundlegender Bedeutung.“

PrimeSim Pro zur Leistungsbeschleunigung

Der Synopsys PrimeSim Pro-Simulator, ein Teil von PrimeSim Continuum, repräsentiert eine FastSPICE-Architektur der nächsten Generation für die schnelle und leistungsstarke Analyse moderner DRAM- und Flash-Speicherdesigns.

Kontinuierliche Technologieskalierung und Innovationen rund um die DRAM-Architektur haben zu größeren und komplexeren Speicherdesigns geführt, die eine höhere Simulationsleistung und -kapazität erfordern. Laut Jung Yun Choi, Corporate Vice President des Memory Design Technology Teams bei Samsung Electronics, sagte:„Synopsys PrimeSim Pro, die nächste Generation unseres Rekord-FastSPICE-Simulators, kann eine bis zu 5-fache Leistungsbeschleunigung auf unseren Full-Chip-Power-Delivery-Netzwerkdesigns liefern. Die Next-Gen-Architektur von PrimeSim Pro kann mit den Kapazitätsanforderungen unserer fortschrittlichen Speicherdesigns Schritt halten und ermöglicht es uns, unsere aggressiven Time-to-Result-Ziele zu erreichen.“

Nvidia der Partner und Kunde

Die Next-Generation-Architektur des Synopsys PrimeSim SPICE-Simulators verwendet die GPU-Technologie von Nvidia, um erhebliche Leistungsverbesserungen zu erzielen, die für die Durchführung umfassender Analysen für analoges und HF-Design erforderlich sind und gleichzeitig die Anforderungen an die Signoff-Genauigkeit erfüllen.

„Mit der Entwicklung moderner Rechenworkloads haben die Größe und Komplexität analoger Designs die Kapazität herkömmlicher Schaltungssimulatoren überschritten“, sagte Edward Lee, Vice President Mixed Signal Design bei Nvidia. „Durch die Verwendung von NVIDIA-GPUs kann PrimeSim SPICE die Schaltungssimulation beschleunigen und insbesondere die Signoff-Zeit analoger Blöcke von Tagen auf Stunden reduzieren.“

„Da die Designkomplexität mit fortschrittlichen Prozessknoten zunimmt, sind wir bestrebt, unsere gemeinsamen Kunden mit innovativen Simulationstechnologien zu unterstützen, um Verifikations- und Analysezyklen zu verkürzen“, sagte Jaehong Park, Executive Vice President und Head of Foundry Design Platform Development bei Samsung Electronics. „Synopsys PrimeSim Continuum mit seinem vereinheitlichten Workflow fortschrittlicher Simulations-Engines lieferte eine 10-fache Geschwindigkeit mit goldener SPICE-Genauigkeit durch heterogene Rechenbeschleunigung auf unserem neuesten 56-Gbit-Ethernet-Design, wodurch der Verifizierungsaufwand von Tagen auf Stunden reduziert wurde.“

Vereinheitlichter Workflow für Analyse und Freigabe

Die PrimeSim Continuum-Lösung integriert PrimeSim SPICE und PrimeSim Pro mit dem PrimeSim HSPICE-Simulator, der Goldstandard-Signoff-Referenz für Foundation IP und Signalintegrität, und dem PrimeSim XA-Simulator, der FastSPICE-Technologie für SRAM und Mixed-Signal-Verifikation. PrimeWave bietet ein nahtloses Erlebnis, indem es eine konsistente und flexible Umgebung für alle PrimeSim Continuum-Engines bereitstellt, die das Design-Setup, die Analyse und die Nachbearbeitung optimiert.

Eingebettet

- Computersimulation elektrischer Schaltungen

- Sensortypen mit ihren Schaltplänen

- Synopsys ermöglicht Multi-Die-Designs mit HBM3-IP und Verifizierung

- Sensirion:tragbare IoT-Plattform zur Arzneimittelverabreichung mit integriertem Flüssigkeitsflusssensor

- ST:8-Bit-MCUs mit Rich Analog und DMA im kostengünstigen SO-8-Paket

- Allegro:fortschrittliche Sensor-ICs für die Übertragungsgeschwindigkeit mit ASIL B-Zertifizierung

- TDK:vollständig integrierter eingebetteter Motorcontroller mit erweitertem Speicher für die Automobilindustrie

- Renesas:RX72M-MCUs mit EtherCAT-Unterstützung für industrielle Anwendungen

- Defense FPGA-Debüts mit Early Access

- Kontron:SMARC-sXAL4 (E2) Modul mit bis zu 8 GByte LPDDR4 Speicher down