Logische Signalspannungspegel

Eingangsspannungen für Logikgatter

Logikgatterschaltungen sind dafür ausgelegt, nur zwei Arten von Signalen ein- und auszugeben:„high“ (1) und „low“ (0), dargestellt durch eine variable Spannung:volle Versorgungsspannung für einen „high“-Zustand und Nullspannung für ein „niedriger“ Zustand. In einer perfekten Welt würden alle Logikschaltungssignale an diesen extremen Spannungsgrenzen existieren und niemals von ihnen abweichen (d.

In Wirklichkeit erreichen die logischen Signalspannungspegel jedoch aufgrund von Streuspannungsabfällen in der Transistorschaltung selten diese perfekten Grenzen, und daher müssen wir die Signalpegelbeschränkungen von Gate-Schaltungen verstehen, wenn sie versuchen, Signalspannungen zu interpretieren, die irgendwo zwischen<. liegen /em> volle Versorgungsspannung und Null.

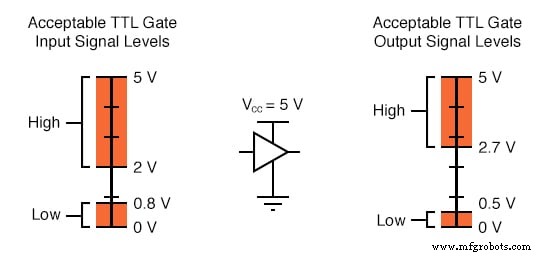

Spannungstoleranz der TTL-Gate-Eingänge

TTL-Gatter arbeiten mit einer Nennversorgungsspannung von 5 Volt, +/- 0,25 Volt. Idealerweise würde ein TTL-„High“-Signal genau 5,00 Volt betragen und ein TTL-„Low“-Signal genau 0,00 Volt.

Reale TTL-Gate-Schaltungen können jedoch solche perfekten Spannungspegel nicht ausgeben und sind dafür ausgelegt, „high“- und „low“-Signale zu akzeptieren, die erheblich von diesen Idealwerten abweichen.

„Akzeptable“ Eingangssignalspannungen reichen von 0 Volt bis 0,8 Volt für einen „niedrigen“ Logikzustand und 2 Volt bis 5 Volt für einen „hohen“ Logikzustand.

„Akzeptable“ Ausgangssignalspannungen (vom Gate-Hersteller über einen spezifizierten Lastbereich garantierte Spannungspegel) reichen von 0 Volt bis 0,5 Volt für einen „niedrigen“ Logikzustand und 2,7 Volt bis 5 Volt für einen „hohen“ Logikzustand :

Wenn ein Spannungssignal zwischen 0,8 Volt und 2 Volt an den Eingang eines TTL-Gates gesendet würde, würde das Gate keine sichere Antwort geben. Ein solches Signal würde als unsicher angesehen , und kein Hersteller von Logikgattern würde garantieren, wie seine Gatterschaltung ein solches Signal interpretieren würde.

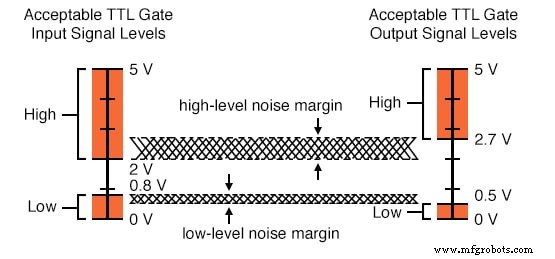

TTL-Rauschabstand

Wie Sie sehen, sind die tolerierbaren Bereiche für Ausgangssignalpegel enger als für Eingangssignalpegel, um sicherzustellen, dass jedes TTL-Gatter, das ein digitales Signal in den Eingang eines anderen TTL-Gatters ausgibt, akzeptable Spannungen zum empfangenden Gate überträgt. Der Unterschied zwischen den tolerierbaren Ausgangs- und Eingangsbereichen wird als Rauschabstand bezeichnet des Tores.

Bei TTL-Gates ist die Rauschspanne bei niedrigem Pegel die Differenz zwischen 0,8 Volt und 0,5 Volt (0,3 Volt), während die Rauschspanne bei hohem Pegel die Differenz zwischen 2,7 Volt und 2 Volt (0,7 Volt) ist. Einfach ausgedrückt ist die Rauschspanne der Spitzenwert der Stör- oder „Rauschen“-Spannung, die einem schwachen Gate-Ausgangsspannungssignal überlagert werden kann, bevor das empfangende Gate es falsch interpretieren könnte:

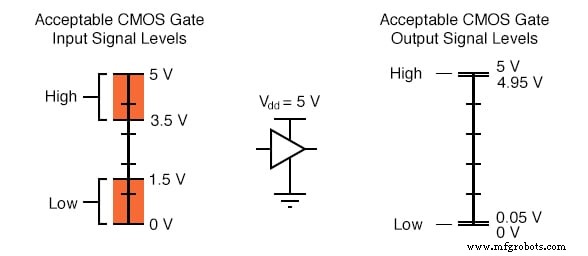

Spannungstoleranz der CMOS-Gate-Eingänge

CMOS-Gate-Schaltungen haben Eingangs- und Ausgangssignalspezifikationen, die sich stark von TTL unterscheiden. Für ein CMOS-Gate, das mit einer Versorgungsspannung von 5 Volt betrieben wird, reichen die akzeptablen Eingangssignalspannungen von 0 Volt bis 1,5 Volt für einen „niedrigen“ Logikzustand und 3,5 Volt bis 5 Volt für einen „hohen“ Logikzustand.

„Akzeptable“ Ausgangssignalspannungen (vom Gate-Hersteller über einen bestimmten Lastbereich garantierte Spannungspegel) reichen von 0 Volt bis 0,05 Volt für einen „niedrigen“ Logikzustand und 4,95 Volt bis 5 Volt für einen „hohen“ Logikzustand :

CMOS-Rauschabstand

Aus diesen Zahlen sollte ersichtlich sein, dass CMOS-Gate-Schaltungen weitaus größere Rauschspannen als TTL aufweisen:1,45 Volt für CMOS-Low-Level- und High-Level-Ränder, gegenüber maximal 0,7 Volt für TTL. Mit anderen Worten, CMOS-Schaltungen können mehr als das Doppelte der überlagerten „Rauschen“-Spannung auf ihren Eingangsleitungen tolerieren, bevor Fehler bei der Signalinterpretation auftreten.

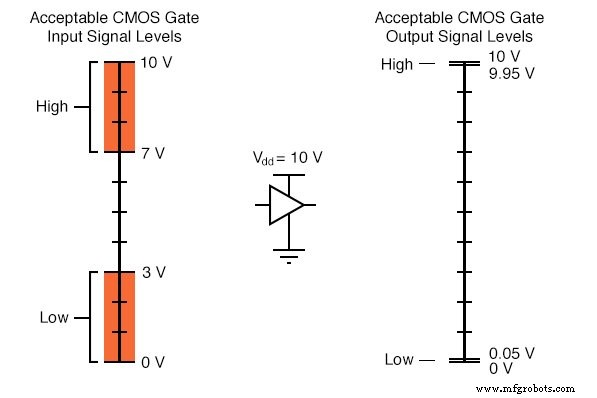

Rauschabstand bei höheren Betriebsspannungen

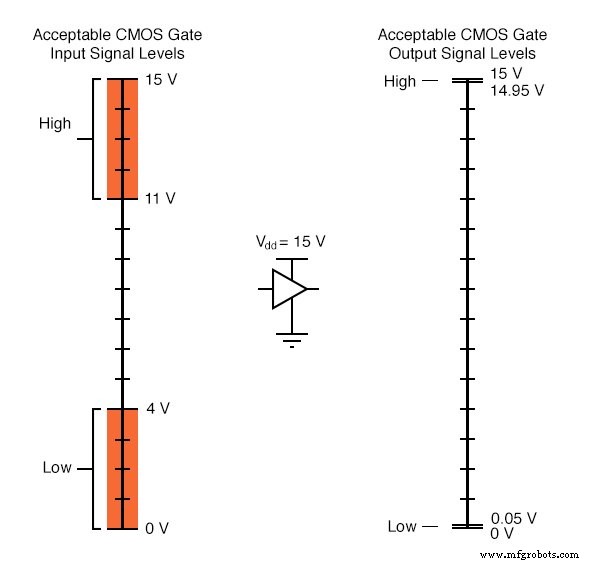

Die CMOS-Rauschgrenzen erweitern sich mit höheren Betriebsspannungen noch weiter. Im Gegensatz zu TTL, das auf eine Versorgungsspannung von 5 Volt beschränkt ist, kann CMOS mit Spannungen von bis zu 15 Volt (einige CMOS-Schaltungen bis zu 18 Volt) betrieben werden.

Hier sind die akzeptablen „High“- und „Low“-Zustände sowohl für den Eingang als auch für den Ausgang von integrierten CMOS-Schaltkreisen dargestellt, die mit 10 Volt bzw. 15 Volt arbeiten:

Die Spielräume für akzeptable „High“- und „Low“-Signale können größer sein als in den vorherigen Abbildungen gezeigt. Was gezeigt wird, stellt die Eingangssignalleistung im „Worst-Case“ dar, basierend auf den Herstellerspezifikationen. In der Praxis kann sich herausstellen, dass eine Gate-Schaltung „hohe“ Signale mit erheblich geringerer Spannung und „niedrige“ Signale mit erheblich höherer Spannung als die hier angegebenen toleriert.

Umgekehrt sind die gezeigten extrem kleinen Ausgangsmargen – die die Ausgangszustände für „High“- und „Low“-Signale bis auf 0,05 Volt der „Schienen“ der Stromversorgung garantieren – optimistisch. Solche „festen“ Ausgangsspannungspegel gelten nur für Bedingungen mit minimaler Belastung. Wenn das Gate einer Last einen erheblichen Strom zuführt oder ableitet, kann die Ausgangsspannung diese optimalen Werte aufgrund des internen Kanalwiderstands der letzten Ausgangs-MOSFETs des Gates nicht aufrechterhalten.

Spannungsschwellen

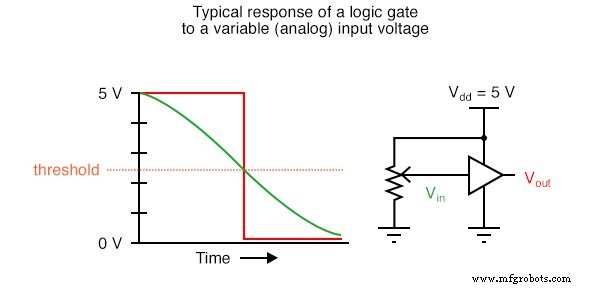

Innerhalb des „unsicheren“ Bereichs für jeden Gate-Eingang gibt es einen Abgrenzungspunkt, der den tatsächlichen „niedrigen“ Eingangssignalbereich des Gates von seinem tatsächlichen „hohen“ Eingangssignalbereich trennt. Das heißt, irgendwo zwischen dem niedrigsten „hohen“ Signalspannungspegel und dem höchsten „niedrigen“ Signalspannungspegel, der vom Gate-Hersteller garantiert wird, gibt es eine Schwellenspannung, bei der das Gate eigentlich wechselt die Interpretation eines Signals von „low“ oder „high“ oder umgekehrt. Für die meisten Gate-Schaltungen ist diese nicht spezifizierte Spannung ein einzelner Punkt:

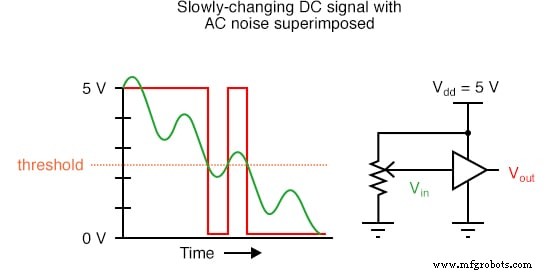

Eingänge mit Wechselstromrauschen

Bei Vorhandensein einer dem DC-Eingangssignal überlagerten AC-„Rauschen“-Spannung führt ein einzelner Schwellenwert, an dem das Gate seine Interpretation des Logikpegels ändert, zu einem fehlerhaften Ausgang:

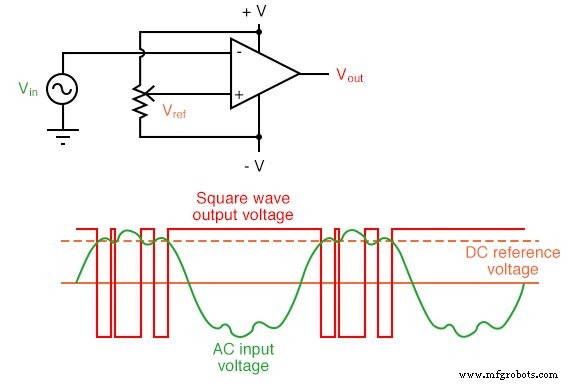

Wenn Ihnen dieses Szenario bekannt vorkommt, liegt es daran, dass Sie sich an ein ähnliches Problem mit (analogen) Spannungskomparator-Operationsverstärkerschaltungen erinnern. Bei einem einzigen Schwellenwert, an dem ein Eingang bewirkt, dass der Ausgang zwischen den Zuständen „high“ und „low“ wechselt, führt das Vorhandensein von signifikantem Rauschen zu unberechenbaren Änderungen im Ausgang:

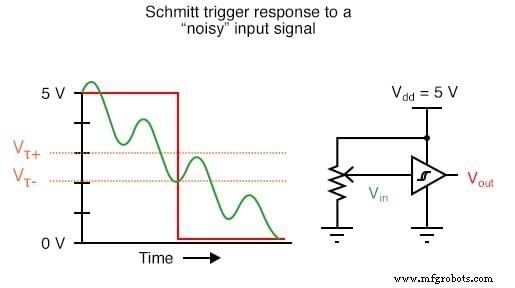

Schmittt-Trigger

Die Lösung für dieses Problem ist ein bisschen positiv Rückkopplung in die Verstärkerschaltung eingeführt. Bei einem Operationsverstärker geschieht dies, indem der Ausgang über einen Widerstand wieder mit dem nicht invertierenden (+) Eingang verbunden wird.

In einer Gate-Schaltung erfordert dies ein Neudesign der internen Gate-Schaltung, wodurch die Rückkopplung innerhalb des Gate-Gehäuses statt durch externe Verbindungen hergestellt wird. Ein so konstruiertes Tor wird als Schmitt-Trigger bezeichnet . Schmitt-Trigger interpretieren unterschiedliche Eingangsspannungen nach zwei Schwellenspannungen:a positiv Schwellenwert (VT+) und ein negativ verlaufender Schwelle (VT-):

Hysterese in Schmitt-Trigger-Gates

Schmitt-Trigger-Gates sind in schematischen Diagrammen durch das kleine eingezeichnete „Hysterese“-Symbol gekennzeichnet, das an die B-H-Kurve für ein ferromagnetisches Material erinnert. Hysterese, die durch positives Feedback innerhalb der Gate-Schaltung erzeugt wird, fügt der Leistung des Gates ein zusätzliches Maß an Rauschimmunität hinzu.

Schmitt-Trigger-Gates werden häufig in Anwendungen verwendet, bei denen Rauschen auf der (den) Eingangssignalleitung(en) erwartet wird und/oder bei denen ein fehlerhafter Ausgang die Systemleistung sehr beeinträchtigen würde.

Verwenden von TTL- und CMOS-Technologien im selben System

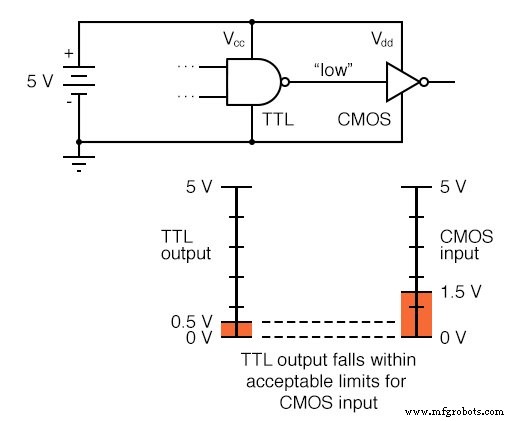

Die unterschiedlichen Spannungspegelanforderungen der TTL- und CMOS-Technologie stellen Probleme bereit, wenn die beiden Arten von Gates in demselben System verwendet werden. Obwohl der Betrieb von CMOS-Gates mit derselben 5,00-Volt-Versorgungsspannung, die von den TTL-Gates benötigt wird, kein Problem darstellt, sind die TTL-Ausgangsspannungspegel nicht mit den CMOS-Eingangsspannungsanforderungen kompatibel.

Beispiel einer TTL- und CMOS-Kombinationsschaltung

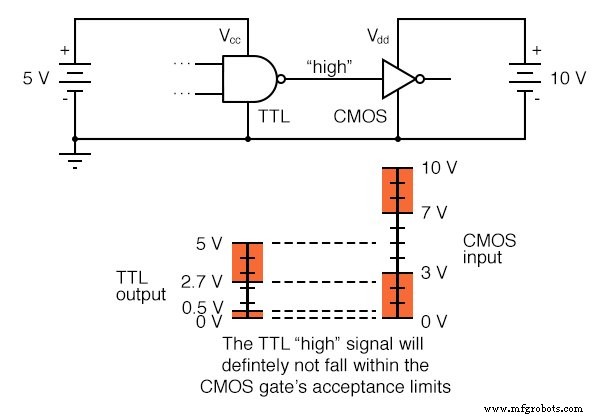

Nehmen wir zum Beispiel ein TTL-NAND-Gatter, das ein Signal in den Eingang eines CMOS-Inverter-Gatters ausgibt. Beide Gates werden von derselben 5,00-Volt-Versorgung gespeist (Vcc ). Wenn das TTL-Gate ein „Low“-Signal ausgibt (garantiert zwischen 0 Volt und 0,5 Volt), wird es vom Eingang des CMOS-Gates richtig als „Low“ interpretiert (erwartet eine Spannung zwischen 0 Volt und 1,5 Volt):

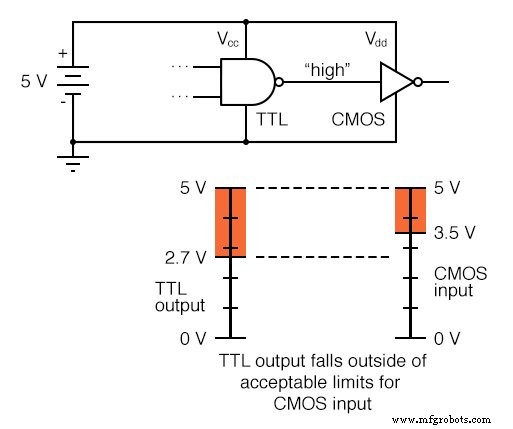

Wenn das TTL-Gate jedoch ein „High“-Signal ausgibt (garantiert zwischen 5 Volt und 2,7 Volt), könnte vom Eingang des CMOS-Gates nicht richtig als „high“ interpretiert werden (wobei eine Spannung zwischen 5 Volt und 3,5 Volt erwartet wird):

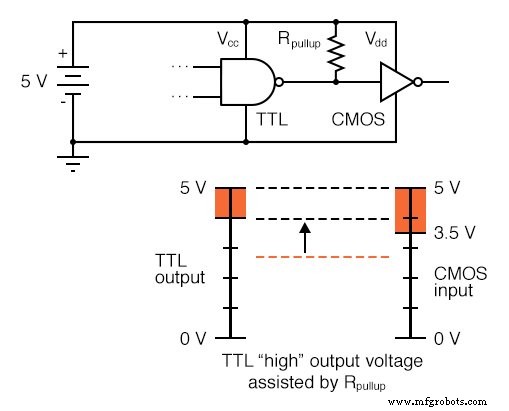

Aufgrund dieser Fehlanpassung ist es durchaus möglich, dass das TTL-Gatter ein gültiges „high“-Signal (gültig, d. h. gemäß den Standards für TTL) ausgibt, das im „unsicheren“ Bereich für den CMOS-Eingang liegt und möglicherweise ( fälschlicherweise) vom empfangenden Gate als „Low“ interpretiert. Eine einfache „Behebung“ für dieses Problem besteht darin, den „hohen“ Signalspannungspegel des TTL-Gates mit einem Pullup-Widerstand zu erhöhen:

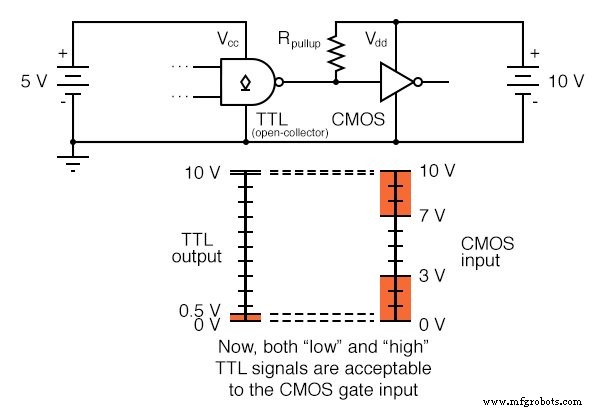

Etwas mehr als dies ist jedoch erforderlich, um einen TTL-Ausgang mit einem CMOS-Eingang zu verbinden, wenn das empfangende CMOS-Gate mit einer höheren Versorgungsspannung versorgt wird:

Verwendung eines Open-Collector-TTL-Gates mit einem CMOS-Gate

Es wird natürlich kein Problem damit geben, dass das CMOS-Gate den „low“-Ausgang des TTL-Gates interpretiert, aber ein „high“-Signal vom TTL-Gatter ist eine ganz andere Sache. Der garantierte Ausgangsspannungsbereich von 2,7 Volt bis 5 Volt vom TTL-Gate-Ausgang liegt bei weitem nicht im Bereich des akzeptablen Bereichs des CMOS-Gates von 7 Volt bis 10 Volt für ein „High“-Signal.

Wenn wir einen open-collector verwenden TTL-Gate anstelle eines Totem-Pole-Ausgangsgates, jedoch ein Pullup-Widerstand auf die 10 Volt Vdd Versorgungsschiene wird die „hohe“ Ausgangsspannung des TTL-Gates auf die volle Versorgungsspannung anheben, die das CMOS-Gate versorgt. Da ein Open-Collector-Gate nur Strom aufnehmen kann, keinen Quellenstrom, wird der Spannungspegel im „High“-Zustand vollständig durch die Stromversorgung bestimmt, an die der Pullup-Widerstand angeschlossen ist, wodurch das Mismatch-Problem sauber gelöst wird:

Probleme bei der Verwendung des CMOS-Ausgangs für einen TTL-Eingang

Aufgrund der hervorragenden Ausgangsspannungseigenschaften von CMOS-Gates ist es normalerweise kein Problem, einen CMOS-Ausgang an einen TTL-Eingang anzuschließen. Das einzige signifikante Problem ist die Strombelastung durch die TTL-Eingänge, da der CMOS-Ausgang im "Low"-Zustand für jeden der TTL-Eingänge Strom aufnehmen muss.

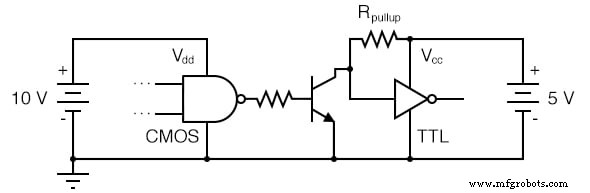

Wenn das fragliche CMOS-Gate von einer Spannungsquelle von mehr als 5 Volt (Vcc ) wird jedoch ein Problem auftreten. Der „high“-Ausgangszustand des CMOS-Gates, der größer als 5 Volt ist, überschreitet die akzeptablen Eingangsgrenzen des TTL-Gates für ein „high“-Signal.

Verwendung einer Wechselrichterschaltung mit offenem Kollektor

Eine Lösung für dieses Problem besteht darin, eine Inverterschaltung mit „offenem Kollektor“ zu erstellen, die einen diskreten NPN-Transistor verwendet und ihn verwendet, um die beiden Gates miteinander zu verbinden:

Der "RPullup ”-Widerstand ist optional, da TTL-Eingänge automatisch einen „High“-Zustand annehmen, wenn sie schwebend gelassen werden, was passiert, wenn der CMOS-Gate-Ausgang „Low“ ist und der Transistor sperrt. Eine sehr wichtige Konsequenz der Implementierung dieser Lösung ist natürlich die vom Transistor erzeugte logische Inversion:Wenn das CMOS-Gate ein „low“-Signal ausgibt, sieht das TTL-Gate einen „high“-Eingang; und wenn das CMOS-Gate ein „High“-Signal ausgibt, wird der Transistor gesättigt und das TTL-Gate sieht einen „Low“-Eingang. Solange diese Umkehrung im logischen Schema des Systems berücksichtigt wird, ist alles gut.

VERWANDTES ARBEITSBLATT:

-

Arbeitsblatt für digitale Logiksignale

Industrietechnik