Schieberegister:Serial-In, Serial-Out

Serial-In-, Serial-Out-Schieberegister verzögern Daten für jede Stufe um eine Taktzeit.

Sie speichern ein Datenbit für jedes Register. Ein Serial-In-, Serial-Out-Schieberegister kann eine Länge von einem bis 64 Bit haben, länger, wenn Register oder Pakete kaskadiert werden.

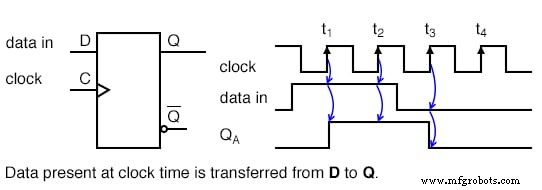

Unten ist ein einstufiges Schieberegister, das Daten empfängt, die nicht mit dem Registertakt synchronisiert sind.

Der „Dateneingang“ am D Pin vom Typ D FF (Flip-Flop) ändert den Pegel nicht, wenn die Uhr von niedrig zu hoch wechselt.

Möglicherweise möchten wir die Daten mit einem systemweiten Takt in einer Leiterplatte synchronisieren, um die Zuverlässigkeit einer digitalen Logikschaltung zu verbessern.

Der offensichtliche Punkt (im Vergleich zur Abbildung unten), der oben dargestellt ist, ist, dass alle „Daten in“ am D . vorhanden sind Pin vom Typ D FF wird zur Uhrzeit von D zum Ausgang Q übertragen.

Da unser Beispielschieberegister positive flankenempfindliche Speicherelemente verwendet, ist der Ausgang Q folgt dem D Eingang, wenn der Takt von niedrig auf hoch übergeht, wie durch die Aufwärtspfeile im obigen Diagramm gezeigt.

Es besteht kein Zweifel, welcher Logikpegel zur Taktzeit vorhanden ist, da die Daten lange vor und nach der Taktflanke stabil sind.

Dies ist bei mehrstufigen Schieberegistern selten der Fall. Aber dies war ein einfaches Beispiel für den Anfang. Wir befassen uns nur mit der positiven, niedrigen bis hohen Taktflanke.

Die fallende Flanke kann ignoriert werden. Q ist sehr leicht zu erkennen folge D zur Uhrzeit oben.

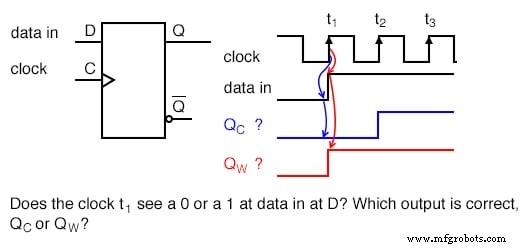

Vergleichen Sie dies mit dem Diagramm unten, in dem sich der "Dateneingang" mit der positiven Taktflanke zu ändern scheint.

Da sich „data in“ zur Uhrzeit t1 . zu ändern scheint oben, was bedeutet der Typ D FF zur Uhrzeit sehen?

Die kurze, stark vereinfachte Antwort lautet, dass die Daten angezeigt werden, die bei D . vorhanden waren vor der Uhr.

Das wird auf Q übertragen zur Uhrzeit t1 . Die richtige Wellenform ist QC . Um t1 Q geht auf Null, wenn es nicht bereits Null ist.

Das D Register sieht keine Eins bis zum Zeitpunkt t2 , zu welchem Zeitpunkt Q hoch wird.

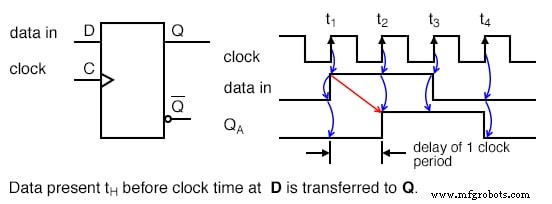

Da die Daten oben in D vorliegen wird auf Q getaktet zur Uhrzeit und Q kann sich bis zur nächsten Uhrzeit nicht ändern, das D FF verzögert Daten um eine Taktperiode, vorausgesetzt, die Daten sind bereits mit dem Takt synchronisiert. Die QA Wellenform ist die gleiche wie „Dateneingang“ mit einer Verzögerung von einer Taktperiode.

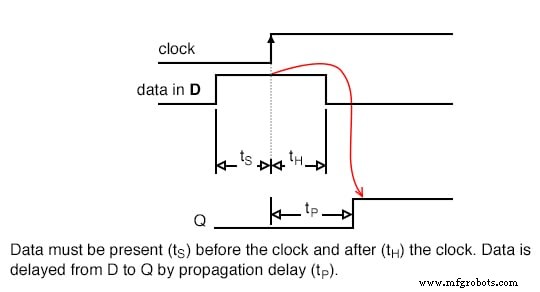

Ein genauerer Blick auf die Eingabe des Typs D Flip-Flop sieht zur Uhrzeit folgt.

Siehe die Abbildung unten. Da sich "data in" zur Uhrzeit (oben) zu ändern scheint, benötigen wir weitere Informationen, um zu bestimmen, was das D FF sieht.

Wenn der "Dateneingang" von einer anderen Schieberegisterstufe stammt, ein anderer gleicher Typ D FF, wir können einige Schlussfolgerungen basierend auf dem Datenblatt ziehen Informationen.

Hersteller digitaler Logik stellen Informationen zu ihren Teilen in Datenblättern zur Verfügung, die früher nur in einer Sammlung namens Datenbuch verfügbar waren .

Datenbücher sind noch verfügbar; Die Website des Herstellers ist jedoch die moderne Quelle.

Die folgenden Daten wurden dem CD4006b Datenblatt für den Betrieb an 5VDC entnommen , das als Beispiel zur Veranschaulichung des Timings dient. [*]

- tS =100ns

- tH =60ns

- tP =200-400ns typ/max

tS ist die Einrichtungszeit , müssen die Zeitdaten vor der Uhrzeit vorliegen. In diesem Fall müssen die Daten in D vorliegen 100ns vor der Uhr.

Darüber hinaus müssen die Daten für die Haltezeit aufbewahrt werden tH =60ns nach der Uhrzeit. Diese beiden Bedingungen müssen erfüllt sein, um zuverlässig Daten von D zu takten zu Q des Flip-Flops.

Es ist kein Problem, die Setup-Zeit von 60 ns einzuhalten, da die Daten bei D vorliegen für die gesamte vorherige Taktperiode da war, wenn es von einer anderen Schieberegisterstufe kommt.

Bei einer Taktfrequenz von 1 MHz beträgt die Taktperiode beispielsweise 1000 µs, viel Zeit.

Daten werden tatsächlich für 1000 µs vor dem Takt vorhanden sein, was viel größer ist als das erforderliche Minimum tS von 60ns.

Die Haltezeit tH =60ns ist erfüllt, weil D mit Q einer anderen Stufe verbunden ist, sich nicht schneller ändern kann als die Ausbreitungsverzögerung der vorherigen Stufe tP =200ns.

Die Haltezeit wird so lange eingehalten, wie die Ausbreitungsverzögerung des vorherigen D FF ist größer als die Haltezeit.

Daten bei D angetrieben von einer anderen Stufe Q ändert sich beim CD4006b nicht schneller als 200 ns.

Zusammenfassend:Ausgabe Q folgt Eingang D fast zur Taktzeit, wenn Flip-Flops in ein mehrstufiges Schieberegister kaskadiert werden.

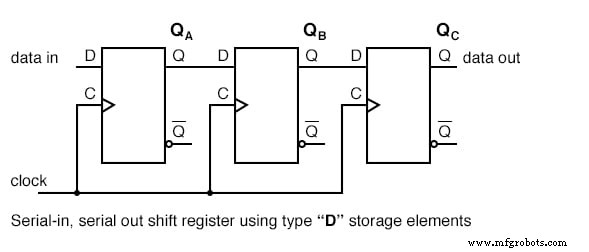

Drei Typ D Flip-Flops sind von Q nach D kaskadiert und die Takte parallel, um oben ein dreistufiges Schieberegister zu bilden.

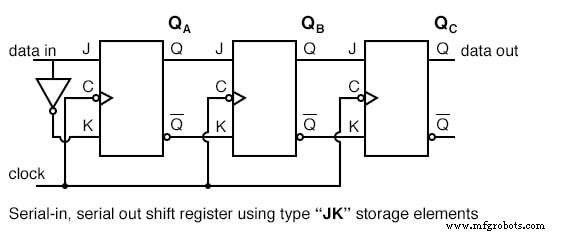

Geben Sie JK ein Flip-Flops kaskadierte Q zu J, Q’ zu K mit parallelen Takten, um eine alternative Form des obigen Schieberegisters zu erhalten.

Ein Serial-In/Serial-Out-Schieberegister hat einen Takteingang, einen Dateneingang und einen Datenausgang von der letzten Stufe.

Im Allgemeinen sind die anderen Stufenausgänge nicht verfügbar. Andernfalls wäre es ein Schieberegister mit seriellem Eingang und parallelem Ausgang.

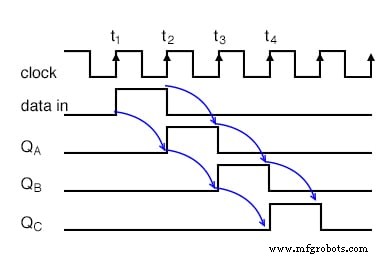

Die folgenden Wellenformen gelten für eine der beiden vorherigen Versionen des Seriell-In-, Seriell-Out-Schieberegisters.

Die drei Pfeilpaare zeigen, dass ein dreistufiges Schieberegister vorübergehend 3 Datenbits speichert und diese vom Eingang zum Ausgang um drei Taktperioden verzögert.

Zur Uhrzeit t1 ein "Dateneingang" von 0 wird von D getaktet zu Q aller drei Stufen. Insbesondere D der Stufe A sieht eine logische 0 , die auf QA . getaktet ist wo es bleibt bis zum Zeitpunkt t2 .

Zur Uhrzeit t2 ein "Dateneingang" von 1 wird von D getaktet zu QA . Auf den Stufen B und C , eine 0 , gespeist von vorhergehenden Stufen wird auf QB . getaktet und QC .

Zur Uhrzeit t3 ein "Dateneingang" von 0 wird von D getaktet zu QA . QA wird niedrig und bleibt für die verbleibenden Takte niedrig, da "Daten ein" 0 ist . QB geht hoch bei t3 aufgrund einer 1 aus der vorherigen Stufe. QC ist nach t3 . immer noch niedrig aufgrund eines Tiefstands aus der vorherigen Phase.

QC geht schließlich hoch bei Takt t4 aufgrund des hohen Fed an D von der vorherigen Stufe QB . Alle früheren Phasen haben 0 s in sie verschoben. Und nach dem nächsten Taktimpuls bei t5 , alle Logik 1 s werden verschoben und durch 0 ersetzt s

Serial-In/Serial-Out-Geräte

Wir werden uns die folgenden Teile, die als integrierte Schaltkreise erhältlich sind, mit freundlicher Genehmigung von Texas Instruments genauer ansehen.

Für vollständige Gerätedatenblätter folgen Sie den Links.

- CD4006b 18-Bit Seriell-In/Seriell-Out-Schieberegister

- CD4031b 64-Bit-Serial-In/Serial-Out-Schieberegister

- CD4517b Dual 64-Bit Seriell-In/Seriell-Out Schieberegister

Die folgenden Serial-In/Serial-Out-Schieberegister sind CMOS der Serie 4000 (Complementary Metal Oxide Semiconductor)-Familienteile.

Als solche akzeptieren sie ein VDD , positive Stromversorgung von 3-Volt bis 15-Volt. Die VSS Pin ist geerdet.

Die maximale Frequenz des Schiebetakts, die mit VDD . variiert , ist ein paar Megahertz.

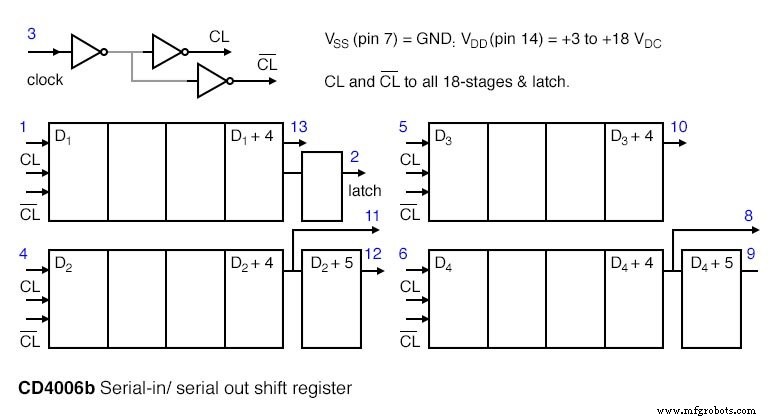

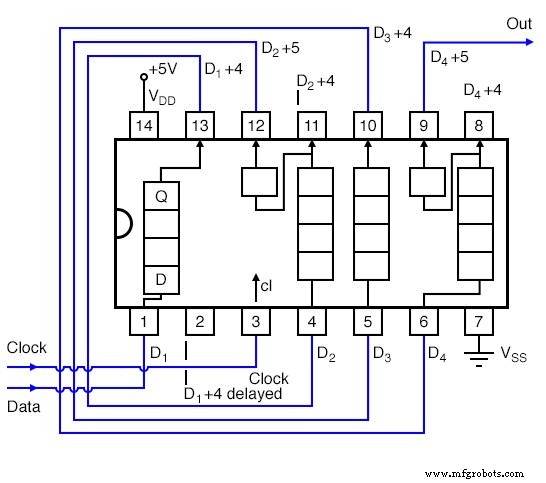

Der 18-Bit-CD4006b besteht aus zwei Stufen von 4 Bit und zwei weiteren Stufen von 5 Bit mit einem Ausgangsabgriff bei 4 Bit.

Somit könnten die 5-Bit-Stufen als 4-Bit-Schieberegister verwendet werden.

Um ein volles 18-Bit-Schieberegister zu erhalten, muss der Ausgang eines Schieberegisters zum Eingang eines anderen kaskadiert werden usw., bis alle Stufen ein einzelnes Schieberegister bilden, wie unten gezeigt.

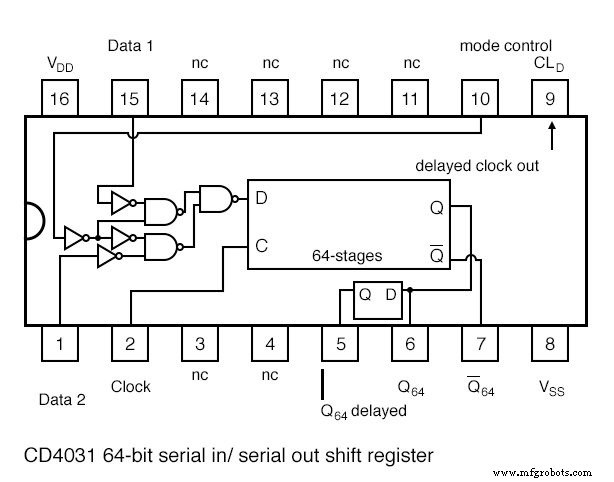

Ein CD4031 64-Bit Serial-In/Serial-Out-Schieberegister ist unten abgebildet.

Mehrere Pins sind nicht verbunden (nc). Sowohl Q als auch Q’ sind ab der 64. Stufe verfügbar, eigentlich Q64 und Q'64 .

Es gibt auch ein Q64 "verzögert" von einer Halbstufe, die um einen halben Taktzyklus verzögert ist. Ein Hauptmerkmal ist ein Datenselektor, der sich am Dateneingang des Schieberegisters befindet.

Die „Modussteuerung“ wählt zwischen zwei Eingängen:Daten 1 und Daten 2. Wenn „Modussteuerung“ hoch ist, werden Daten aus „Daten 2“ für die Eingabe in das Schieberegister ausgewählt.

Im Fall von "mode control" auf logisch Low wird "data 1" ausgewählt. Beispiele dafür sind in den beiden folgenden Abbildungen dargestellt.

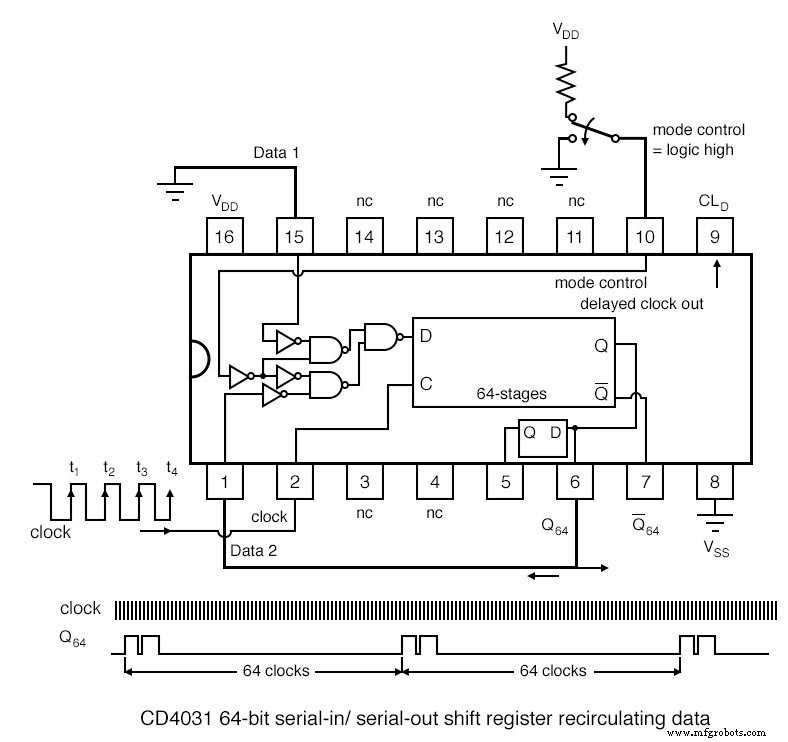

Die „Daten 2“ oben sind mit dem Q64 . verbunden Ausgang des Schieberegisters. Bei hoher „Modussteuerung“ ist der Q64 Ausgang wird zurück zum Shifter-Dateneingang D geleitet.

Die Daten werden rezirkuliert vom Ausgang zum Eingang. Die Daten werden alle 64 Taktimpulse wie oben gezeigt wiederholt.

Es stellt sich die Frage, wie dieses Datenmuster überhaupt in das Schieberegister gelangt ist?

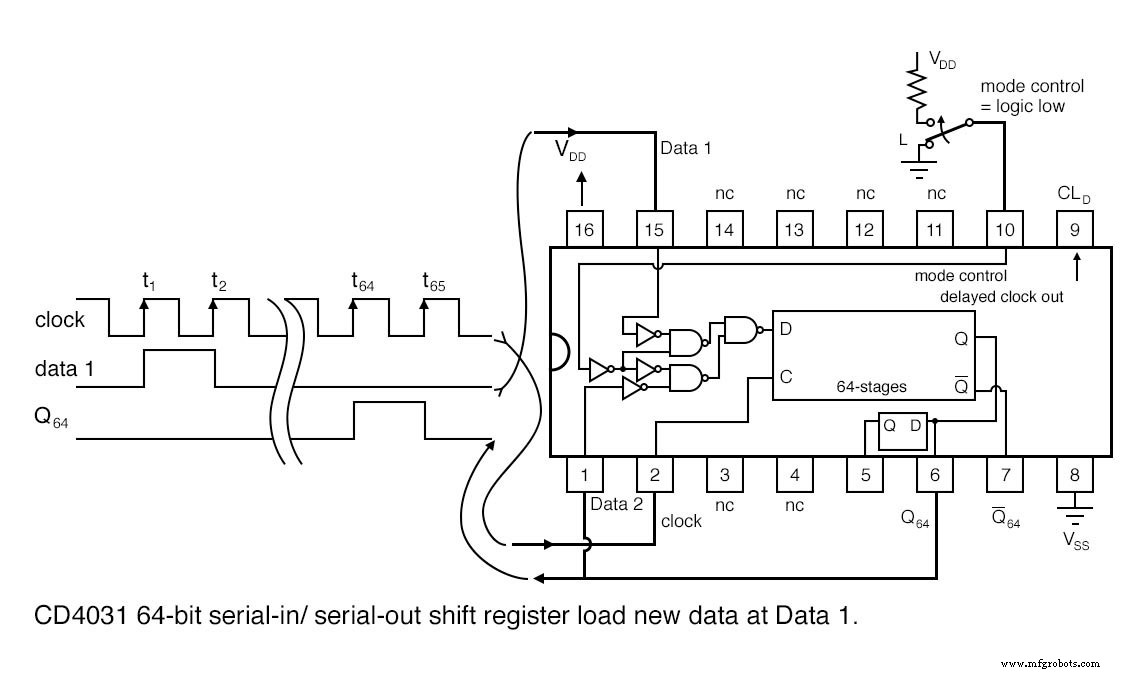

Bei „mode control“ niedrig wird der CD4031 „data 1“ für die Eingabe in den Shifter ausgewählt.

Die Ausgabe, Q64 , wird nicht rezirkuliert, weil das untere Datenauswahl-Gate deaktiviert . ist .

Mit deaktiviert meinen wir, dass die logisch niedrige „Modusauswahl“ am unteren NAND-Gatter zweimal invertiert auf ein niedriges NAND-Gatter verhindert, dass jedes Signal am unteren Pin (Daten 2) an den Gate-Ausgang weitergegeben wird.

Daher ist es deaktiviert.

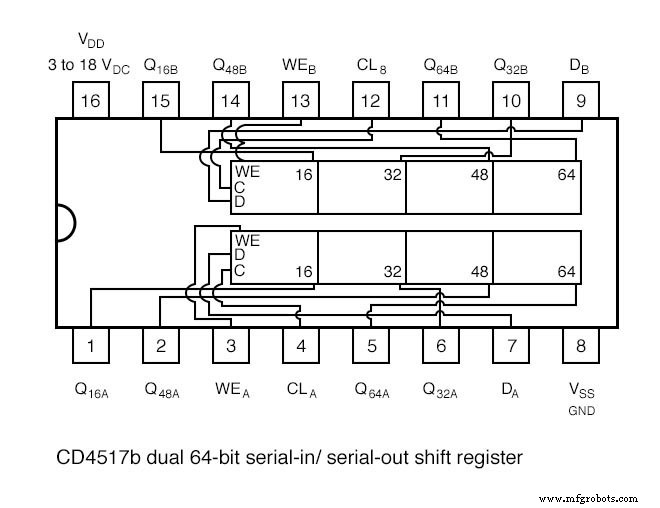

Ein CD4517b Dual 64-Bit-Schieberegister ist oben gezeigt. Beachten Sie die Taps in der 16., 32. und 48. Stufe.

Das bedeutet, dass Schieberegister dieser Länge von einem der 64-Bit-Schieber konfiguriert werden können.

Natürlich können die 64-Bit-Schieber kaskadiert werden, um ein 80-Bit-, 96-Bit-, 112-Bit- oder 128-Bit-Schieberegister zu ergeben.

Die Uhr CLA und CLB müssen beim Kaskadieren der beiden Schalthebel parallel geschaltet werden. WIRB und WIRB sind für normale Schaltvorgänge geerdet.

Die Dateneingaben zu den Schieberegistern A und B sind DA und DB bzw.

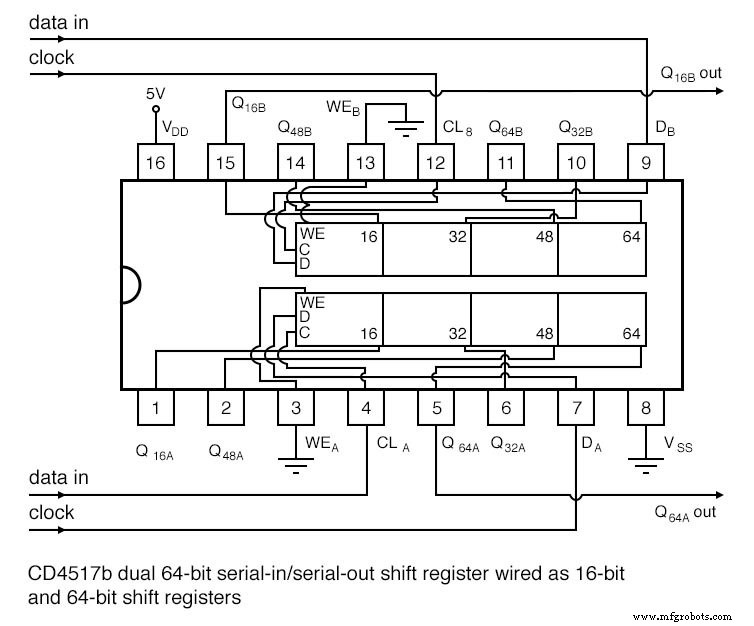

Angenommen, wir benötigen ein 16-Bit-Schieberegister.

Kann das mit dem CD4517b konfiguriert werden? Wie wäre es mit einem 64-Schieberegister aus dem gleichen Teil?

Oben zeigen wir einen CD4517b, der als 16-Bit-Schieberegister für Abschnitt B verdrahtet ist.

Die Uhr für Abschnitt B ist CLB . Die Daten werden bei CLB . eingetaktet . Und die um 16 Takte verzögerten Daten werden von Q16B . abgegriffen . WIRB , die Schreibfreigabe, ist geerdet.

Oben zeigen wir auch den gleichen CD4517b, der als 64-Bit-Schieberegister für den unabhängigen Abschnitt A verdrahtet ist.

Die Uhr für Abschnitt A ist CLA . Die Daten werden bei CLA . eingegeben . Die um 64-Takt-Impulse verzögerten Daten werden von Q64A . abgeholt . WIRA , die Schreibfreigabe für Abschnitt A, ist geerdet.

VERWANDTE ARBEITSBLÄTTER:

- Schichtregister Arbeitsblatt

Industrietechnik