Schieberegister:Parallel-in, Serial-out (PISO)-Konvertierung

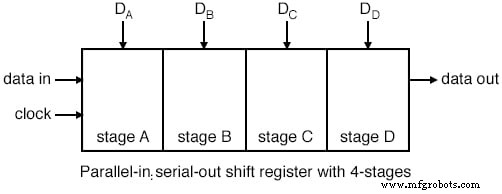

Parallel-In/Serial-Out-Schieberegister tun alles, was die vorherigen Serial-In/Serial-Out-Schieberegister tun und geben gleichzeitig Daten in alle Stufen ein.

Das Parallel-In/Serial-Out-Schieberegister speichert Daten, verschiebt sie Takt für Takt und verzögert sie um die Anzahl der Stufen mal der Taktperiode.

Darüber hinaus bedeutet Parallel-In/Serial-Out wirklich, dass wir Daten parallel in alle Stufen laden können, bevor überhaupt eine Verschiebung beginnt.

Dies ist eine Möglichkeit, Daten aus einem Parallel . zu konvertieren zu einer Serien formatieren Format. Mit parallelem Format meinen wir, dass die Datenbits gleichzeitig auf einzelnen Drähten vorhanden sind, eines für jedes Datenbit, wie unten gezeigt.

Mit seriellem Format meinen wir, dass die Datenbits zeitlich sequentiell auf einem einzelnen Draht oder Stromkreis präsentiert werden, wie im Fall des „Datenausgangs“ im Blockdiagramm unten.

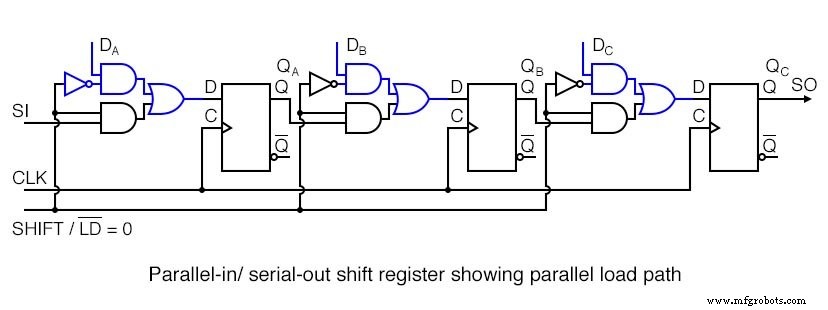

Im Folgenden sehen wir uns die internen Details eines 3-stufigen Parallel-In/Serial-Out-Schieberegisters genauer an.

Eine Stufe besteht aus einem Typ D Flip-Flop zum Speichern und ein UND-ODER-Selektor, um zu bestimmen, ob Daten parallel geladen werden oder gespeicherte Daten nach rechts verschieben.

Im Allgemeinen werden diese Elemente für die erforderliche Anzahl von Stufen repliziert. Aus Platzgründen zeigen wir drei Stufen.

Vier, acht oder sechzehn Bits sind für Realteile normal.

Oben zeigen wir den parallelen Lastpfad, wenn SHIFT/LD’ logisch niedrig ist. Die oberen NAND-Gatter, die DA . bedienen DB DC aktiviert sind und Daten an die D-Eingänge vom Typ D passing übergeben Flip-Flops QA QB DC bzw.

Bei der nächsten positiven Taktflanke werden die Daten von D nach Q der drei FFs getaktet. Drei Datenbits werden in QA . geladen QB DC gleichzeitig.

Die gerade beschriebene Art der parallelen Last, bei der die Daten in einem Takt geladen werden, wird als synchrone Last bezeichnet weil das Laden der Daten mit der Uhr synchronisiert ist.

Dies muss von asynchronem Laden unterschieden werden wo das Laden durch die voreingestellten und klaren Pins der Flip-Flops gesteuert wird, die keine Uhr benötigen.

Innerhalb eines einzelnen Geräts wird nur eine dieser Lademethoden verwendet, wobei die synchrone Last bei neueren Geräten häufiger vorkommt.

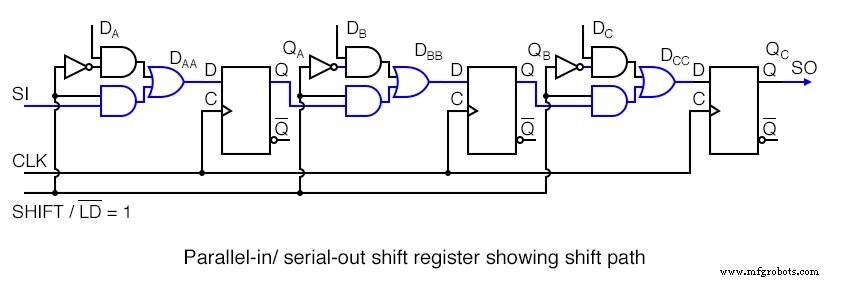

Der Schiebepfad ist oben gezeigt, wenn SHIFT/LD’ logisch hoch ist. Die unteren UND-Gatter der Paare, die das ODER-Gatter speisen, werden aktiviert, was uns eine Schieberegisterverbindung von SI zu DA . gibt , QA nach DB , QB nach DC , QC zu SO. Taktimpulse bewirken, dass Daten bei aufeinanderfolgenden Impulsen nach rechts nach SO verschoben werden.

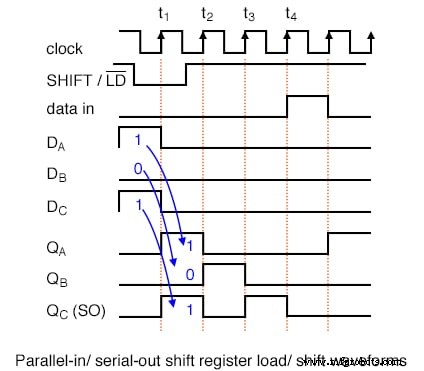

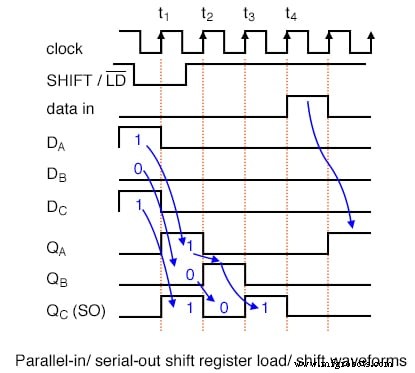

Die folgenden Wellenformen zeigen sowohl das parallele Laden von drei Datenbits als auch das serielle Verschieben dieser Daten. Parallele Daten bei DA DB DC wird bei SO in serielle Daten umgewandelt.

Was wir zuvor mit Worten für paralleles Laden und Verschieben beschrieben haben, ist jetzt oben als Wellenformen aufgeführt.

Als Beispiel präsentieren wir 101 an die parallelen Eingänge DAA DBB DCC . Als nächstes wird SHIFT/LD’ niedrig, was das Laden von Daten im Gegensatz zum Verschieben von Daten ermöglicht.

Aufgrund von Setup- und Hold-Anforderungen muss er kurz vor und nach dem Taktimpuls niedrig sein. Es ist erheblich breiter als es sein muss.

Mit synchroner Logik ist es jedoch praktisch, sie breit zu machen. Wir hätten das aktive Low SHIFT/LD’ fast zwei Takte breit machen können, fast einen Takt vor t1 . niedrig und wieder hoch kurz vor t3 .

Der wichtige Faktor ist, dass er um die Uhrzeit t1 . niedrig sein muss um das parallele Laden der Daten durch die Uhr zu ermöglichen.

Beachten Sie, dass bei t1 die Daten 101 bei DA DB DC wird von D nach Q der Flip-Flops getaktet, wie bei QA . gezeigt QB QC zum Zeitpunkt t1 .

Dies ist das parallele Laden der Daten synchron zum Takt.

Nachdem die Daten jetzt geladen sind, können wir sie verschieben, vorausgesetzt, dass SHIFT/LD’ hoch ist, um das Verschieben zu ermöglichen, was vor t2 . der Fall ist .

Um t2 die Daten 0 bei QC wird aus SO herausgeschoben, was dem QC . entspricht Wellenform. Es wird entweder in einen anderen integrierten Schaltkreis verschoben oder geht verloren, wenn nichts mit SO verbunden ist.

Die Daten bei QB , eine 0 wird auf QC . verschoben . Die 1 bei QA wird in QB . verschoben . Mit "Daten in" eine 0 , QA wird 0 . Nach t2 , QA QB QC =010 .

Nach t3 , QA QB QC =001 . Diese 1 , die ursprünglich bei QA . vorhanden war nach t1 , ist jetzt bei SO und QC . vorhanden .

Das letzte Datenbit wird zu einer externen integrierten Schaltung herausgeschoben, falls vorhanden. Nach t4 alle Daten vom parallelen Laden sind weg.

Um Uhr t5 wir zeigen die Verschiebung von Daten 1 vorhanden am SI, serieller Eingang.

F:Warum SI- und SO-Pins an einem Schieberegister bereitstellen?

A:Diese Verbindungen ermöglichen es uns, Schieberegisterstufen zu kaskadieren, um größere Schieber bereitzustellen, als in einem einzelnen IC-Gehäuse (Integrated Circuit) verfügbar sind. Sie ermöglichen auch serielle Verbindungen zu und von anderen ICs wie Mikroprozessoren.

Werfen wir einen genaueren Blick auf Parallel-In/Serial-Out-Schieberegister, die als integrierte Schaltungen mit freundlicher Genehmigung von Texas Instruments erhältlich sind.

Für vollständige Gerätedatenblätter folgen Sie diesen Links.

Parallel-in/serial-out-Geräte

- SN74ALS166 Parallel-In/Serial-Out 8-Bit-Schieberegister, synchrones Laden

- SN74ALS165 Parallel-In/Serial-Out 8-Bit-Schieberegister, asynchrones Laden

- CD4014B Parallel-In/Serial-Out 8-Bit-Schieberegister, synchrones Laden

- SN74LS647 Parallel-In/Serial-Out 16-Bit-Schieberegister, synchrones Laden

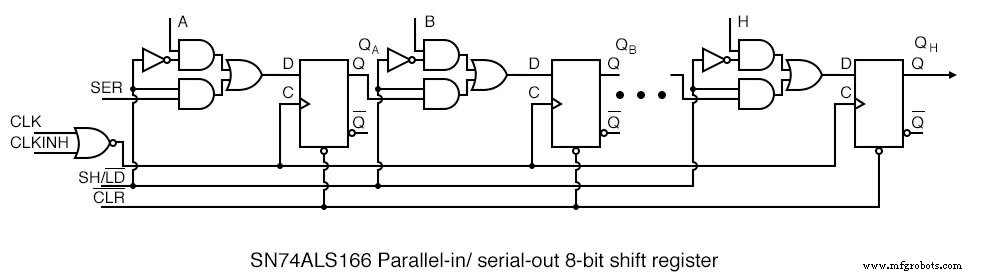

Der oben gezeigte SN74ALS166 ist die genaueste Übereinstimmung eines tatsächlichen Teils mit den vorherigen Parallel-In/Serial-Out-Shifter-Zahlen.

Beachten wir die geringfügigen Änderungen an unserer obigen Abbildung. Zunächst einmal gibt es 8-Stufen. Wir zeigen nur drei.

Alle 8-Stufen sind im Datenblatt unter dem obigen Link aufgeführt. Der Hersteller beschriftet die Dateneingänge A, B, C usw. mit H.

Der SHIFT/LOAD-Regler heißt SH/LD’. Es ist von unserer vorherigen Terminologie abgekürzt, funktioniert aber gleich:parallele Last wenn niedrig, Verschiebung wenn hoch.

Der Shift-Eingang (serielle Daten in) ist SER beim ALS166 anstelle von SI. Der Takt CLK wird durch ein Sperrsignal CLKINH gesteuert.

Wenn CLKINH hoch ist, wird der Takt gesperrt oder deaktiviert. Ansonsten ist dieser „reale Teil“ derselbe, den wir uns im Detail angesehen haben.

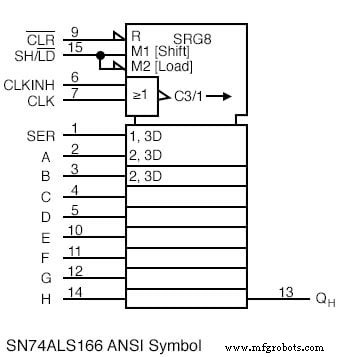

Oben ist das ANSI-Symbol (American National Standards Institute) für den SN74ALS166 wie im Datenblatt angegeben.

Sobald wir wissen, wie das Teil funktioniert, ist es praktisch, die Details in einem Symbol auszublenden. Es gibt viele allgemeine Formen von Symbolen.

Der Vorteil des ANSI-Symbols besteht darin, dass die Etiketten Hinweise auf die Funktionsweise des Teils geben.

Der große gekerbte Block oben auf dem '74ASL166 ist der Steuerabschnitt des ANSI-Symbols. Es gibt einen Reset, der von R angeklagt wurde .

Es gibt drei Steuersignale:M1 (Umschalt), M2 (Laden) und C3/1 (Pfeil) (gesperrte Uhr). Die Uhr hat zwei Funktionen.

Zuerst C3 zum Verschieben von parallelen Daten überall dort, wo ein Präfix von 3 erscheint. Zweitens, wann immer M1 wird geltend gemacht, wie durch die 1 . angezeigt von C3/1 (Pfeil) , werden die Daten wie durch den nach rechts zeigenden Pfeil angezeigt verschoben.

Der Schrägstrich (/) ist ein Trennzeichen zwischen diesen beiden Funktionen. Die 8-Schicht-Stufen, wie durch den Titel SRG8 angezeigt , werden durch die externen Eingaben A, B, C, identifiziert zu H .

Das interne 2, 3D zeigt an, dass Daten, D , wird gesteuert von M2 [Laden] und C3 Uhr. In diesem Fall können wir schließen, dass die parallelen Daten synchron mit der Uhr geladen werden C3 .

Die Oberstufe bei A ist ein breiterer Block als die anderen, um die Eingabe SER aufzunehmen .

Die Legende 1, 3D impliziert, dass SER wird gesteuert von M1 [Shift] und C3 Uhr. Daher erwarten wir, dass wir Daten bei SER einstempeln beim Verschieben im Gegensatz zum Parallelladen.

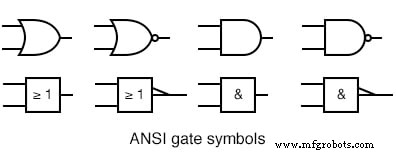

Das ANSI/IEEE-Basistor rechteckige Symbole sind oben zum Vergleich mit den bekannteren Formsymbolen . angegeben damit wir die Bedeutung der Symbolik entschlüsseln können, die mit dem CLKIN verbunden ist H und CLK Pins auf dem vorherigen ANSI SN74ALS166 Symbol.

Der CLK und CLKINH füttern ein ODER Gate auf dem SN74ALS166 ANSI-Symbol. ODER wird angezeigt durch => auf dem rechteckigen Einschubsymbol.

Das lange Dreieck am Ausgang zeigt eine Uhr an. Wenn es eine Blase mit dem Pfeil gegeben hätte, hätte dies eine Verschiebung bei der negativen Taktflanke (hoch nach niedrig) angezeigt.

Da es keine Blase mit dem Taktpfeil gibt, verschiebt sich das Register auf der positiven Taktflanke (von Low nach High).

Der lange Pfeil nach der Legende C3/1 nach rechts zeigen bedeutet nach rechts verschieben, was das Symbol nach unten ist.

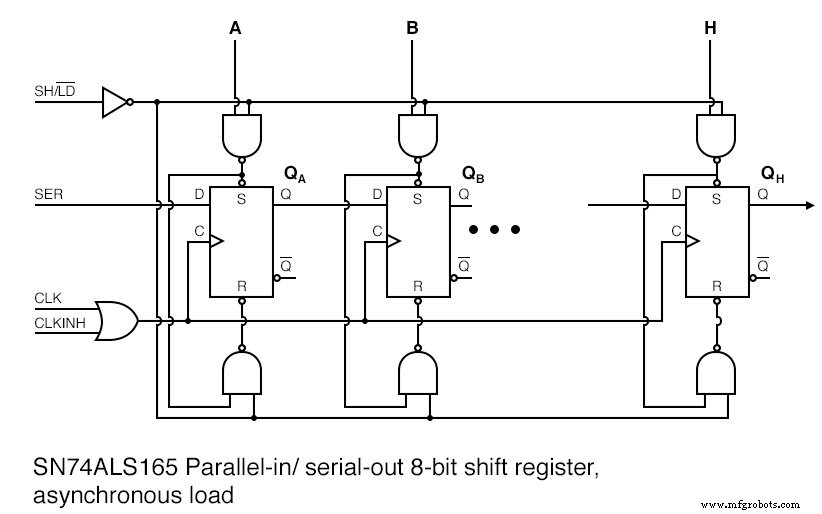

Ein Teil der internen Logik des SN74ALS165 Parallel-In/Serial-Out, asynchrones Lade-Schieberegister ist aus dem obigen Datenblatt reproduziert.

Das vollständige Diagramm finden Sie unter dem Link am Anfang dieses Abschnitts. Wir haben uns bisher nicht mit dem asynchronen Laden von Daten befasst.

Das Laden erfolgt zunächst durch Anlegen entsprechender Signale an das Set (voreingestellt) und Zurücksetzen (löschen) Eingänge der Flip-Flops.

Der obere NAND Tore füttern den Satz Pins der FFs und kaskadiert auch in den unteren NAND Gate-Fütterung des Reset Pins der FFs.

Der untere NAND Gate invertiert das Signal beim Gehen vom Set an das Zurücksetzen anheften Pin.

Zuerst SH/LD’ muss Low gezogen werden um das obere und untere NAND zu aktivieren Tore.

Wenn SH/LD’ waren logisch hoch stattdessen speist der Wechselrichter ein logisches low an alle NAND Tore würden ein High erzwingen aus, das "aktive Low" Set freigeben und Zurücksetzen Pins aller FFs.

Es gäbe keine Möglichkeit die FFs zu laden.

Mit SH/LD’ Niedrig gehalten , können wir beispielsweise ein Daten 1 . füttern zum parallelen Eingang A , die am oberen NAND zu einer Null invertiert wird Gate-Ausgang, Einstellung FF QA zu einer 1 .

Die 0 am Set Pin wird dem unteren NAND zugeführt Gate, wo es in eine 1 invertiert ist , Freigabe des Resets Pin von QA .

Somit ist ein Daten A=1 setzt QA =1 . Da nichts davon die Uhr erfordert, erfolgt das Laden asynchron in Bezug auf die Uhr.

Wir verwenden ein asynchrones Ladeschieberegister, wenn wir nicht auf einen Takt warten können, um Daten parallel zu laden, oder wenn es unpraktisch ist, einen einzelnen Taktimpuls zu erzeugen.

Der einzige Unterschied beim Einspeisen von Daten 0 zum parallelen Eingang A ist, dass es in eine 1 . invertiert wird aus dem oberen Tor, das Set loslässt .

Diese 1 bei Set ist invertiert zu einer 0 am unteren Tor, Reset ziehen zu einem Niedrig , wodurch QA . zurückgesetzt wird =0 .

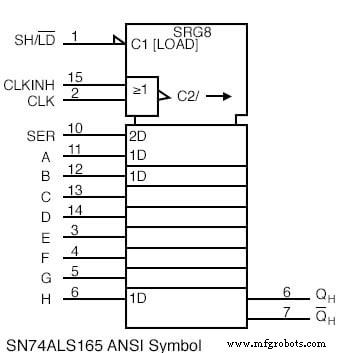

Das ANSI-Symbol für das SN74ALS166 oben hat zwei interne Kontrollen C1 [LOAD] und C2 Uhr vom ODER Funktion von (CLKINH, CLK ).

SRG8 sagt 8-Stufen-Schaltung. Der Pfeil nach C2 zeigt das Verschieben nach rechts oder unten an. SER Eingang ist eine Funktion der Uhr, wie durch das interne Label 2D angezeigt .

Die parallelen Dateneingänge A, B, C zu H sind eine Funktion von C1 [LOAD], angezeigt durch internes Label 1D .

C1 wird geltend gemacht, wenn sh/LD’ =0 durch den Halbpfeil-Inverter am Eingang.

Vergleichen Sie dies mit der Steuerung der parallelen Dateneingänge durch den Takt des vorherigen synchronen ANSI SN75ALS166. Beachten Sie die Unterschiede in den ANSI-Datenetiketten.

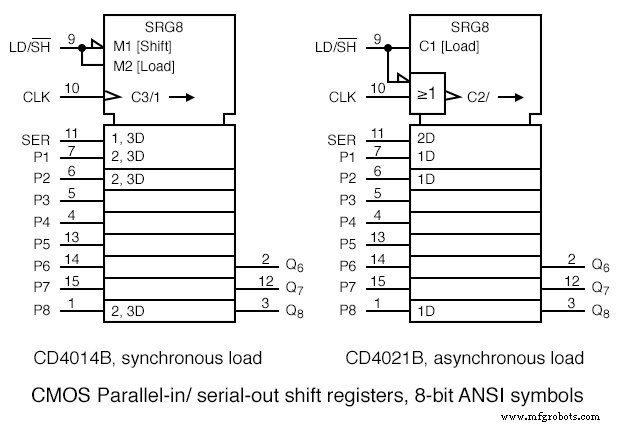

Auf CD4014B oben M1 wird geltend gemacht, wenn LD/SH’=0 . M2 wird geltend gemacht, wenn LD/SH’=1 .

Uhr C3/1 wird zum parallelen Laden von Daten in 2, 3D verwendet wenn M2 ist aktiv, wie durch die 2,3 . angezeigt Präfix-Labels.

Pins P3 zu P7 haben die gleichen internen 2,3 Präfix-Labels als P2 und P8 . Bei SER , die 1,3D Präfix impliziert, dass M1 und Uhr C3 sind erforderlich, um serielle Daten einzugeben.

Die Verschiebung nach rechts findet statt, wenn M1 aktiv ist, wie durch die 1 . angezeigt im C3/1 Pfeil .

Der CD4021B ist ein ähnliches Teil, mit Ausnahme des asynchronen parallelen Ladens von Daten, wie es durch das Fehlen von 2 . impliziert wird Präfix im Datenlabel 1D für Pins P1, P2, bis P8.

Natürlich Präfix 2 im Label 2D am Eingang SER sagt, dass Daten in diesen Pin getaktet werden. Das ODER Gate-Einschub zeigt, dass die Uhr von LD/SH’ . gesteuert wird .

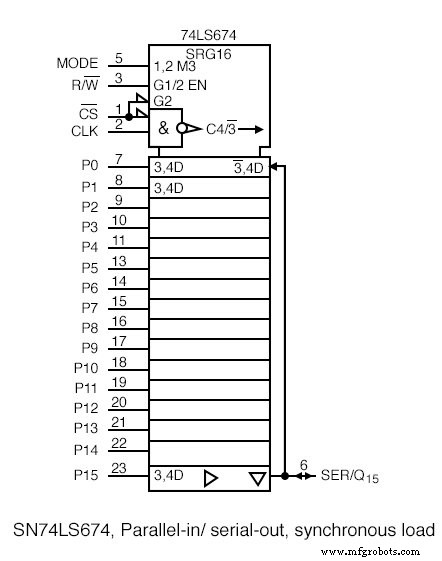

Das obige SN74LS674 interne Label SRG 16 zeigt 16-Bit-Schieberegister an.

Der MODUS Eingaben in den Steuerbereich oben auf dem Symbol sind mit 1,2 M3 gekennzeichnet . Intern M3 ist eine Funktion der Eingabe MODE und G1 und G2 wie durch die 1,2 . angezeigt vor M3 .

Das Basislabel G zeigt ein UND . an Funktion eines solchen G Eingänge. Eingabe R/W’ ist intern mit G1/2 EN gekennzeichnet .

Dies ist eine Aktivierung DE (gesteuert von G1 UND G2 ) für Tristate-Geräte, die an anderer Stelle im Symbol verwendet werden.

Wir weisen darauf hin, dass CS' Ein (Pin 1) ist intern G2 . Chipauswahl CS’ ist auch UND ed mit der Eingabe CLK um die innere Uhr C4 zu geben .

Die Blase innerhalb des Uhrpfeils zeigt an, dass sich die Aktivität auf der negativen Uhrflanke (Hoch-zu-Low-Übergang) befindet.

Der Schrägstrich (/) ist ein Trennzeichen, das zwei Funktionen für die Uhr impliziert. Vor dem Schrägstrich C4 zeigt die Kontrolle über alles mit dem Präfix 4 an .

Nach dem Schrägstrich die 3’ (Pfeil) zeigt eine Verschiebung an. Die 3' von C4/3' impliziert Verschiebung, wenn M3 deaktiviert ist (MODE=0 ). Der lange Pfeil zeigt an, dass Sie nach rechts (nach unten) schalten.

Unterhalb des Kontrollbereichs zum Datenbereich haben wir externe Eingaben P0-P15 , Stifte (7-11, 13-23).

Das Präfix 3,4 des internen Labels 3,4D zeigt an, dass M3 und die Uhr C4 Kontrollieren Sie das Laden von parallelen Daten.

Das D steht für Daten. Es wird davon ausgegangen, dass dieses Label für alle parallelen Eingänge gilt, jedoch nicht explizit ausgeschrieben wird.

Suchen Sie das Label 3',4D rechts vom P0 (Pin7) Stufe. Die ergänzten-3 zeigt an, dassM3=MODE=0 Eingaben (Schichten) SER/Q15 (pin5) zur Uhrzeit, (4 von 3’,4D) entsprechend der Uhr C4 .

Mit anderen Worten, mit MODE=0 , wir verschieben Daten in Q0 vom seriellen Eingang (Pin 6) Alle anderen Stufen verschieben sich zur Uhrzeit nach rechts (unten).

Wenn Sie sich zum unteren Rand des Symbols bewegen, zeigt das nach rechts zeigende Dreieck einen Puffer zwischen Q und der Ausgangspin.

Das nach unten zeigende Dreieck weist auf ein Tri-State-Gerät hin. Wir haben bereits erwähnt, dass der Tristate durch enable DE . gesteuert wird , was eigentlich G1 UND G2 ist aus dem Kontrollbereich.

Wenn R/W=0 , der Tri-State ist deaktiviert und wir können Daten in Q0 . verschieben über SER (Pin 6), ein Detail, das wir oben weggelassen haben. Wir brauchen eigentlich MODE=0, R/W’=0, CS’=0

Die interne Logik des SN74LS674 und eine Tabelle, die die Funktionsweise der Steuersignale zusammenfasst, finden Sie im Link in der Aufzählungsliste oben im Abschnitt.

Wenn R/W’=1 , der Tristate ist aktiviert, Q15 verschiebt SER/Q15 (Pin 6) und rezirkuliert zum Q0 Bühne über den rechten Draht zu 3',4D .

Wir haben angenommen, dass CS’ niedrig war, sodass wir C4/3’ und G2 auf EN takten in der Lage den Tri-State.

Praktische Anwendungen

Eine Anwendung eines Parallel-In/Serial-Out-Schieberegisters ist das Einlesen von Daten in einen Mikroprozessor.

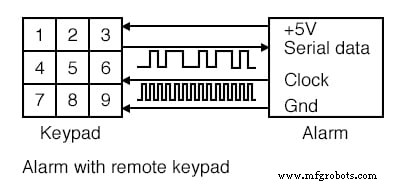

Der obige Alarm wird über eine Fernbedienung gesteuert. Die Alarmbox liefert +5V und Masse an die Fernbedienung, um sie mit Strom zu versorgen.

Der Alarm liest die entfernte Tastatur alle paar zehn Millisekunden, indem er Schiebetakte an die Tastatur sendet, die serielle Daten zurückgibt, die den Status der Tasten über ein Parallel-In/Serial-Out-Schieberegister anzeigen.

So lesen wir neun Schlüsselschalter mit vier Drähten. Wie viele Drähte wären erforderlich, wenn wir für jede der neun Tasten einen Stromkreis führen müssten?

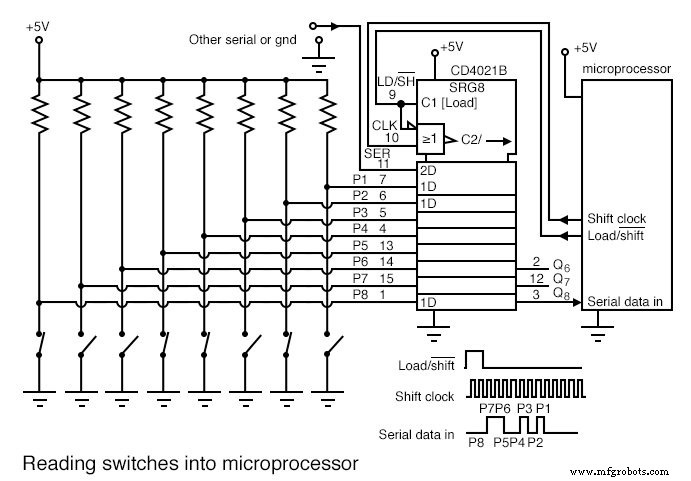

Eine praktische Anwendung eines Parallel-In/Serial-Out-Schieberegisters besteht darin, viele Schalterschließungen an nur wenigen Pins in einen Mikroprozessor einzulesen.

Einige Low-End-Mikroprozessoren haben nur 6-I/O-Pins (Input/Output) auf einem 8-Pin-Gehäuse.

Oder wir haben die meisten Pins auf einem 84-Pin-Gehäuse verwendet. Wir möchten möglicherweise die Anzahl der Drähte reduzieren, die um eine Leiterplatte, eine Maschine, ein Fahrzeug oder ein Gebäude herumlaufen.

Dies erhöht die Zuverlässigkeit unseres Systems. Es wurde berichtet, dass Hersteller, die die Anzahl der Kabel in einem Auto reduziert haben, ein zuverlässigeres Produkt herstellen.

In jedem Fall sind nur drei Mikroprozessor-Pins erforderlich, um 8-Bit-Daten von den Schaltern in der obigen Abbildung einzulesen.

Wir haben uns für ein asynchrones Ladegerät, das CD4021B, entschieden, weil es einfacher ist, das Laden von Daten zu kontrollieren, ohne einen einzigen parallelen Ladetakt erzeugen zu müssen.

Die parallelen Dateneingänge des Schieberegisters werden mit einem Widerstand an jedem Eingang auf +5V hochgezogen.

Wenn alle Schalter geöffnet sind, alle 1 s werden in das Schieberegister geladen, wenn der Mikroprozessor die LD/SH’ . bewegt Linie von niedrig nach hoch, dann wieder tief in Erwartung einer Verschiebung.

Beim Schließen des Schalters wird die Logik 0 angewendet s an die entsprechenden parallelen Eingänge. Das Datenmuster bei P1-P7 wird parallel geladen von LD/SH’=1 von der Mikroprozessor-Software generiert.

Der Mikroprozessor erzeugt Schiebeimpulse und liest ein Datenbit für jedes der 8 Bits.

Dieser Prozess kann vollständig mit Software durchgeführt werden, oder größere Mikroprozessoren können eine oder mehrere serielle Schnittstellen haben, um die Aufgabe mit Hardware schneller zu erledigen.

Mit LD/SH’=0 , generiert der Mikroprozessor eine 0 zu 1 Übergang auf der Shift Clock-Linie , liest dann ein Datenbit der Seriendaten in Linie. Dies wird für alle 8-Bit wiederholt.

Der SER Zeile des Schieberegisters kann von einer anderen identischen CD4021B-Schaltung angesteuert werden, wenn mehr Schaltkontakte gelesen werden müssen.

In diesem Fall erzeugt der Mikroprozessor 16-Shift-Impulse. Es ist wahrscheinlicher, dass es von etwas anderem gesteuert wird, das mit diesem seriellen Datenformat kompatibel ist, beispielsweise einem Analog-Digital-Wandler, einem Temperatursensor, einem Tastaturscanner, einem seriellen Festwertspeicher.

Bei den Schalterverschlüssen kann es sich um Endschalter an einem Maschinenschlitten, einen Übertemperatursensor, einen magnetischen Reedschalter, einen Tür- oder Fensterschalter, einen Luft- oder Wasserdruckschalter oder einen optischen Halbleiterschalter handeln.

VERWANDTE ARBEITSBLÄTTER:

- Schichtregister Arbeitsblatt

Industrietechnik