Universelle Schieberegister:Parallel-in, Parallel-out

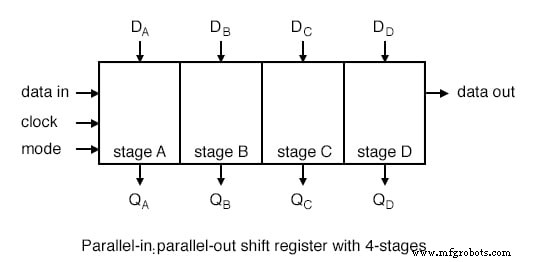

Der Zweck des Parallel-In/Parall-Out-Schieberegisters besteht darin, parallele Daten aufzunehmen, zu verschieben und dann wie unten gezeigt auszugeben.

Ein universelles Schieberegister ist ein Alleskönner zusätzlich zur Parallel-In/Parallel-Out-Funktion.

Oben wenden wir vier Datenbits an ein Parallel-In/Parallel-Out-Schieberegister bei DA . an DB DC DD . Die Modussteuerung, bei der es sich um mehrere Eingänge handeln kann, steuert das parallele Laden im Vergleich zum Verschieben.

Die Modussteuerung kann bei einigen realen Geräten auch die Richtung der Verschiebung steuern. Die Daten werden für jeden Taktimpuls um eine Bitposition verschoben.

Die verschobenen Daten stehen an den Ausgängen QA . zur Verfügung QB QC QD . „Dateneingang“ und „Datenausgang“ sind für die Kaskadierung mehrerer Stufen vorgesehen.

Oben können wir jedoch nur Daten für die Rechtsverschiebung kaskadieren. Wir könnten die Kaskadierung von Linksverschiebungsdaten anpassen, indem wir oben ein Paar von nach links weisenden Signalen, „Dateneingang“ und „Datenausgang“, hinzufügen.

Die internen Details eines nach rechts schiebenden Parallel-In/Parall-Out-Schieberegisters sind unten gezeigt.

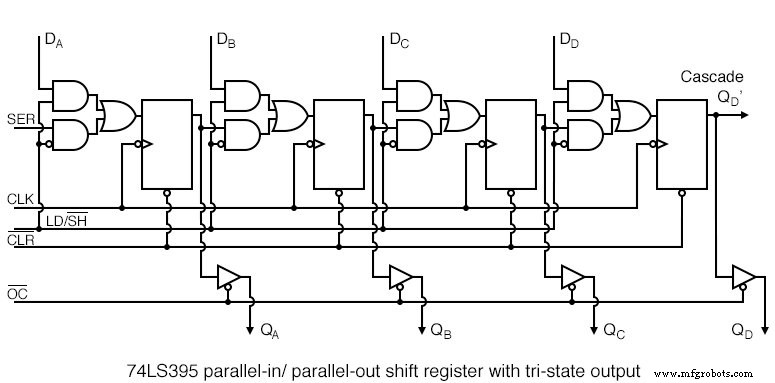

Die Tri-State-Puffer sind für das Parallel-In/Parallel-Out-Schieberegister nicht unbedingt erforderlich, aber sie sind Teil des unten gezeigten realen Geräts.

Das 74LS395 entspricht unserem Konzept eines hypothetischen rechtsschiebenden Parallel-In/Parall-Out-Schieberegisters so gut, dass wir eine stark vereinfachte Version der obigen Datenblattdetails verwenden.

Weitere Informationen finden Sie im Link zum vollständigen Datenblatt weiter unten in diesem Kapitel.

LD/SH’ steuert den UND-ODER-Multiplexer am Dateneingang der FFs. Wenn LD/SH’=1 , die oberen vier UND-Gatter sind aktiviert und ermöglichen die Anwendung paralleler Eingänge DA DB DC DD an die vier FF-Dateneingänge.

Beachten Sie die Inverterblase am Takteingang der vier FFs. Dies zeigt an, dass der 74LS395 Daten auf dem negativ gehenden Takt taktet, was der Übergang von hoch zu niedrig ist.

Die vier Datenbits werden parallel von DA . getaktet DB DC DD an QA QB QC QD bei der nächsten negativ gehenden Uhr. In diesem "realen Teil" OC' muss niedrig sein, wenn die Daten an den tatsächlichen Ausgangspins verfügbar sein müssen, anstatt nur an den internen FFs.

Die zuvor geladenen Daten können um eine Bitposition nach rechts verschoben werden, wenn LD/SH’=0 für die nachfolgenden negativ gehenden Taktflanken.

Vier Takte würden die Daten vollständig aus unserem 4-Bit-Schieberegister herausschieben. Die Daten würden verloren gehen, es sei denn, unser Gerät würde von QD . kaskadiert ’ an SER eines anderen Geräts.

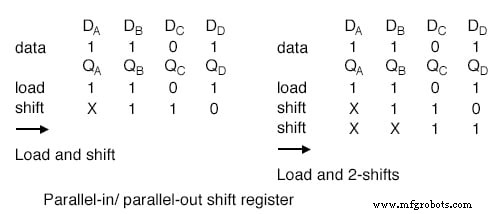

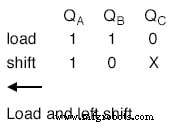

Oben wird den Eingängen DA . ein Datenmuster präsentiert DB DC DD . Das Muster wird in QA . geladen QB QC QD . Dann wird es ein Bit nach rechts verschoben.

Die eingehenden Daten sind mit X . gekennzeichnet , was bedeutet, dass wir nicht wissen, was es ist. Wenn die Eingabe (SER ) geerdet wären, würden wir beispielsweise wissen, welche Daten (0 ) wurde eingeschoben.

Ebenfalls dargestellt ist die Rechtsverschiebung um zwei Positionen, die zwei Takte erfordert.

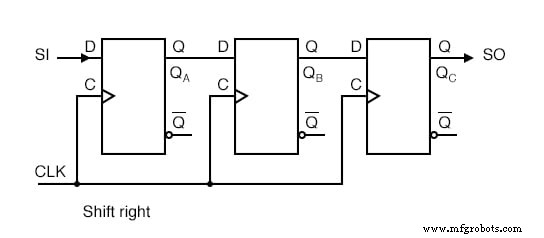

Die obige Abbildung dient als Referenz für die Hardware, die an der Rechtsverschiebung von Daten beteiligt ist.

Es ist zu einfach, sich auch nur mit dieser Figur zu beschäftigen, außer für den Vergleich mit komplexeren Figuren, die folgen.

Die Rechtsverschiebung von Daten wird oben als Bezug auf die vorherige Rechtsverschiebung bereitgestellt.

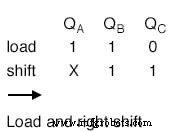

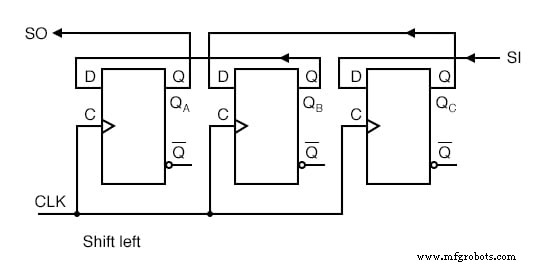

Wenn wir nach links verschieben müssen, müssen die FFs neu verkabelt werden. Vergleichen Sie mit dem vorherigen rechten Schalthebel. Außerdem SI und SO wurden umgekehrt. SI wechselt zu QC . QC wechselt zu QB . QB wechselt zu QA . QA Blätter am SO Verbindung, wo es zu einem anderen Shifter kaskadieren könnte SI . Diese linke Shift-Sequenz ist rückwärts von der rechten Shift-Sequenz.

Oben verschieben wir dasselbe Datenmuster um ein Bit nach links.

Es gibt ein Problem mit der obigen Abbildung „nach links verschieben“. Es gibt keinen Markt dafür. Niemand stellt ein Shift-Links-Teil her.

Ein „echtes Gerät“, das eine Richtung verschiebt, kann extern verdrahtet werden, um die andere Richtung zu verschieben. Oder sollten wir sagen, es gibt kein Links oder Rechts im Kontext eines Geräts, das sich nur in eine Richtung bewegt.

Es gibt jedoch einen Markt für ein Gerät, das auf Befehl durch eine Steuerleitung nach links oder rechts verschoben wird. Links und rechts sind in diesem Zusammenhang natürlich gültig.

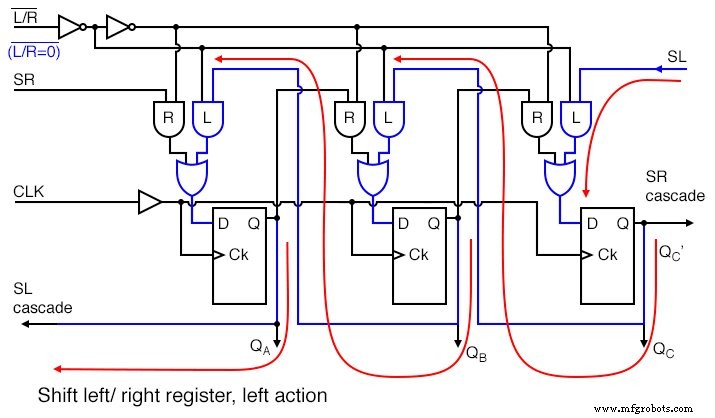

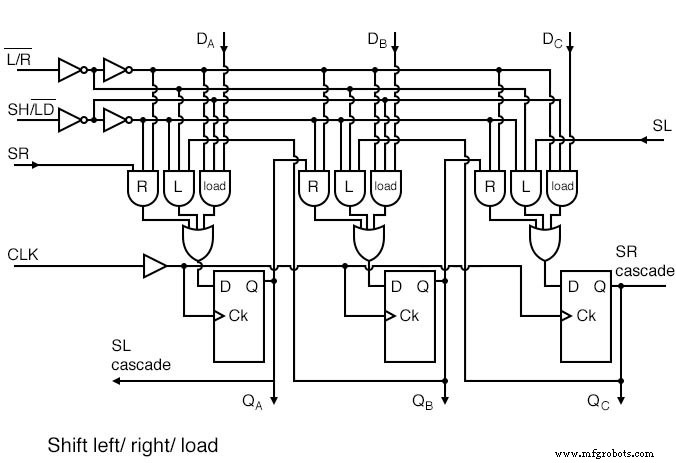

Was wir oben haben, ist ein hypothetisches Schieberegister, das in der Lage ist, unter der Kontrolle von L’/R . in beide Richtungen zu verschieben .

Es ist eingerichtet mit L’/R=1 um die normale Richtung zu verschieben, nach rechts. L’/R=1 aktiviert die UND-Gatter des Multiplexers mit der Bezeichnung R .

Dadurch können die Daten dem durch die Pfeile dargestellten Pfad folgen, wenn ein Takt angelegt wird. Der Verbindungspfad ist der gleiche wie in der "zu einfachen" "nach rechts verschieben" Abbildung oben.

Datenverschiebungen bei SR , an QA , zu QB , bis QC , wo es an der SR-Kaskade austritt . Dieser Pin könnte SR auslösen eines anderen Geräts auf der rechten Seite.

Was ist, wenn wir L’/R ändern? zu L’/R=0 ?

Mit L’/R=0 , die UND-Gatter des Multiplexers mit der Aufschrift L aktiviert sind, was einen Pfad ergibt, der durch die Pfeile angezeigt wird, der gleiche wie in der obigen Abbildung "nach links verschieben".

Datenverschiebungen in SL , bis QC , zu QB , an QA , wo es an der SL-Kaskade abfährt . Dieser Pin könnte SL antreiben eines anderen Geräts auf der linken Seite.

Die Haupttugend der obigen beiden Abbildungen, die das „Shift-Links/Rechts-Register“ veranschaulichen, ist Einfachheit.

Die Bedienung des linken rechten Steuerelements L’/R=0 ist leicht zu befolgen. Ein kommerzieller Teil benötigt das parallele Laden der Daten, das durch den Abschnittstitel impliziert wird. Dies erscheint in der Abbildung unten.

Jetzt können wir mit L’/R sowohl nach links als auch nach rechts verschieben , fügen wir SH/LD’ hinzu , Shift/Load und die UND-Gatter mit der Aufschrift „load“ zum parallelen Laden von Daten von den Eingängen DA DB DC .

Wenn SH/LD’=0 , UND-Gatter R und L sind deaktiviert, UND-Gatter "Laden" werden aktiviert, um Daten DA . weiterzugeben DB DC an die FF-Dateneingänge. die nächste Uhr CLK taktet die Daten auf QA QB QC .

Solange die gleichen Daten vorhanden sind, werden sie bei nachfolgenden Takten neu geladen. Daten, die nur für einen Takt vorhanden sind, gehen jedoch von den Ausgängen verloren, wenn sie nicht mehr an den Dateneingängen vorhanden sind.

Eine Lösung besteht darin, die Daten auf einen Takt zu laden und dann mit der Verschiebung auf den nächsten vier Takten fortzufahren. Dieses Problem wird beim 74ALS299 durch Hinzufügen eines weiteren UND-Gatters zum Multiplexer behoben.

Wenn SH/LD’ wird geändert in SH/LD’=1 , sind die UND-Gatter mit der Aufschrift „Laden“ deaktiviert, sodass die linke/rechte Steuerung L’/R möglich ist um die Richtung der Verschiebung auf dem L einzustellen oder R UND Tore. Das Schalten erfolgt wie in den vorherigen Abbildungen.

Das einzige, was erforderlich ist, um ein praktikables integriertes Gerät zu produzieren, ist das Hinzufügen des vierten UND-Gatters zum Multiplexer, wie für den 74ALS299 angedeutet.

Dies wird im nächsten Abschnitt für diesen Teil gezeigt.

Parallel-in/Parallel-out und universelle Geräte

Werfen wir einen genaueren Blick auf die als integrierte Schaltungen verfügbaren Serial-In/Parallel-Out-Schieberegister mit freundlicher Genehmigung von Texas Instruments.

Für vollständige Gerätedatenblätter folgen Sie den Links.

-

SN74LS395A Parallel-in/Parallel-out 4-Bit-Schieberegister

-

SN74ALS299 Parallel-in/Parallel-out 8-Bit-Universal-Schieberegister

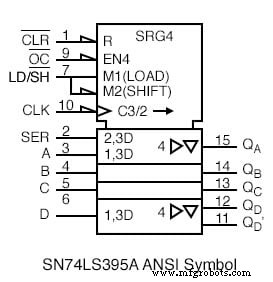

Wir haben uns bereits die internen Details des SN74LS395A angesehen, siehe obige Abbildung, 74LS395 Parallel-In/Parallel-Out-Schieberegister mit Tri-State-Ausgang.

Direkt darüber befindet sich das ANSI-Symbol für den 74LS395.

Warum nur 4-Bit, wie durch SRG4 angegeben Oben? Wenn sowohl parallele Eingänge als auch parallele Ausgänge zusätzlich zu Steuer- und Strompins vorhanden sind, können keine weiteren I/O-Bits (Input/Output) in einem 16-Pin-DIP (Dual Inline Package) verwendet werden.

R zeigt an, dass die Schieberegisterstufen durch Eingabe CLR’ zurückgesetzt werden (aktiver Low-invertierender Halbpfeil am Eingang) des Bedienteils am oberen Rand des Symbols. OC’ , wenn niedrig, (Pfeil umkehren) wird aktiviert (EN4 ) die vier Tristate-Ausgangspuffer (QA QB QC QD ) im Datenbereich.

Laden/Verschieben’ (LD/SH’ ) an Pin (7) entspricht den Einbauten M1 (Laden) und M2 (Schicht). Suchen Sie nach Präfixen von 1 und 2 im Rest des Symbols, um festzustellen, was von diesen gesteuert wird.

Der gegen die Flanke empfindliche Taktgeber (angezeigt durch den invertierten Pfeil an Pin-10) C3/2 hat zwei Funktionen.

Zuerst die 3 von C3/2 betrifft alle Eingaben mit dem Präfix 3 , sagen Sie 2,3D oder 1,3D im Datenbereich.

Dies wäre eine parallele Last bei A, B, C, D zugeschrieben M1 und C3 für 1,3D . Zweitens 2 von C3/2 -Pfeil nach rechts zeigt die Datentaktung überall dort an, wo 2 erscheint in einem Präfix (2,3D an Pin-2).

Somit haben wir eine Datentaktung bei SER in QA mit Modus 2 . Der Rechtspfeil nach C3/2 berücksichtigt Verschiebungen an internen Schieberegisterstufen QA QB QC QD .

Die nach rechts zeigenden Dreiecke zeigen die Pufferung an; das umgekehrte Dreieck zeigt Tri-State an, gesteuert von der EN4 .

Beachten Sie, dass alle 4 s im Symbol für DE werden häufig weggelassen. Phasen QB QC haben die gleichen Attribute wie QD . QD ’ kaskadiert zum SER des nächsten Pakets nach rechts.

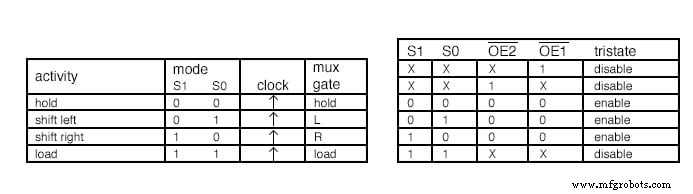

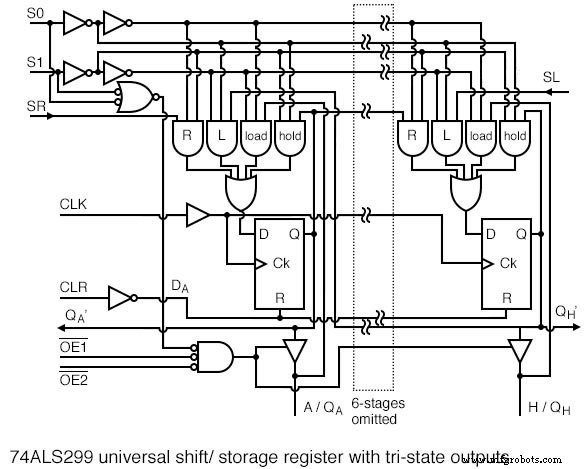

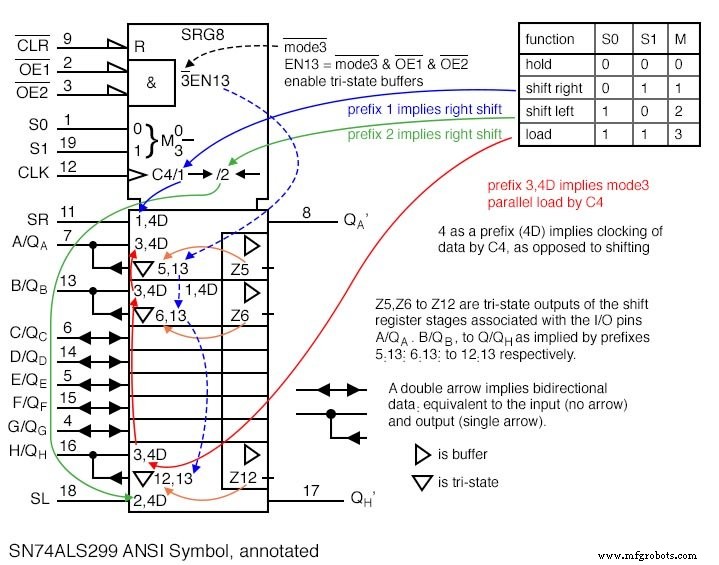

Die obige Tabelle, zusammengefasst aus dem Datenblatt '299, fasst die Funktionsweise des universellen Schiebe-/Speicherregisters 74ALS299 zusammen.

Folgen Sie dem obigen '299-Link, um alle Details zu erfahren. Die Multiplexer-Gates R , L , laden funktionieren wie in den vorherigen Abbildungen zum „Shift-Links/Rechts-Register“.

Der Unterschied besteht darin, dass der Modus S1 . eingibt und S0 Wählen Sie nach links verschieben, nach rechts verschieben und laden Sie mit dem Modus S1 S0 = bis 01 , 10 , und 11 jeweils wie in der Tabelle gezeigt, aktivieren Multiplexer-Gates L , R , und laden bzw.

Siehe Tabelle. Ein kleiner Unterschied ist der parallele Lastpfad von den Tri-State-Ausgängen. Tatsächlich sind (müssen) die Tri-State-Puffer deaktiviert durch S1 S0 =11 den I/O-Bus zu floaten zur Verwendung als Eingänge.

Ein Bus ist eine Sammlung ähnlicher Signale. Die Eingaben werden auf A angewendet , B bis H (gleiche Pins wie QA , QB , bis QH ) und an die Last weitergeleitet Gate in den Multiplexern und auf dem D Eingänge der FFs. Daten werden parallel auf einen Takt geladen.

Das einzige neue Multiplexer-Gatter ist das UND-Gatter mit der Bezeichnung hold , aktiviert durch S1 S0 =00 . Das Halten gate ermöglicht einen Weg vom Q Ausgabe des FF zurück zum Halten Gate an den D-Eingang desselben FF. Das Ergebnis ist, dass mit Modus S1 S0 =00 , wird der Ausgang mit jedem neuen Takt kontinuierlich neu geladen. Somit werden Daten gehalten. Dies ist in der Tabelle zusammengefasst.

So lesen Sie Daten aus den Ausgängen QA , QB , bis QH , müssen die Tri-State-Puffer aktiviert werden durch OE2’, OE1’ =00 und Modus =S1 S0 =00, 01 oder 10 .

Das heißt, Modus ist alles außer Laden . Siehe zweite Tabelle.

Daten von einem Paket nach rechts nach links verschieben, auf der SR einschieben Eingang. Alle Daten, die von Stufe QH nach rechts verschoben wurden Kaskaden nach rechts über QH ’.

Diese Ausgabe wird durch die Tri-State-Puffer nicht beeinflusst. Die Rechtsverschiebungsfolge für S1 S0 =10 ist:

SR> QA> QB> QC> QD> QE> QF> QG> QH (QH ’)

Daten von einem Paket von links nach rechts verschieben auf der SL Eingang. Alle Daten, die aus Stufe QA nach links verschoben wurden Kaskaden nach links über QA “, ebenfalls unbeeinflusst von den Tri-State-Puffern. Die Shift-Links-Sequenz für S1 S0 =01 ist:

(QA ’) QA

Das Verschieben kann mit deaktivierten Tri-State-Puffer durch einen der OE2' . erfolgen oder OE1’ =1 . Auf die Registerinhaltsausgänge kann jedoch nicht zugegriffen werden. Siehe Tabelle.

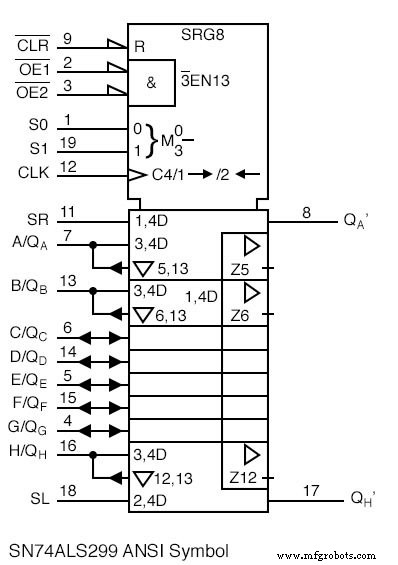

Das „saubere“ ANSI-Symbol für das SN74ALS299 Parallel-In/Parallel-Out-8-Bit-Universal-Schieberegister mit Tri-State-Ausgang ist oben als Referenz gezeigt.

Die kommentierte Version des ANSI-Symbols wird gezeigt, um die darin enthaltene Terminologie zu verdeutlichen.

Beachten Sie, dass der ANSI-Modus (S0 S1) von der in der vorherigen Tabelle verwendeten Reihenfolge (S1 S0) umgekehrt ist.

Das kehrt die Dezimalmoduszahlen (1 &2) um. Auf jeden Fall stimmen wir dem offiziellen Datenblatt vollständig zu und kopieren diese Inkonsistenz.

Praktische Anwendungen

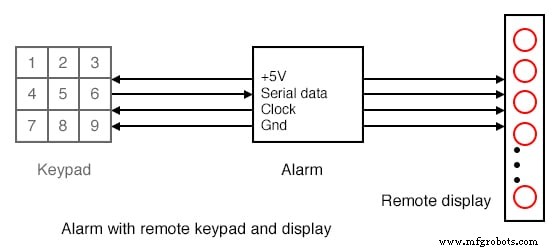

Das Blockschaltbild Alarm mit Fernbedienung wird unten wiederholt. Bisher haben wir den Tastaturleser und die Fernanzeige als separate Einheiten gebaut.

Jetzt werden wir sowohl die Tastatur als auch das Display mit einem universellen Schieberegister zu einer einzigen Einheit kombinieren.

Obwohl im Diagramm getrennt, befinden sich die Tastatur und das Display beide im selben Remote-Gehäuse.

Wir werden die Tastaturdaten mit einem einzigen Taktimpuls parallel in das Schieberegister laden und dann zur Hauptalarmbox verschieben.

Gleichzeitig verschieben wir LED-Daten vom Hauptalarm zum Remote-Schieberegister, um die LEDs zu beleuchten.

Wir werden gleichzeitig Tastaturdaten und LED-Daten in das Schieberegister verschieben.

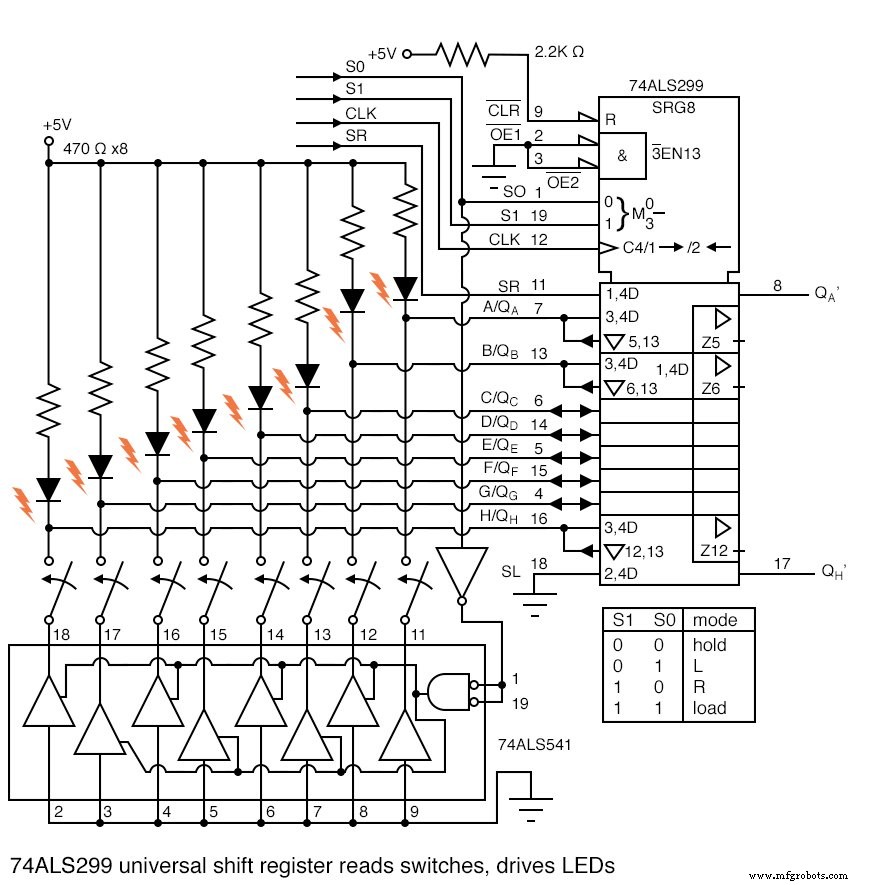

Acht LEDs und Strombegrenzungswiderstände sind mit den acht I/O-Pins des Universalschieberegisters 74ALS299 verbunden.

Die LEDs können nur im Modus 3 mit S1=0 S0=0 betrieben werden . Die OE1’ und OE2’ Tristate-Freigaben sind geerdet, um die Tristate-Ausgänge während der Modi 0, 1, 2 dauerhaft zu aktivieren .

Dadurch leuchten (flimmern) die LEDs während des Schaltens. Wenn dies ein Problem wäre, die EN1 ’ und EN2’ könnte ungeerdet und parallel zu S1 sein und S0 um nur die Tristate-Puffer zu aktivieren und die LEDs während des Haltens zu leuchten, Modus 3 . Lassen Sie es uns für dieses Beispiel einfach halten.

Beim parallelen Laden S0=1 zu 0 invertiert, ermöglicht es den oktalen Tristate-Puffern, die Schalterwischer zu erden.

Die oberen, offenen Schaltkontakte werden durch die Widerstands-LED-Kombination an den acht Eingängen auf logisch High gezogen.

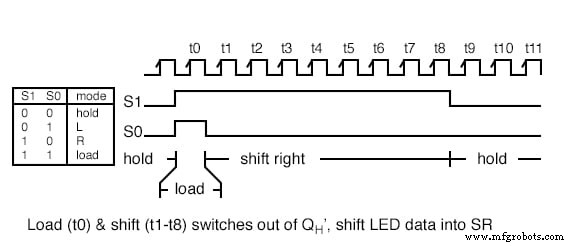

Jedes Schließen des Schalters wird den Eingang niedrig kurzschließen. Wir laden die Switch-Daten parallel in die ‘299 um Uhr t0 wenn beide S0 und S1 sind hoch. Siehe Wellenformen unten.

Einmal S0 sinkt, acht Uhr (t0 zut8 ) Daten zum Schließen des Schalters aus dem ‘299 . verschieben über das Qh ’ Pin.

Gleichzeitig werden neue LED-Daten bei SR eingeschoben der 299 um die gleichen acht Uhren. Die LED-Daten ersetzen die Schalterschließdaten, wenn das Schalten fortschreitet.

Nach der 8. Schicht, t8 , S1 sinkt in den Ertragshaltemodus (S1 S0 =00 ). Die Daten im Schieberegister bleiben auch bei mehr Takten gleich, zum Beispiel T9 , t10 , usw.

Woher kommen die Wellenformen? Sie könnten von einem Mikroprozessor erzeugt werden, wenn die Taktrate nicht über 100 kHz liegt. In diesem Fall wäre es unpraktisch, Takte nach t8 . zu generieren .

Wenn die Uhr im Megahertz-Bereich wäre, würde die Uhr kontinuierlich laufen. Die Uhr, S1 und S0 würde durch digitale Logik erzeugt, hier nicht gezeigt.

VERWANDTE ARBEITSBLÄTTER:

- Schichtregister Arbeitsblatt

Industrietechnik