So entwerfen Sie Bildebenen für Hochgeschwindigkeits-Leiterplatten

Heutzutage werden mehrschichtige Leiterplatten in den meisten Hochgeschwindigkeitsschaltungssystemen verwendet, und viele Schaltungssysteme haben zahlreiche Betriebsleistungen, was strenge Anforderungen an das Bildebenendesign stellt, insbesondere an die Regelung der Beziehungen zwischen mehreren Stromversorgungs-/Masseebenen. Außerdem muss eine spezielle kupferkaschierte Oberfläche für das Design der Geräteschicht entwickelt werden, um zu verhindern, dass Oszillatoren HF-Energie (Hochfrequenz) erzeugen, und um eine hervorragende Wärmeableitung für Hochleistungskomponenten zu gewährleisten.

Funktionen von Bildebenen

Bildebenen sind eine kupferkaschierte Oberfläche, die an Signalschichten in Leiterplatten angrenzt. Zu den Hauptfunktionen von Bildebenen gehören:

1). Reduzierung von Reflow-Rauschen und EMI (elektromagnetische Interferenz). Bildebenen bieten Pfade mit niedriger Impedanz für den Signalrückfluss, insbesondere wenn im Stromverteilungssystem ein hoher Strom fließt. Darüber hinaus verkleinern sie die geschlossene Ringfläche, die durch Signal und Reflow gebildet wird, sodass die EMI sinkt.

2). Steuern des Übersprechens zwischen Signalleitungen in digitalen Hochgeschwindigkeitsschaltungen. Das Übersprechen wird durch das Verhältnis D/H bestimmt, wobei sich D auf den Abstand zwischen Störquelle und gestörtem Objekt und H auf die Höhe von Bildebenen zwischen Signalschichten bezieht. Das Verhältnis D/H kann gesteuert werden, indem der Wert von H geändert wird, so dass das Übersprechen zwischen Signalleitungen letztendlich gesteuert wird.

3). Kontrolle der Impedanz. Die charakteristische Impedanz einer gedruckten Verdrahtung hängt von der Breite der Drähte und der Höhe zwischen Drähten und Bildebenen ab. Wenn keine Bildebene vorhanden ist, kann die Impedanz möglicherweise nicht kontrolliert werden, was zu einem Ausfall der Übertragungsleitungsanpassung und Signalreflexion führt.

Außerdem sind Bildebenen auch in der Lage, das Rauschen von Reflexionen zu äußeren Platten zu kontrollieren. Es muss anerkannt werden, dass Bildebenen allein für die Implementierung dieser Funktionen nicht ausreichen, strenge Designregeln müssen ergänzt werden, um die erwarteten Ziele zu erreichen. Diese Tatsache kann folgendermaßen ausgedrückt werden:Um das Rauschen in digitalen Hochgeschwindigkeitsschaltungen zu kontrollieren, sind Bildebenen unerlässlich, aber sie können nicht alleine funktionieren.

Layer-Skipping von Signal Reflow

Bei mehrschichtigen Leiterplatten sollte jede Layoutschicht an eine Bildebene angrenzen und die Rückleitung von Signalen auf der entsprechenden Bildebene fließen. Wenn eine Signalleitung nicht durch eine Layoutschicht verläuft, besteht das übliche Verfahren darin, dass zuerst eine Signalleitung mit einer Layoutschicht verbunden wird und dann die Signalleitung mit einer anderen Schicht durch Durchgangslöcher verbunden wird. Daher springt die Signalleitung von einer Schicht zur anderen und der Rückstrom folgt demselben Pfad. Wenn beide Schichten Masseschichten sind, kann der Rückstrom durch Durchgangslöcher, die zwei Schichten oder Massestifte verbinden, überspringen. Wenn eine Schicht die Leistungsschicht und die andere die Erdungsschicht ist, ist die einzige Möglichkeit des Rückstroms, zwischen den Schichten zu springen, die Position mit dem platzierten Entkopplungskondensator. Wenn es keinen Entkopplungskondensator oder Durchgangslöcher gibt, die die Erdungsschicht verbinden, muss das Überspringen durch Rückstrom erfolgen, der den weitesten Weg zurücklegen muss, wodurch der Rückstrom von anderen Schaltkreisen entkoppelt wird, so dass Übersprechen und EMI verursacht werden.

Daher sollte Layer-Skipping im Prozess des PCB-Designs an den Massepins neben den Komponenten oder am besten um den Entkopplungskondensator herum eingestellt werden. Wenn dies nicht möglich ist, können Erdungsdurchgangslöcher (Überspringen zwischen zwei Erdungsschichten) oder Bypass-Kondensatoren (Überspringen zwischen einer Leistungsschicht und einer Erdungsschicht) am Sprungpunkt platziert werden, um den Rückstrom zu überspringen>

Ebenen teilen

Bei der Verwendung von mehrschichtigen Leiterplatten ist es manchmal erforderlich, einen Bereich ohne Kupferfolie mit einer bestimmten Breite zu erzeugen, indem eine integrierte Bildebene in mehrere unabhängige Teile geteilt wird, was als Teilungsebenen bezeichnet wird.

Das Teilen von Ebenen wird normalerweise verwendet, um Rauschen zu stoppen, das empfindliche Schaltkreise stört, und verschiedene Referenzspannungen zu isolieren, z

Teilungsebenen können in vollständige Teilung und unvollständige Teilung eingeteilt werden. Ersteres bezieht sich auf die vollständige Isolierung zwischen Leistungsschichten und Erdungsschichten nach dem Splitten. Letzteres bezieht sich auf die vollständige Isolierung zwischen Leistungsschichten, während Masseschichten durch "Brücken" verbunden sind. Ob eine vollständige oder unvollständige Aufteilung verwendet wird, hängt davon ab, ob eine Signalverbindung zwischen den Aufteilungsebenen besteht.

• Beispiele zum Teilen von Ebenen

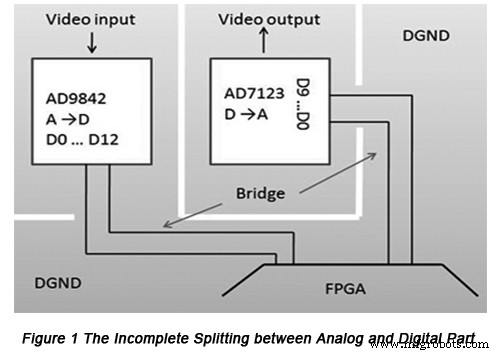

Abbildung 1 ist ein Teil des Bildebenendesigns einer analogen und digitalen gemischten Schaltung einer Testplattform. Das analoge Videoeingangssignal wird durch AD-Wandlung zum FPGA übertragen und als DA-Wandlung ausgegeben. Sowohl AD als auch DA verwenden unabhängige Leistungskomponenten zur Bereitstellung von Strom. Digitale Komponenten nehmen den größten Teil des Platzes der Platine ein, während analoge Komponenten nur einen kleinen Teil ausmachen. Sie alle sind jedoch wesentliche Teile, die für die Leistung des gesamten Systems wichtig sind. Daher muss beim Umgang mit diesen Komponenten viel Sorgfalt aufgewendet werden. Es ist ideal, dass das Rauschen des digitalen Teils nicht in den analogen Teil eindringt. Einige Signale von AD- und DA-Wandlern sind jedoch mit dem FPGA des digitalen Teils verbunden. Um den Rückfluss dieser angeschlossenen Signale zu gewährleisten, müssen die digitale Stromversorgung und die analoge Stromversorgung vollständig isoliert werden, während die digitale Masse und die analoge Masse unvollständig isoliert werden müssen, damit der Einfluss des analogen Teils vom digitalen Teil auf ein Minimum reduziert wird.

Alle Leitungen vom Digitalteil zum Analogteil müssen durch die Brücke verlaufen, deren Öffnungsgröße gerade für die Durchführung der erforderlichen Drähte geeignet sein sollte, damit der Datensignalrückfluss durch die Brücke zurückkehren kann, wodurch die Interferenz mit anderen Signalen vermieden wird der Wicklung für den Rückweg. Bei diesem PCB-Design sind die Massen von AD- und DA-Teil vollständig voneinander isoliert.

• Einige Probleme beim Teilen von Ebenen

a. Überlappung von Isolationsschichten

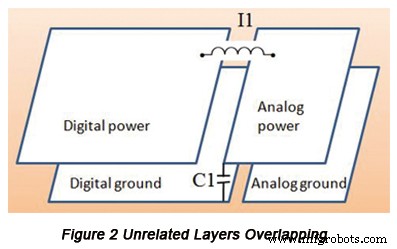

In den Multilayer-Leiterplatten werden normalerweise Trennebenen verwendet, um unterschiedliche Leistungen zu isolieren. Im Allgemeinen sind die entsprechenden Masseschichten dieser Kräfte gegeneinander isoliert, dh jede Kraft hat ihre eigene Referenzschicht. Im Prozess des PCB-Designs müssen Überlappungen von Isolationsschichten vermieden werden. Beispielsweise sind in den meisten mehrschichtigen Leiterplatten die Leistungs- und Erdungsschicht des analogen Teils und des digitalen Teils voneinander isoliert. Analoge Power-Layer und digitale Ground-Layer dürfen sich räumlich nicht wie in Abbildung 2 überschneiden.

Wenn eine überlappende Isolationsschicht auftritt, erscheint eine kleine Pad-Kapazität C1 im überlappenden Bereich. Die Kapazität bewirkt, dass HF-Energie von einer Schicht zu einer anderen isolierten, statischen und unabhängigen Schicht übertragen wird, um die Gültigkeit der Isolierung zu verringern.

b. Platzierung des Entkopplungskondensators

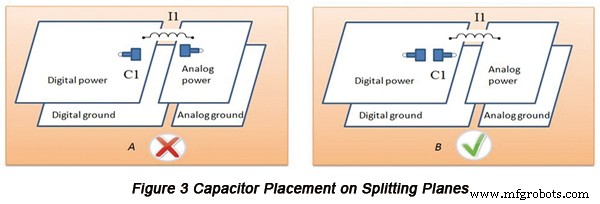

Um das hochfrequente Rauschen zu filtern, das von Hochgeschwindigkeitskomponenten erzeugt wird, sind viele Entkopplungskondensatoren auf Leiterplatten angeordnet. Wenn in Leiterplatten Trennebenen herauskommen, kann es beim Layoutprozess dazu kommen, dass Massepins des Entkopplungskondensators nicht mit anderen Referenzmasselagen verbunden werden, sondern mit der entsprechenden Masselage. Diese Art von Fehler wird möglicherweise auftreten und führt zu einer Rauschentkopplung von einer Schicht zur anderen, die ähnlich ist wie bei sich überlappenden Teilungsebenen. Deshalb sollte dieses Problem bereits in der Entwurfsphase behandelt werden. Nehmen Sie als Beispiel wieder eine digital-analoge gemischte Schaltung. Die analoge Leistung wird vom digitalen Teil über die Ferritperle zugeführt, und C1 bezieht sich auf die Entkopplungskapazität des digitalen Teils. In Abbildung 3A sind die Stromversorgungsstifte von C1 mit der digitalen Stromversorgung verbunden, während die Erdungsstifte mit der analogen Masse verbunden sind, was zur Entkopplung von digitalem Rauschen mit hoher Frequenz im empfindlichen analogen Teil führt, was eine falsche Verbindung ist. Abbildung 3B ist eine rechte Entkopplungskondensatorverbindung.

c. Einzelpunkterdung

Beim Zusammenschalten von Referenzlagen unterschiedlicher Leistung ist auf Einzelpunkterdung zu achten. In der beispielhaften gemischten Digital-Analog-Schaltung werden Leiterplatten in einen digitalen Teil und einen analogen Teil eingeteilt, und sowohl die digitale Masse als auch die analoge Masse haben mindestens zwei Verbindungspunkte, so dass ein Rauschsignal möglicherweise eine Zirkulation zwischen zwei Referenzschichten durch die zwei Verbindungspunkte bildet, das heißt "Erdschleife" genannt. Eine Masseschleife führt zu Rauschen, EMI, Energieverbrauch und Schwierigkeiten bei der Wärmeableitung. Es gibt eine einfache Lösung für das Problem der Masseschleife:Solange es nur einen Verbindungspunkt zwischen Referenzschichten gibt, kann keine Schleife gebildet werden.

Lokale Bodenleger

Als Teil von Bildebenen beziehen sich lokale Erdungsschichten auf eine Kupferplattierung auf der Oberseite von Leiterplatten, die direkt mit der inneren Erdungsschicht verbunden ist. Seine Hauptfunktion besteht darin, den HF-Magnetfluss zu erfassen, der im Inneren einiger Schlüsselchips (z. B. Oszillatoren) erzeugt wird, oder zur Verlustleistung zu verwenden.

Um eine hervorragende Leistung zu erzielen, sollten Oszillatoren, Kristalle und Uhrenhalterungen auf einer unabhängigen lokalen Erdungsschicht montiert werden. Zu den Gründen gehören:

1). Wenn der Oszillator in eine Metallummantelung gepackt ist, ist der innerhalb der Metallummantelung erzeugte HF-Strom möglicherweise so groß, dass seine Erdungsstifte den großen Strom nicht mit einem Verfahren mit geringem Energieverbrauch zur Erde leiten können. Dadurch wird dieser Metallmantel zu einer unipolaren Antenne.

2). Wenn beim Platzieren des Oszillators auf Leiterplatten die Oberflächenmontagetechnik verwendet wird, wird das oben erwähnte Problem noch schlimmer, da in der SMT-Verpackung normalerweise Kunststoffmaterial verwendet wird, wodurch der zum Erdungspunkt geführte HF-Strom unterbrochen wird. Schließlich wird innerhalb der Verpackung erzeugter HF-Strom in den freien Raum abgestrahlt und mit anderen Komponenten entkoppelt.

3). Gewöhnliche Oszillatoren sind in der Lage, die Taktpufferung zu treiben, die zu Komponenten mit superhoher Geschwindigkeit und schneller Flankenrate gehört, wodurch eine große Menge an HF-Strom erzeugt wird, was möglicherweise zu einem Ausfall der Stromfunktion führt.

Wenn eine lokale Erdungsschicht in den Oszillator- und Taktschaltkreis eingebaut wird, werden Bildebenen bereitgestellt, die verwendet werden, um die im Inneren des Oszillators und der entsprechenden Schaltkreise erzeugte HF-Energie einzufangen, so dass die HF-Strahlung verringert werden kann.

20-H-Regel

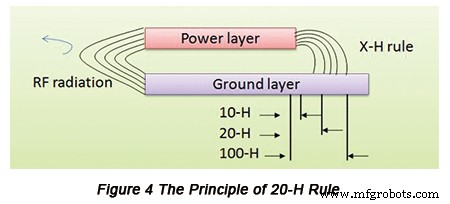

Als empirische Regel beschreibt die 20-H-Regel, dass bei mehrschichtigen Leiterplatten mit hoher Dichte die Größe der Leistungsschicht um 20 H kleiner sein sollte als die der Masseschicht, in der H bezieht sich auf den Abstand zwischen den beiden Schichten. In Abbildung 4 zeigt der linke Teil die Power/Ground-Schicht ohne spezielles Design, bei der die Randstrahlung so stark ist, dass sie die Funktionen der angrenzenden Schaltung beeinflusst. Der rechte Teil zeigt die HF-Strahlungssituation durch abnehmende Leistungsflächengröße um X-H. Es ist ersichtlich, dass die Bodenschicht viele magnetische Kraftlinien anzieht und die HF-Strahlungsenergie verringert wird. Gemäß den Ergebnissen von Experimenten beginnt die HF-Strahlungskraft von 10-H abzunehmen; im Fall von 20-H kann der Boden 70 % des magnetischen Flusses anziehen; im Fall von 100-H kann die Magnetkraft um 98 % abnehmen.

Natürlich ist 20-H nicht perfekt für alle PCB-Strukturen. Die Effizienz von 20-H hängt von der Betriebsfrequenz, der physikalischen Größe der Leistungs-/Masseschicht und dem Abstand zwischen ihnen ab, wobei die letzten beiden Elemente die SRF (Eigenresonanzfrequenz) der Leiterplatte bestimmen. Untersuchungen zeigen, dass 20-H nicht funktioniert, wenn PCB an einer SRF betrieben wird, und der Boden auch keine Strahlungsenergie anzieht. Was noch schlimmer ist, es wird stattdessen viel Strahlungsenergie erzeugt. Daher müssen in der praktischen Hochgeschwindigkeitsschaltung bestimmte Situationen berücksichtigt werden, wenn entschieden wird, ob die 20-H-Regel gewählt wird oder nicht.

Hilfreiche Ressourcen

• Hochgeschwindigkeits-Layout-Tipps

• Hochgeschwindigkeits-Leiterplatten-Routing-Techniken zur Reduzierung des Einflusses von EMI

• Missverständnisse und Strategien zum Hochgeschwindigkeits-Leiterplattendesign

• Differenzial isometrisch Verarbeitungs- und Simulationsverifizierung von Hochgeschwindigkeits-PCB-Designs

• PCB-Fertigungsservice mit vollem Funktionsumfang von PCBCart – Mehrere Mehrwertoptionen

• Erweiterter PCB-Bestückungsservice von PCBCart – ab 1 Stück

Industrietechnik

- Design für Herstellbarkeit:Eine Anleitung

- Designtipps zum Schutz von Hochgeschwindigkeitsschnittstellen

- SMT-Bestückung für Leiterplatten

- Leiterplatten für raue Umgebungen

- Leitfaden zu den IPC-Standards für Leiterplatten

- Design für die Herstellung von Leiterplatten

- Vorbereitung auf Industrie 4.0

- So entwerfen Sie ein vorbeugendes Wartungsprogramm für Ihre Ausrüstung

- Wichtige Designrichtlinien für die Herstellung und Bestückung von Leiterplatten – Teil I

- Wichtige Designrichtlinien für die Herstellung und Bestückung von Leiterplatten – Teil II