Differentiale isometrische Verarbeitung und Simulationsverifizierung von Hochgeschwindigkeits-PCB-Design

Einfluss der relativen Verzögerung auf Signale

Signale, die in Differenzsignalleitungen übertragen werden, enthalten Gegentaktkomponenten und Gleichtaktkomponenten von Signalen.

Die Menge der Differenzsignale bezieht sich auf die Differenz zwischen zwei Signalen nach der Formel Vdiff =V1 - V2 . Die Anzahl der Gleichtaktsignale bezieht sich auf die Hälfte der Summe zweier Signale nach folgender Formel  . Daher führt die Spannungsänderung einer einzelnen Leitung durchaus zur gleichzeitigen Beeinflussung von Gegentaktsignalen und Gleichtaktsignalen. Als nächstes wird eine Grafiksoftware angewendet, um mathematische Funktionsdiagramme zu zeichnen, um jeweils den Einfluss auf Gegentaktsignale und Gleichtaktsignale zu untersuchen. Zur Vereinfachung der Forschung können Signale analysiert werden, indem sie in eine trapezförmige Wellenform mit der gleichen oberen Zeit und der gleichen unteren Zeit simuliert werden.

. Daher führt die Spannungsänderung einer einzelnen Leitung durchaus zur gleichzeitigen Beeinflussung von Gegentaktsignalen und Gleichtaktsignalen. Als nächstes wird eine Grafiksoftware angewendet, um mathematische Funktionsdiagramme zu zeichnen, um jeweils den Einfluss auf Gegentaktsignale und Gleichtaktsignale zu untersuchen. Zur Vereinfachung der Forschung können Signale analysiert werden, indem sie in eine trapezförmige Wellenform mit der gleichen oberen Zeit und der gleichen unteren Zeit simuliert werden.

• Beeinflussung von Differenzsignalen

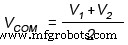

Das Anschlusssignal der positiven Phase, das Anschlusssignal der negativen Phase und das Differenzsignal von Differenzleitungspaaren sind in Abbildung 1 unten dargestellt, wobei die durchgezogene Linie für eine Differenzsignalwelle steht.

Wenn eine Phasenplatzierung vom positiven Phasenanschluss zum negativen Phasenanschluss stattfindet, wird es eine Änderung der Differenz zwischen dem positiven Phasenanschlusssignal und dem negativen Phasenanschlusssignal an der Aufwärts- oder Abwärtsflanke geben, und diese Änderung wird sich mit der Phasenänderung ändern. Tr wird verwendet, um für die kürzere Zeit zwischen ansteigender und abfallender Zeit zu stehen. Es kann angegeben werden, dass, wenn die Phasenplatzierung kleiner als Punkt zwei von Tr ist , ist die Signalverzerrung relativ gering und die Erhöhung der Phasenlage führt zu einer starken Verzerrung der differentiellen Wellenform. Wenn die Phasenplatzierung Tr überschreitet , wird ein nicht-monotoner Bereich auf der Wellenform stattfinden. Hier ist der nicht monotone Bereich eine Gerade. Bei praktischen Signalen können jedoch aufgrund von Reflexionen große Höhen und Tiefen im nicht monotonen Bereich auftreten, wobei sich Interferenzimpulse bilden, die zu Fehltriggerungen führen, was vermieden werden sollte. Außerdem wird die Oberkante der differentiellen Wellenform mit zunehmender Phasenlage langsam, was zu einer unzureichenden Einrichtungszeit für das Datensignal und zu einer unzureichenden Haltezeit für das Taktsignal führen kann.

• Beeinflussung des Gleichtaktsignals

Die Phasenlage des Einzelanschlusssignals hat keinen Einfluss auf die differentielle Wellenform, ändert jedoch die Wellenform von Gleichtaktsignalen. Wenn am positiven Anschlusssignal eine Phasenverschiebung stattfindet, findet eine Wellenänderung zu Gleichtaktsignalen statt. Es kann angegeben werden, dass der Schwankungsbereich mit dem Betrag der Phasenplatzierung zusammenhängt. Wenn der Betrag der Phasenplatzierung jeweils 0,05 Tr beträgt , 0,1Tr , 0,2Tr und 0,5Tr beträgt der Schwankungsbereich des Gleichtakts jeweils 5 %, 10 %, 20 % und 50 % des ursprünglichen Schwankungsbereichs. Wenn die Phase auf Tr ansteigt oder mehr, steigt die Schwankung auf etwa 100 % an, das ist die höchste Schwankungsbreite. Die Änderung des Gleichtaktsignals kann zu EMI-Problemen führen, und da das Gleichcodesignal unter vielen Bedingungen nicht am Terminal empfangen wird, bildet sich am Empfangsterminal eine Reflexion, die zu einem Signalklingeln führt. Daher sollte der Schwankungsbereich des Gleichtaktsignals so weit wie möglich verringert werden.

Zusammenfassend kann eine zu große relative Verzögerung zwischen differentiellen Paaren ein falsches Auslösen von Signalen, Signalreflexion, EMI und Zeitablaufprobleme verursachen. Jedoch hängt der Einflussgrad des relativen Verzögerungssignals von dem Skalierungsfaktor ab, der mit dem Signal Tr kompatibel ist . Wenn der Skalierungsfaktor 0,05 beträgt, kann die Verzerrung von Differenzsignalen fast ignoriert werden. Bei Gleichtaktsignalen jedoch, wenn der Skalierungsfaktor 0,05 beträgt, kann die Spannungsschwankung von Gleichtaktsignalen auf ungefähr 5 % gesteuert werden. Dann beträgt selbst bei vollständiger Reflexion die auf Signalleitungen gestapelte Reflexionsspannung nur 10 % der ursprünglichen Schwankung, was normalerweise ein akzeptabler Wert ist. Daher kann im Prozess des Hochgeschwindigkeits-PCB-Designs die relative Verzögerung der differentiellen Signalleitung in den Routing-Regulierungsregeln auf 0,05 T r eingestellt werden die in der Lage ist, die Anforderung der Signalintegrität zu erfüllen.

Bestimmung der relativen Verzögerungskategorie

Basierend auf der obigen Analyse liegt der Schlüssel zur Bestimmung der differentiellen isometrischen Kategorie, d. h. der Bestimmung der relativen Verzögerung von differentiellen Paaren, in der Bestimmung von Tr bezieht sich auf den kleinsten Wert unter der oberen und unteren Zeit von Differenzsignalen. Die Ausgabe der Anstiegszeit und Abfallzeit ist eigentlich die Ausgabe der Kombination aus Impedanz und Kapazität. Daher ist die Anstiegs-/Abfallzeit ohne Belastung tatsächlich eine inhärente Anstiegs-/Abfallzeit.

Die folgenden drei Methoden können angewendet werden, um den Wert von Tr zu erhalten :

• Die Anstiegs-/Abfallzeit kann direkt den Komponentenhandbüchern entnommen werden. In den meisten Situationen wird dieser Parameter jedoch nicht bereitgestellt.

• Wert von Tr kann aus Ramp-Schlüsselwörtern aus dem Komponenten-IBIS-Modell (Input/Output Buffer Informational Specification) erhalten werden. Parameter der Anstiegs-/Abfallzeit unter den Schlüsselwörtern Rampe werden im Allgemeinen am Ausgangsport gemessen, der mit einem Widerstand von 50 Ω verbunden ist, was normalerweise 20 % bis 80 % der endgültigen Spannungszeit ausmacht. Da die Parameter ohne Berücksichtigung des Einflusses des Pakets erhalten werden, ist es für uns strikt, die Anstiegs-/Abfallzeit als Wert von Tr zu verwenden .

• Der Wert von Tr kann gemäß der minimalen Taktfrequenz oder maximalen Taktfrequenz von Ausgangssignalen abgeschätzt werden. Da die distributive Anstiegsflanke in den meisten digitalen Hochgeschwindigkeitssystemen ungefähr 10 % der Taktfrequenz beträgt, ist der Wert von Tr kann mit der bereitgestellten minimalen Taktperiode Tclk geschätzt werden, basierend auf der Formel:Tr =Tclk x 10 %.

Der durch die Taktperiode erhaltene geschätzte Wert ist normalerweise streng, da parasitäre Parameter des Gehäuses oder das Laden von Komponenten die inhärente Anstiegs-/Abfallzeit in Transistoren stark verlangsamen.

In der praktischen Arbeit liefern Schaltungsdesigner in den meisten Situationen keine Informationen über Tr an PCB-Layout-Ingenieure, die nur einige mehrdeutige Anforderungen in Bezug auf die differenzielle isometrische Kontrolle erhalten. Das dritte Verfahren bietet zweifellos ein einfaches Schema für PCB-Layout-Ingenieure, solange die höchste Taktfrequenz auf der Signalleitung erhalten wird. Die höchste Taktfrequenz gilt als zuverlässigster Designparameter für Schaltungsdesigner und wird den PCB-Layout-Ingenieuren normalerweise zu Beginn des PCB-Designs mitgeteilt.

Die dritte Methode führt normalerweise zu einer Liste von Referenzwerten innerhalb der relativen Verzögerungssteuerungskategorie zwischen differentiellen Paaren, wie in der folgenden Tabelle gezeigt.

| Taktfrequenz/ns | Taktfrequenz/MHz | Relative Verzögerungskategorie/ps | Übertragungsleitungslänge/mil |

| 3,75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2.5 | 400 | 12.5 | 70 |

| 1,87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1,25 | 800 | 6.3 | 35 |

Simulationsüberprüfung

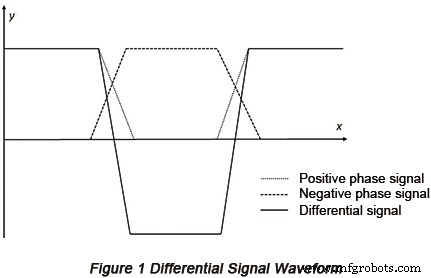

Nehmen Sie als Beispiel das DQS (Data Strobe)-Differenzsignal zwischen TSM320 und MT41J256M16. Die Cadence-Simulationssoftware wird angewendet, um das DOS-Signal an den DRR3-Speicher zu übertragen, um den Speichersteuerchip zu simulieren, seinen Einfluss auf die Haltezeit des Datensignalaufbaus zu analysieren und die obige Analyse zu überprüfen. Die Simulationsschaltung ist in Abbildung 2 unten dargestellt.

Basierend auf Abbildung 2 beträgt die Referenzspannung der Ausgangspins 1,5 V; Der Speichersteuerchip ist über den ODT-Modus (On-Die Termination) mit einer Übertragungsleitung von 800 mil direkt mit dem Speicherchip verbunden. Die Differenzimpedanz beträgt 100 Ω und die Simulationstaktfrequenz 800 MHz. Eine Übertragungsleitung von 50 Ω ist seriell mit dem positiven Phasenanschluss des DQS verbunden, um das Diskrepanzphänomen von Differentialpaaren zu simulieren. Bei isometrischen Differenzen beträgt die Länge der einpoligen Übertragungsleitung von 50 Ω 0 mil.

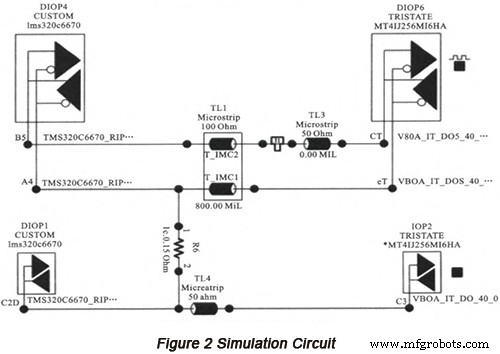

Die Simulation wird an der differentiellen isometrischen Schaltung durchgeführt. Fig. 3 veranschaulicht das Ausgangssignal am positiven Phasenanschluss von Differenzsignalen. Durch Messung beträgt die Anstiegszeit ungefähr 216 ps, während die Abfallzeit 219 ps beträgt, also die minimale Anstiegs-/Abfallzeit Tr sollte 216ps sein.

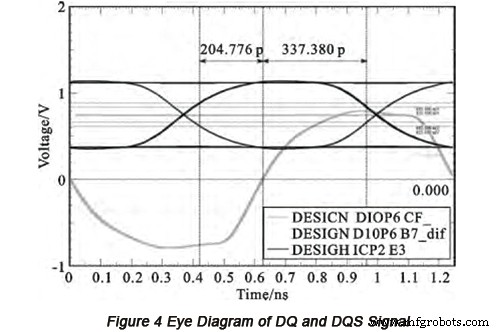

Fig. 4 ist ein Augendiagramm des Datensignals DQ und des Gating-Signals DQS durch Simulation mit der Aufbauzeit 205 ps und der Haltezeit 337 ps. Gemäß der Turnover-Rate von DQS- und DQ-Signalen durch Simulation und basierend auf dem Datenhandbuch muss die minimale Aufbauzeit von Datensignalen durch das empfangende Endgerät 85 ps und die minimale Haltezeit 95 ps betragen. Daher beträgt das Übermaß der Mindestaufbauzeit 120 ps und der Haltezeit 242 ps.

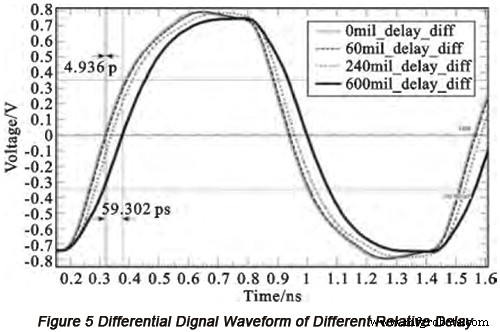

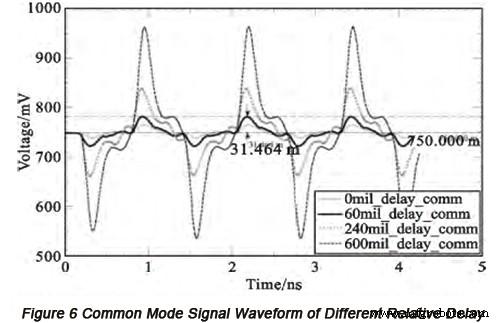

Die Situation der Existenz von 0,05Tr Phasenplatzierung, 0,2Tr Phasenplatzierung und 0,5Tr Phasenlage am positiven Phasenanschluss muss berücksichtigt werden. Die Schaltung kann mit einer Einzelanschluss-Übertragungsleitungslänge simuliert werden, die jeweils auf 60 mil, 240 mil und 600 mil eingestellt ist. Differentialsignalwellenform und Gleichtaktsignalwellenform durch viermalige Simulation sind in Abbildung 5 und 6 dargestellt.

Basierend auf Abbildung 5 ist die Verzerrung das Minimum bei relativen Verzögerungen von 0,05Tr und 0,2Tr stattfinden. Besonders wenn die relative Verzögerung 0,05Tr beträgt , nur Platzierung von etwa 5 ps von Differenzsignal zu Differenzsignalwellenform ohne relative Verzögerung, so dass die Datensignalaufbau-Übermessung um etwa 5 ps erhöht wird, wobei die Halte-Übermessungszeit um 5 ps verringert wird. Obwohl die Halte-Übermesszeit verringert wird, ist diese Platzierungsmenge so gering für die Haltezeit von 242 ps. Eine zeitliche Abfolge kann vermieden werden. Für die Situation, wenn die relative Verzögerung 0,5 Tr beträgt , hat die Platzierung der DQS-Signalwellenform etwa 60ps erreicht. Obwohl diese Platzierung immer noch in die Kategorie der Übermessung fällt, sollte ihr ausreichend Aufmerksamkeit geschenkt werden.

Basierend auf Abbildung 6 führt die Zunahme der Phasenlage zu einer offensichtlichen periodischen Schwankung auf Wellen und einer allmählichen Zunahme der Reichweite. Wenn die relative Verzögerung jeweils 0,05 Tr beträgt , 0,2Tr und 0,5Tr , beträgt der gemessene Spitzenwert des Gleichtaktsignals jeweils 61 mV, 176 mV und 430 mV, wobei der höchste Wert das Siebenfache des niedrigsten ist. Die größte Schwankungsbreite beträgt jeweils 4,3 %, 12 % und 29 %.

Zusammenfassend lässt sich sagen, dass das Simulationsergebnis mit dem Ergebnis kompatibel ist, das durch die mathematische Funktionsdiagrammanalyse erhalten wurde. Wenn die relative Verzögerung zwischen differentiellen Paaren weniger als 0,05 Tr beträgt , der Einfluss auf Signale ist recht gering.

Die minimale Taktperiode des Ausgangssignals am Ausgangsanschluss wird angewendet, um die relative Verzögerungssteuerkategorie abzuschätzen. Basierend auf dem Komponentenhandbuch beträgt die minimale Taktperiode der Komponenten 1,25 ns bei einer Taktfrequenz von 800 MHz. Gemäß Tabelle 1 sollte die relative Verzögerung bei einer Übertragungsleitungslänge von 35 mil innerhalb von 6,3 ps gesteuert werden. Anscheinend ist dieser Wert viel kleiner als die Kontrollkategorie der relativen Verzögerung von 0,05 Tr durch Simulation. Daher ist die geschätzte Steuerkategorie der relativen Verzögerung relativ konservativ, was spezifischer ist als das simulierte Ergebnis.

Hilfreiche Ressourcen

• Forschung zum Hochgeschwindigkeits-PCB-Design in eingebetteten Anwendungssystemen

• Wie man Bildebenen für Hochgeschwindigkeits-PCBs entwirft

• Hochgeschwindigkeits-PCB-Design-Herausforderungen zur Signalintegrität und ihre Lösungen

• PCB-Simulation mit OrCAD PSpice

• PCB-Fertigungsservice mit vollem Funktionsumfang von PCBCart – Mehrere Mehrwertoptionen

• Erweiterter PCB-Montageservice von PCBCart – ab 1 Stück

Industrietechnik

- Richtlinien für das HF- und Mikrowellendesign

- PCB-Materialien und Design für Hochspannung

- Flex- und Starrflex-Biegefähigkeiten im PCB-Design

- Schritte und Verfahren zum Schutz Ihres PCB-Designs

- Rückschläge und Lösungen im HF-PCB-Design

- 3 Routing-Techniken beim PCB-Design von Hochgeschwindigkeits-Signalschaltungen

- Hochgeschwindigkeits-Layout-Tipps

- Unterdrückungsmethode der Signalreflexion im Hochgeschwindigkeits-PCB-Layout

- Diskussion über Strom und Masse bei der elektromagnetischen Kompatibilität von PCB

- Signalintegritätsanalyse und PCB-Design auf gemischten Hochgeschwindigkeits-Digital-Analog-Schaltkreisen