Wie man Verarbeiter vertrauenswürdig macht

Moderne integrierte Schaltkreise (ICs) bieten die Rechen- und Systemsteuerungsfähigkeiten, um enorme Datenmengen zu verarbeiten, sicherheitskritische Entscheidungen in Echtzeit zu treffen und sensible Daten zu schützen. Das Entwerfen einer anwendungsspezifischen integrierten Schaltung (ASIC) oder eines feldprogrammierbaren Gate-Arrays (FPGA) System-on-Chip (SoC) von Grund auf wäre unerschwinglich teuer und zeitaufwendig. Viele kritische Funktionen werden unter Verwendung von geistigem Eigentum (IPs) von Drittanbietern implementiert. Prozessorkerne zum Beispiel werden von spezialisierten Organisationen bezogen und bieten durch ihre Befehlssatzarchitektur (ISA), die die Schnittstelle zwischen Hardware und Software definiert, eine flexible, softwareprogrammierbare Funktion. Open-Source-Prozessorarchitekturen bieten die Möglichkeit einer eingehenderen Prüfung und rigorosen Sicherheitsgewährleistung in Systemen, die bereits einer fließenden Bedrohungsumgebung ausgesetzt sind. Dieser Artikel beschreibt einen Ansatz zur Gewährleistung der Sicherheit von IP und SoCs basierend auf der RISC-V Open-Source-ISA.

RISC-V wurde an der University of California erfunden und von der gemeinnützigen RISC-V Foundation verwaltet und ist die erste Open-Source-ISA, die zu einer wirklich praktikablen industriellen Wahl für eine breite Palette von Anwendungen wird.

RISC-V ist ein Open-Source-ISA, das an der University of California erfunden wurde und von der RISC-V Foundation verwaltet wird, einer gemeinnützigen Organisation mit über 300 Mitgliedern, die 2015 gegründet wurde. RISC-V ist die erste Open-Source-ISA, die a eine wirklich praktikable industrielle Wahl für ein breites Anwendungsspektrum. Das Ökosystem aus Tools, Software und Know-how ist robust und wächst stetig. Viele Einzelpersonen und Organisationen haben bereits Open-Source-Hardware-IPs gespendet, die die RISC-V ISA implementieren. Die OpenHW-Gruppe beispielsweise möchte die lang ersehnte Aussicht auf Open-Source-Hardware – insbesondere Prozessorkerne – für High-Volume-Chips Wirklichkeit werden lassen.

Der Aufstieg von RISC-V hat viele Gründe. RISC-V wurde von Grund auf unter Berücksichtigung der benutzerdefinierten Erweiterbarkeit entwickelt und ermöglicht eine neue Ebene der Hardwareoptimierung für bestimmte Workloads. Das Mooresche Gesetz verlangsamt sich, und die Anpassung ist entscheidend, um die Leistungsverbesserungen aufrechtzuerhalten, die technologische Fortschritte im Halbleiterherstellungsprozess nicht mehr bieten können. Darüber hinaus ist die RISC-V-Architektur frei von Lizenzkosten und Lizenzgebühren, was es mehr Unternehmen ermöglicht, innovative, erschwingliche Produkte zu entwickeln. Viel passiert zum Beispiel im Bereich IoT und tragbare Geräte mit Fähigkeiten der künstlichen Intelligenz.

SoC-Integratoren verwenden häufig Open-Source- oder RISC-V-Prozessor-IPs von Drittanbietern. Diese Designs und die dazugehörigen Toolchains können mit benutzerdefinierten Anweisungen erweitert werden. Eine hochwertige Verifizierungsumgebung, die mit dem IP geliefert wird, und zusätzliche Tests auf Systemebene können eine gewisse Sicherheit vermitteln, dass das IP keine kritischen Fehler aufweist. Leider reicht dies für viele Anwendungen nicht aus und es sind andere ernsthafte Risiken zu berücksichtigen.

Sicherheitslücken und Trojaner

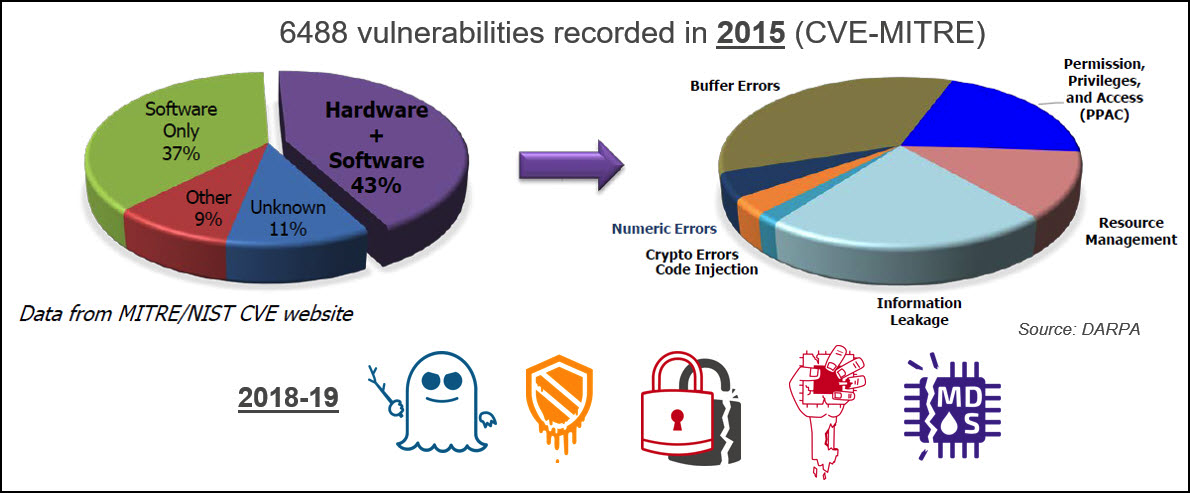

Traditionell wurden Sicherheitslücken in elektronischen Systemen mit Problemen auf Systemebene und Software in Verbindung gebracht. In jüngerer Zeit sind auch Hardware-IPs, vor allem Prozessoren, zu einem zentralen Anliegen geworden (siehe Abb. 1). Prozessorimplementierungen verwenden Pipeline-basierte Mikroarchitekturen und umfassen häufig Leistungs- und Leistungsoptimierungsfunktionen. Komplexität erhöht das Risiko, nicht nur funktionale Fehler, sondern auch Sicherheitslücken zu übersehen. Die Sicherheitsforscher, die Anfang 2018 die Angriffe Meltdown und Spectre entdeckt haben, haben gezeigt, dass Leistungsoptimierungsfunktionen in Prozessoren unbeabsichtigt für schändliche Zwecke verwendet werden können. Seitdem wurden viele weitere Schwachstellen in High-End- und Low-End-Prozessoren entdeckt. Seitenkanäle und Angriffe mit vorübergehender Ausführung können sichere Enklaven durchbrechen und böswilligen Anwendungen ermöglichen, vertrauliche Daten zu verlieren oder sogar die Kontrolle über das System zu übernehmen. Und im Gegensatz zu Software können Hardwareprobleme nicht einfach mit Over-the-Air-Updates behoben werden. Die Behebung eines Hardwareproblems durch Software führt oft zu schwerwiegenden Leistungseinbußen.

Die RISC-V-Architektur verfügt über viele Funktionen, die die Implementierung sicherer eingebetteter Systeme unterstützen. Die Berechtigungsspezifikation definiert beispielsweise vier Berechtigungsmodi (Maschine, Supervisor, Hypervisor und Benutzer). Benutzerdefinierte Anweisungen und ISA-Erweiterungen, die gerade ratifiziert werden, wie die kryptografische Erweiterung, bieten zusätzliche Sicherheitsfunktionen. Designer können mehrere sichere Enklaven implementieren, um Anwendungen zu isolieren und den Verlust sensibler Daten zu verhindern. Allerdings können RTL-Mikroarchitekturfunktionen immer noch zu Sicherheitslücken führen. Diese Risiken können auf ISA-Ebene nicht vollständig angegangen werden. Ein neuer Ansatz, der untersucht wird, ist die Verwendung einer erweiterten ISA (aISA), um Aspekte der Befehlsausführung auf der Mikroarchitekturebene zu definieren und beispielsweise den Zustand von Puffern oder Registern zu steuern, die auf der ISA-Ebene nicht sichtbar sind. RTL-Funktionsfehler können all diese Sicherheitsfunktionen immer noch beeinträchtigen.

Ein weniger wahrscheinliches Risiko, aber mit einem viel höheren Schweregrad, ist das Vorhandensein von bösartiger Logik oder Hardware-Trojanern im RISC-V-Kern. Ein Hardware-Trojaner ist eine bewusst heimlich konzipierte Logikfunktion, die in sehr seltenen Fällen aktiviert wird, die nur dem Angreifer bekannt sind. Eine bestimmte Abfolge von Daten- und Kontrollereignissen, die während des Systembetriebs in seinen Zielanwendungsfällen nicht eintreten würden, löst die Trojaner-Logik aus, die wiederum eine schädliche Nutzlast liefert, beispielsweise ein Geheimnis preisgibt oder das Systemverhalten kritisch korrumpiert. SoC-Integrationen, die Open-Source- oder RISC-V-Kerne von Drittanbietern verwenden, können dieses Risiko nicht länger ignorieren.

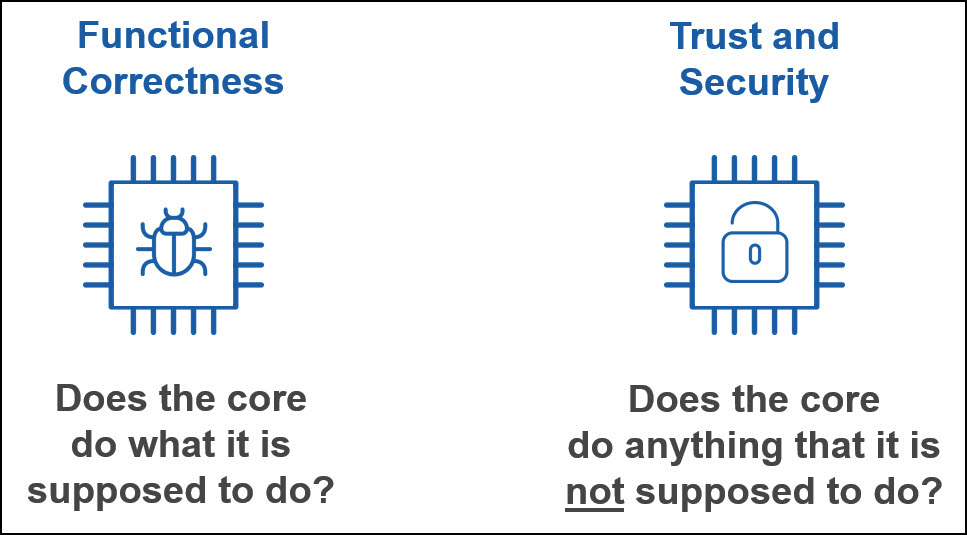

Sicherzustellen, dass ein Prozessor tut, was er tun soll, ist schwer, aber sicherzustellen, dass er nichts tut, was er nicht tun soll, ist eine noch anspruchsvollere Aufgabe, die noch weitgehend ungelöst ist. Sicherheitskritische Systeme und Systeme, bei denen der Schutz der Privatsphäre von größter Bedeutung ist, benötigen effiziente, qualitativ hochwertige Lösungen, die das Risiko von Sicherheitslücken und Trojanern beseitigen.

Abbildung 1:Die CVE-MITRE-Datenbank verzeichnete im Jahr 2015 6488 Schwachstellen, von denen 43 % als softwaregestützte Hardware-Schwachstellen klassifiziert werden können. In den Jahren 2018 und 2019 haben Forscher zahlreiche Schwachstellen in Prozessoren entdeckt und gemeldet, darunter Meltdown und Spectre, Foreshadow, ZombieLoad sowie RIDL und Fallout. (Quelle:DARPA und OneSpin)

Smart Hardware Assurance

Um das Vertrauen und die Sicherheit von RISC-V-IPs zu gewährleisten, sind innovative und effiziente technische Lösungen erforderlich, die funktionale Korrektheitsansätze ergänzen und hauptsächlich auf die beabsichtigten IP-Anwendungsfälle abzielen (siehe Abb. 2). IP-Anbieter sind für die Anwendung modernster Vertrauens- und Sicherheitsverifizierungsprozesse verantwortlich, während IP-Integratoren Zugang zu unabhängigen Assurance-Lösungen haben sollten, die schnell und ohne eingehende Kenntnisse der IP-Implementierungsdetails bereitgestellt werden können.

Formale Methoden können Hardwarefunktionen umfassend analysieren und den Beweis liefern, dass das IP oder SoC genau einem erwarteten Verhalten entspricht, das oft in SystemVerilog-Assertionen erfasst wird. Die formale Hardwareverifizierung mit kommerziellen Modellprüfern hat in den letzten zehn Jahren eine breite Akzeptanz gefunden. Typischerweise haben IP-Provider und SoC-Integratoren formelle Verifikationsexperten in ihren Reihen, die versuchen, das Risiko, funktionale Fehler zu verpassen, auf ein Minimum zu reduzieren. Während bestimmte gut definierte formale Verifizierungsaufgaben durch Apps automatisiert werden können , im Allgemeinen ist ein erheblicher technischer Aufwand erforderlich, um das erwartete Verhalten des geistigen Eigentums in Behauptungen zu erfassen. Darüber hinaus gibt es keine Garantie dafür, dass genügend Behauptungen geschrieben wurden. Nicht dokumentierte Funktionen oder unbeabsichtigte Lücken im Satz von Behauptungen können zu nicht überprüfter IP-Funktionalität führen.

Der Open-Source-Charakter von RISC-V ermöglicht die Entwicklung vorgefertigter, unabhängiger Assurance-Lösungen. Die RISC-V Integrity Verification Solution von OneSpin kann beispielsweise auf eine Vielzahl von Mikroarchitekturen angewendet werden. Es umfasst Modelle der RISC-V ISA und privilegierten ISA, die erweiterbar sind und benutzerdefinierte Anweisungen aufnehmen können. Ein entscheidender Aspekt dieser Lösung ist, dass sie auf dem GapFreeVerification™-Prozess von OneSpin basiert, der einen rigorosen Beweis dafür liefert, dass der Satz von Behauptungen, die den RISC-V-ISA modellieren, vollständig und lückenlos ist. Dieser Aspekt ist von größter Bedeutung, wenn die Erkennung von Hardware-Trojanern oder undokumentierter Logik ein entscheidendes Ziel ist. Die Lösung ermöglicht es SoC-Integratoren mit begrenztem Fachwissen zu RISC-V und der RTL-Implementierung, die geprüft wird, Vertrauen in die Qualität und Vertrauenswürdigkeit des geistigen Eigentums zu gewinnen. IP-Entwickler können damit Sicherheitslücken und Funktionsfehler vor der Veröffentlichung erkennen.

Abbildung 2:Die Überprüfung der funktionalen Korrektheit schafft Gewissheit, dass sich eine Prozessorimplementierung wie angegeben verhält und die Anforderungen der Endbenutzer erfüllt. Die Vertrauens- und Sicherheitsüberprüfung hingegen schafft die Gewissheit, dass der Prozessor keine undokumentierten Funktionen, unvorhergesehenen Seitenkanäle, Hardware-Trojaner oder andere Schwachstellen hat, die von böswilligen Akteuren ausgenutzt werden könnten. (Quelle:OneSpin)

Funktioniert es?

Der im vorherigen Abschnitt beschriebene RISC-V-Integritätssicherungsprozess wurde erfolgreich auf mehrere RTL-Designs angewendet. Edaptive Computing, ein Unternehmen, das innovative Lösungen zur schnellen Optimierung, Sicherung und Automatisierung von System- und Prozesssystemen für eine Vielzahl von Kunden des US-Verteidigungsministeriums und des kommerziellen Sektors integriert, hat das Verfahren beispielsweise auf den RocketCore angewendet. Der RocketCore ist ein quelloffener, siliziumerprobter 64-Bit-RISC-V-Kern mit einem virtuellen 39-Bit-Speichersystem. Es verfügt über eine fünfstufige, geordnete Pipeline mit einer Ausgabe und einer nicht in der Reihenfolge ausgeführten Vervollständigung für Befehle mit langer Latenz, wie z. B. Division. Es enthält die erweiterten Funktionen der Verzweigungsvorhersage und der Befehlswiedergabe.

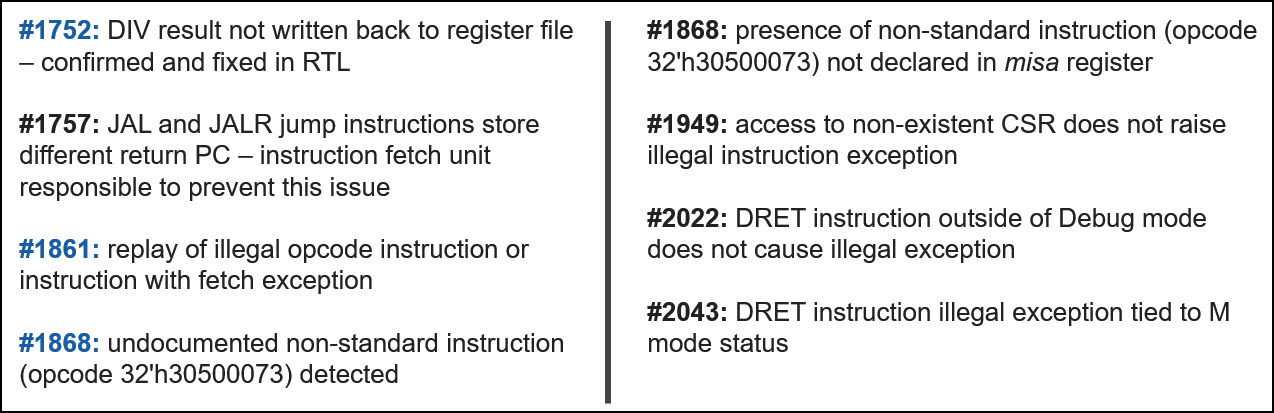

Die RISC-V Integrity Verification Solution wurde mit allen Anweisungen, Berechtigungsstufen, Interrupts und Ausnahmemechanismen auf das Design angewendet, und es wurden 8 Probleme erkannt (siehe Abb. 3). Weitere Informationen zu 3 davon sind unten aufgeführt.

Divisions-Eckkoffer :ein tiefer Eckfallfehler, der mit der Beendigung des Divisionsbefehls außerhalb der Reihenfolge verbunden ist. Dieses Problem könnte dazu geführt haben, dass ein Softwareprogramm, das die Divisionsoperation verwendet, falsche Ergebnisse berechnet und zu einem Fehlverhalten des Systems führt. Das Problem tritt nur unter einer Kombination seltener Umstände auf, weshalb es bei früheren Überprüfungsbemühungen übersehen wurde.

Wiedergabe illegaler Anweisungen :Dies ist kein Corner-Case-Bug. Das Wiederholen eines unzulässigen Befehls kann Verarbeitungszyklen verschwenden, aber wenn dies nur in seltenen Situationen passiert, ist die Auswirkung auf die Leistung vernachlässigbar. Es sind jedoch noch andere Aspekte zu berücksichtigen. Die Befehlswiedergabe kann unnötige Speicheranforderungen verursachen. Diese Anforderungen können Nebenwirkungen haben, die bei Seitenkanalangriffen ausgenutzt werden könnten. Daher muss dieses Verhalten entweder beseitigt oder klar verstanden und dokumentiert werden.

Undokumentierte Anweisung :Eine undokumentierte, nicht standardmäßige Anweisung namens CEASE, die den Kern stoppt, wurde erkannt. Tatsächlich konnte der RISC-V RocketCore etwas tun, was es nicht tun sollte. Undokumentierte, versteckte Funktionen sind nicht akzeptabel, wenn Vertrauen und Sicherheit ein Anliegen sind, selbst wenn sie sich auf Anwendungsfälle beziehen, die für die Endanwendung als nicht relevant erachtet werden.

Die RocketCore-Fallstudie wird im GOMACTech 2019-Papier mit dem Titel Complete Formal Verification of RISC-V Processor IPs for Trojan-Free Trusted ICs ausführlich vorgestellt. Um eine Kopie zu erhalten, besuchen Sie onespin.com/resources/white-papers.

Abbildung 3:Liste der Probleme, die von OneSpins RISC-V-Integritätsprüfungslösungen erkannt und im GitHub RocketCore-Projekt gemeldet wurden. (Quelle:OneSpin)

Wie geht es weiter?

Der in diesem Artikel vorgestellte RISC-V-Assurance-Prozess erkennt Szenarien, die die Sicherheit beeinträchtigen könnten, und deckt systematisch undokumentierte Funktionen und Hardware-Trojaner auf, die das Verhalten des Prozessors beeinträchtigen, unabhängig davon, wie selten und heimlich sie sind. Seitenkanäle werden jedoch nicht systematisch erkannt. Eine umfassende Erkennung aller potentiellen Seitenkanäle erfordert eine dedizierte Lösung mit entsprechender Technologie. Es gibt bereits Prototypen, die sich dieser Herausforderung stellen. Weitere Informationen finden Sie unter onespin.com/resources/technical-articles und lesen Sie den Artikel der EE Times Seitenkanalangriffe auf eingebettete Prozessoren.

Prozessorkerne sind wichtige IPs in eingebetteten Systemen. Ein typischer SoC integriert jedoch viele andere IPs, die auch Hardware-Trojaner enthalten können. Im Gegensatz zu RISC-V-Kernen sind unabhängige Vertrauenssicherungslösungen möglicherweise nicht ohne weiteres verfügbar. In diesem Fall wäre ein automatisierter Vertrauensbewertungsprozess mit geringem Aufwand für jedes geistige Eigentum von Vorteil. Ein Prozess, der kein vertrauenswürdiges Modell der IP enthält, kann die Abwesenheit eines Trojaners nicht gewährleisten. Es ist jedoch möglich, ungewöhnliche und verdächtige Codemuster und bekannte Trojaner-Signaturen sowie Schwachstellen zu identifizieren, die in späteren Entwicklungsstadien für schändliche Zwecke ausgenutzt werden könnten. Ein Artikel zu diesem Thema mit dem Titel An Automated Pre-Silicon IP Trustworthiness Assessment for Hardware Assurance , verfasst von AEROSPACE Corporation und OneSpin-Ingenieuren, wird auf der GOMACTech 2020-Konferenz vorgestellt.

Eingebettet

- So nutzen Sie Ihre Daten optimal

- Ein Leitfaden zum Beschleunigen von Anwendungen mit genau richtigen benutzerdefinierten RISC-V-Anweisungen

- So erstellen Sie eine Arduino+Raspberry Pi-Roboterplattform

- Wie man Glasfaser herstellt

- Wie man Lieferkettendaten vertrauenswürdig macht

- So erstellen Sie eine Cutaway-Animation in Solidworks

- So erstellen Sie einen Prototyp

- Ersetzen eines Hydraulikschlauchs

- Wie man ein umfassendes Sicherheitsprogramm zum Laufen bringt

- Wie man ein Drehfutter aus Metall herstellt