Embedded Design mit FPGAs:Erstellen eines Projekts

Anmerkung des Herausgebers:Da immer fortschrittlichere Algorithmen für intelligente Produktdesigns entstehen, haben Entwickler oft Schwierigkeiten, eingebettete Systeme zu implementieren, die die entsprechenden Verarbeitungsanforderungen dieser Algorithmen erfüllen. FPGAs können die erforderliche Leistung liefern, aber das Entwerfen mit FPGAs galt lange Zeit als auf FPGA-Programmierexperten beschränkt. Heute jedoch hat die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Entwicklungsumgebungen die FPGA-Entwicklung allgemein zugänglich gemacht. In diesem Auszug, Kapitel 4 aus dem Buch Architecting High-Performance Embedded Systems, bietet der Autor einen umfassenden Überblick über FPGA-Geräte, Implementierungssprachen und den FPGA-Entwicklungsprozess sowie eine detaillierte Anleitung, wie Sie mit der Implementierung eigener FPGAs beginnen können Entwurf. Der vollständige Auszug wird in der folgenden Reihe von Raten präsentiert:

Anmerkung des Herausgebers:Da immer fortschrittlichere Algorithmen für intelligente Produktdesigns entstehen, haben Entwickler oft Schwierigkeiten, eingebettete Systeme zu implementieren, die die entsprechenden Verarbeitungsanforderungen dieser Algorithmen erfüllen. FPGAs können die erforderliche Leistung liefern, aber das Entwerfen mit FPGAs galt lange Zeit als auf FPGA-Programmierexperten beschränkt. Heute jedoch hat die Verfügbarkeit leistungsfähigerer FPGAs und effektiverer Entwicklungsumgebungen die FPGA-Entwicklung allgemein zugänglich gemacht. In diesem Auszug, Kapitel 4 aus dem Buch Architecting High-Performance Embedded Systems, bietet der Autor einen umfassenden Überblick über FPGA-Geräte, Implementierungssprachen und den FPGA-Entwicklungsprozess sowie eine detaillierte Anleitung, wie Sie mit der Implementierung eigener FPGAs beginnen können Entwurf. Der vollständige Auszug wird in der folgenden Reihe von Raten präsentiert:

1:Hardwareressourcen

2:Implementierungssprachen

3:Entwicklungsprozess

4:Erstellen eines Projekts (dieser Artikel)

5:Implementierung

Adaptiert aus Architecting High-Performance Embedded Systems, von Jim Ledin.

Entwicklung Ihres ersten FPGA-Projekts

In diesem Abschnitt werden wir ein einfaches, aber vollständiges Projekt mit einem Xilinx Artix-7 FPGA-Gerät entwickeln und implementieren, das auf einem Digilent Arty A7-Entwicklungsboard installiert ist. Dieses Board ist in zwei Varianten erhältlich, einer kostengünstigeren Version (129 US-Dollar) mit einer Modellnummer, die auf -35T endet, und einer leistungsfähigeren, aber teureren Version (249 US-Dollar) mit einer Modellnummer, die auf -100T endet. Der einzige Unterschied zwischen den beiden Boards ist das auf dem Board verbaute Modell des Artix-7 FPGA. Erwartungsgemäß stehen dem -35T weniger Ressourcen zur Verfügung als dem -100T.

Sie können für dieses Projekt entweder die -35T- oder die -100T-Variante verwenden. Der einzige Unterschied im Entwicklungsprozess besteht darin, bei Bedarf das richtige Board-Modell zu spezifizieren. In späteren Kapiteln wird jedoch die -100T-Variante aufgrund der Ressourcenanforderungen des beispielhaften Digitaloszilloskop-Projektdesigns benötigt, daher wird die leistungsfähigere Platine empfohlen.

Die Arty A7-Boards können unter https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/ und bei anderen Quellen wie Amazon erworben werden.

Für die Zwecke dieses Projekts sind die Ressourcen auf dem interessierenden Board das FPGA-Gerät selbst sowie die vier Schalter, vier Drucktasten und fünf LEDs. Dieses Projekt zeigt, wie Sie die Vivado-Toolsuite installieren, ein Projekt erstellen, HDL-Code eingeben, den Code testen und schließlich einen Bitstream produzieren und auf das Board herunterladen. Nachdem Sie den Bitstream auf das Board heruntergeladen haben, können Sie den Betrieb des Systems manuell testen. Sie werden auch sehen, wie Sie das FPGA-Image in den Flash-Speicher des Arty A7-Boards programmieren, damit es jedes Mal geladen und ausgeführt wird, wenn das Board eingeschaltet wird.

Projektbeschreibung

Dieses Projekt wird einen Vier-Bit-Binäraddierer im FPGA implementieren. Dabei handelt es sich bewusst um ein sehr einfaches Design, da hier der Fokus auf dem Einrichten der Tools und dem Erlernen ihrer Verwendung liegt und nicht auf der Implementierung eines komplexen HDL-Modells.

Die vier Schalter auf der Platine repräsentieren eine 4-Bit-Binärzahl und die vier Drucktasten repräsentieren eine weitere 4-Bit-Zahl. Die FPGA-Logik führt kontinuierlich eine Additionsoperation zwischen diesen beiden Zahlen durch und zeigt das Ergebnis als 4-Bit-Binärzahl auf vier LEDs an, wobei eine fünfte LED das Übertragsbit darstellt.

Der 4-Bit-Addierercode basiert auf der Einzelbit-Volladdiererschaltung, die in den Hardware-Designsprachen . beschrieben ist Abschnitt von Kapitel 1 , Architektur leistungsstarker eingebetteter Systeme .

Installieren der Vivado-Tools

Wir werden die Xilinx Vivado Suite von FPGA-Entwicklungstools für dieses Projekt und für Projekte in zukünftigen Kapiteln verwenden. Diese Tools sind kostenlos erhältlich und werden auf Windows- und Linux-Betriebssystemen unterstützt. Sie können die Tools auf beiden Betriebssystemen installieren. Die Beschreibung in diesem Abschnitt behandelt die Windows-Version der Tools, aber wenn Sie unter Linux installieren, sollten die Unterschiede offensichtlich sein. Die Arbeit mit den Vivado-Tools sollte auf den verschiedenen Betriebssystemen nahezu identisch sein:

- Wenn Sie noch keins haben, erstellen Sie ein Xilinx-Benutzerkonto unter https://www.xilinx.com/registration/create-account.html.

- Besuchen Sie https://xilinx.com und melden Sie sich bei Ihrem Benutzerkonto an. Rufen Sie nach der Anmeldung die Tools-Download-Seite unter https://www.xilinx.com/support/download.html auf.

- Laden Sie das Xilinx Unified Installer:Windows Self-Extracting Web Installer herunter . Sie sollten wahrscheinlich die neueste verfügbare Version auswählen, aber wenn Sie der in diesem Buch verwendeten Version folgen möchten, wählen Sie Version 2020.1 .

- Die Installationsdatei hat einen ähnlichen Namen wie Xilinx_1_0602_1208_Win64.exe. Suchen Sie diese Datei in Ihrem Download-Verzeichnis und führen Sie sie aus. Wenn Sie in einem Dialogfeld gewarnt werden, eine App zu installieren, die nicht von Microsoft bestätigt wurde, klicken Sie auf Trotzdem installieren .

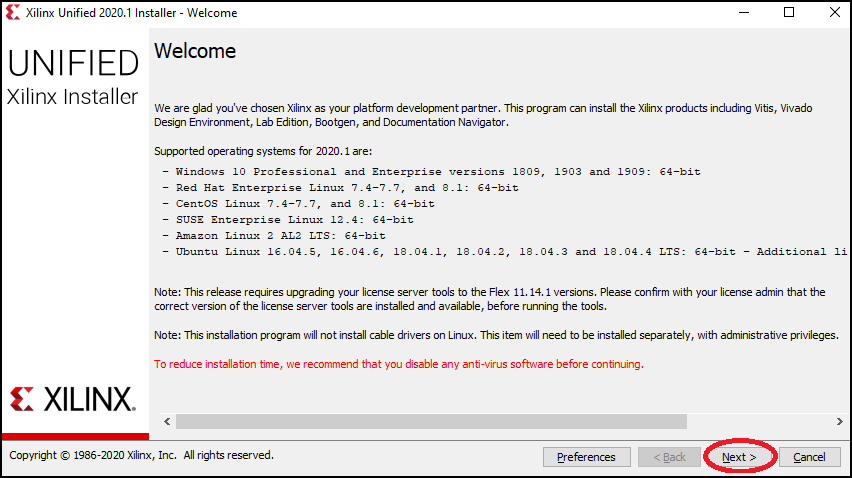

- Wenn das Willkommen Bildschirm erscheint, klicken Sie auf Weiter :

Abbildung 4.3 – Willkommensdialog des Installationsprogramms

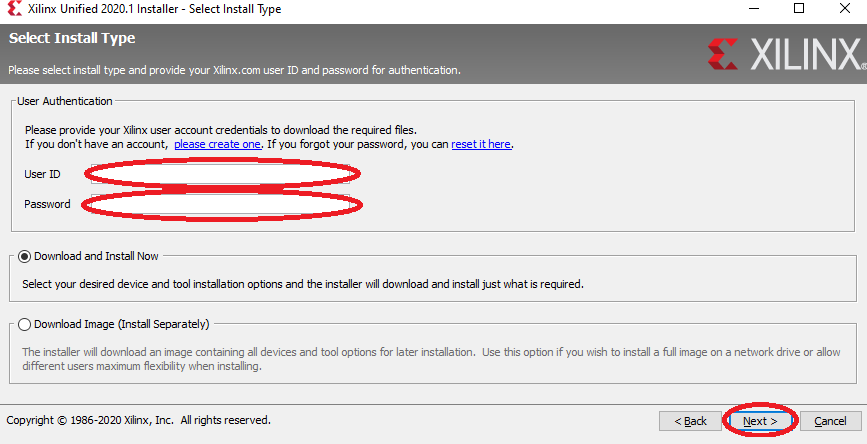

- Geben Sie auf dem folgenden Bildschirm Ihre xilinx.com-Benutzer-ID und Ihr Passwort ein und klicken Sie dann auf Weiter :

Abbildung 4.4 – Anmeldedialog des Installers

- Im nächsten Dialogfeld werden Sie aufgefordert, einige Lizenzvereinbarungen zu akzeptieren. Aktivieren Sie die Kästchen mit der Aufschrift Ich stimme zu , und klicken Sie dann auf Weiter .

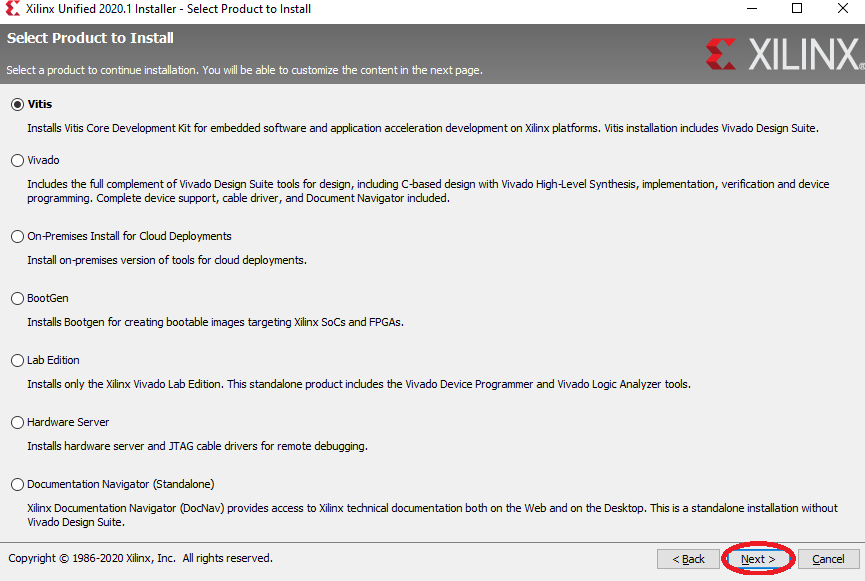

- Verlassen Sie im nächsten Dialog Vitis als zu installierendes Produkt ausgewählt und klicken Sie auf Weiter . Vitis enthält die Vivado-Toolsuite zusammen mit einer Sammlung anderer Xilinx-Entwicklungstools:

Abbildung 4.5 – Dialog zur Produktauswahl des Installers

- Im nächsten Dialog können Sie die zu installierenden Softwarekomponenten auswählen. Belassen Sie die Auswahl bei ihren Standardwerten und klicken Sie auf Weiter .

- Im nächsten Dialog können Sie ein Zielverzeichnis auswählen und Programmverknüpfungsoptionen angeben. Ein Zielverzeichnis von C:\Xilinx ist ein geeigneter Ort. Erstellen Sie dieses Verzeichnis, falls es nicht existiert. Klicken Sie auf Weiter .

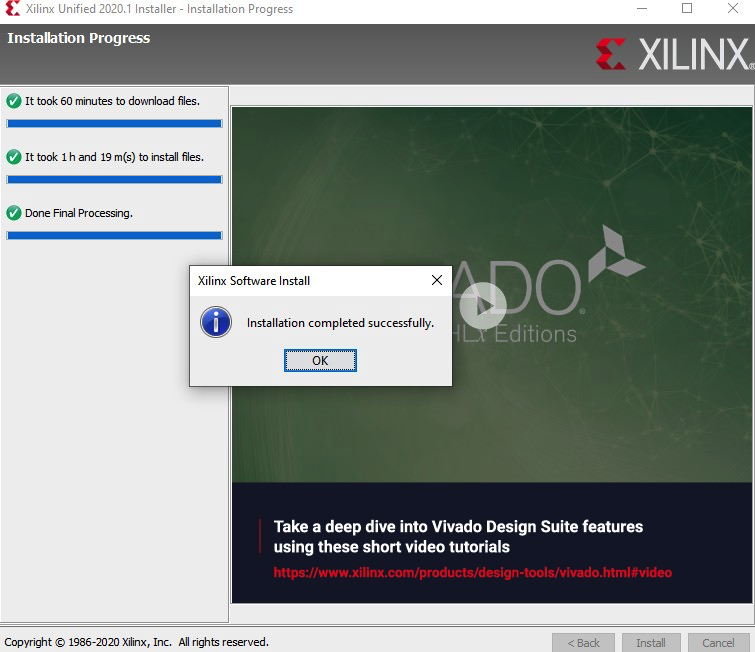

- Der nächste Dialog zeigt eine Zusammenfassung der Installationsoptionen. Klicken Sie auf Installieren um mit der Installation fortzufahren. Abhängig von der Geschwindigkeit Ihres Computers und Ihrer Internetverbindung kann die Installation einige Stunden dauern:

Abbildung 4.6 – Dialog Installation abgeschlossen

Nachdem die Installation abgeschlossen ist, erstellen wir als nächstes unser erstes Projekt.

Projekt erstellen

Befolgen Sie diese Schritte, um das 4-Bit-Binär-Addierer-Projekt für das Arty A7-Board zu erstellen und zu erstellen:

- Suchen Sie das Desktop-Symbol mit dem Titel Vivado 2020.1 (oder suchen Sie nach Ihrer Versionsnummer, falls abweichend) und doppelklicken Sie darauf.

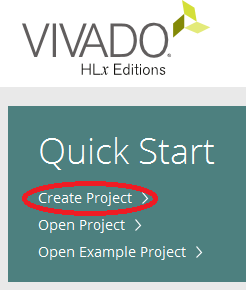

- Wenn Vivado seinen Hauptbildschirm anzeigt, klicken Sie auf Projekt erstellen in der Kurzanleitung Abschnitt:

Abbildung 4.7 – Vivado Schnellstart-Dialog

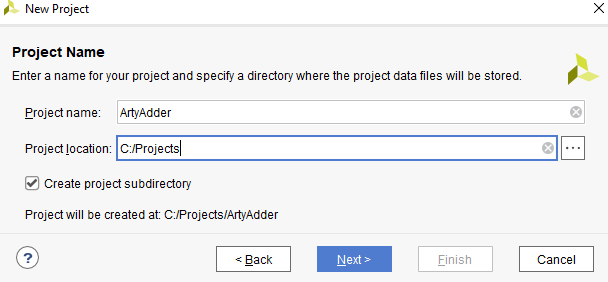

- Damit wird das Neue Vivado-Projekt erstellen gestartet Magier. Klicken Sie auf Weiter um den Projektnamen zu erreichen Seite und geben Sie ArtyAdder als Projektnamen ein. Wählen Sie einen geeigneten Verzeichnisspeicherort für das Projekt aus und aktivieren Sie das Kontrollkästchen, um ein Unterverzeichnis zu erstellen, und klicken Sie dann auf Weiter . Die Beispiele in diesem Buch verwenden das Verzeichnis C:\Projects als Speicherort für alle Projekte:

Abbildung 4.8 – Dialog Projektname

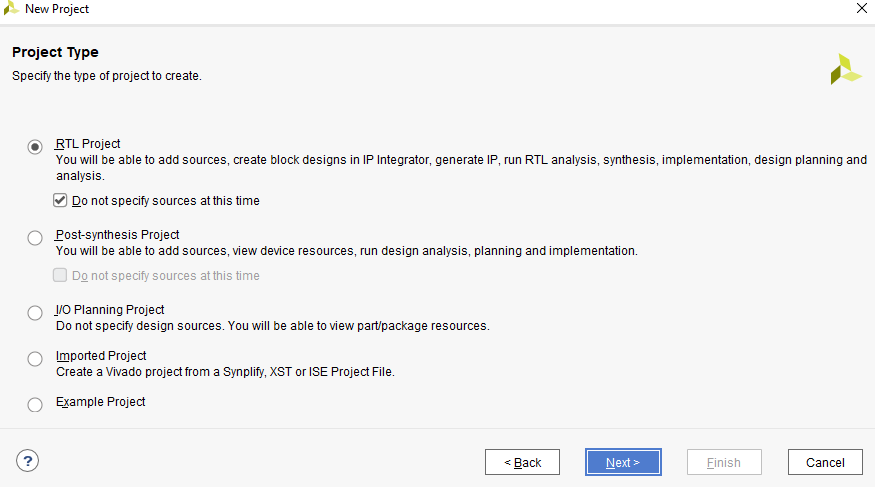

- Im Projekttyp Wählen Sie im Dialogfeld RTL-Projekt und aktivieren Sie das Kontrollkästchen neben Zu diesem Zeitpunkt keine Quellen angeben . Klicken Sie auf Weiter :

Abbildung 4.9 – Dialog Projekttyp

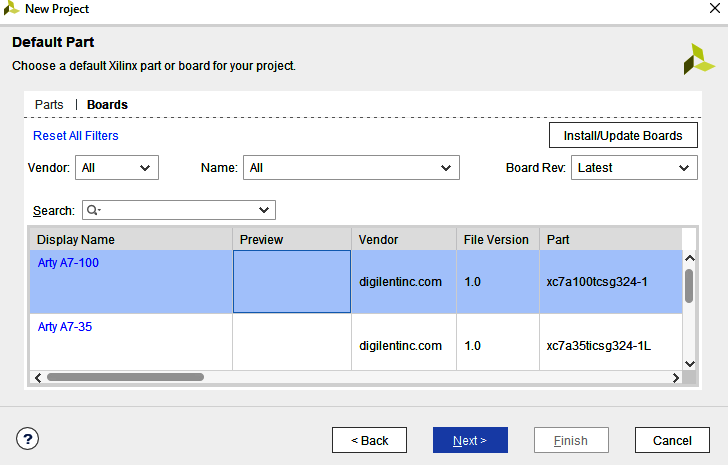

- Im Standardteil Klicken Sie im Dialogfeld auf Boards Tab und geben Sie Arty in die Suche ein Bereich. Wählen Sie je nach Board-Typ (oder wenn Sie noch kein Board haben) entweder den Arty A7-100 oder Arty A7-35 und klicken Sie auf Weiter :

Abbildung 4.10 – Dialog Standardteil

- In der Neuen Projektzusammenfassung Klicken Sie im Dialogfeld auf Fertig stellen .

Wir haben jetzt ein leeres Projekt erstellt. Im nächsten Abschnitt werden wir VHDL-Quelldateien erstellen, die das Logikschaltungsdesign für dieses Projekt enthalten.

VHDL-Quelldateien erstellen

Die folgenden Schritte beschreiben das Erstellen von VHDL-Quelldateien, die Eingabe von Quellcode und das Kompilieren des FPGA-Designs:

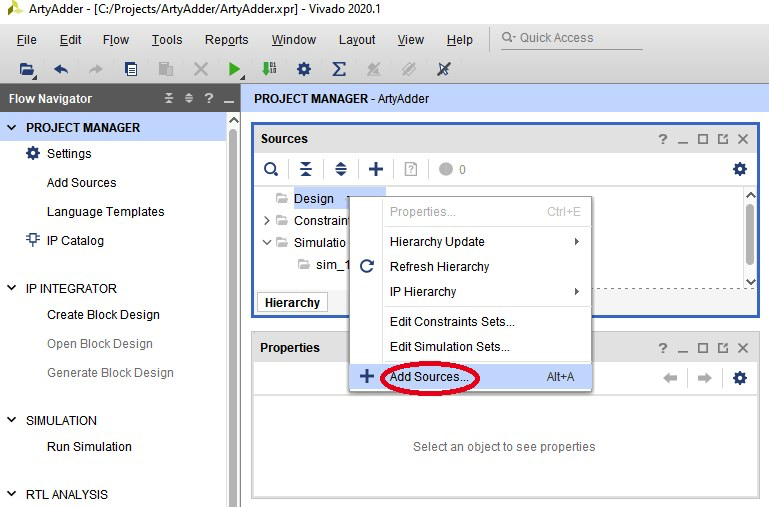

- In den Quellen Klicken Sie im Unterfenster mit der rechten Maustaste auf Designquellen und wählen Sie Quellen hinzufügen… :

Abbildung 4.11 – Quellen hinzufügen… Menüauswahl

- Im Quellen hinzufügen Dialog, vergewissern Sie sich, dass Designquellen hinzufügen oder erstellen ausgewählt ist, klicken Sie dann auf Weiter .

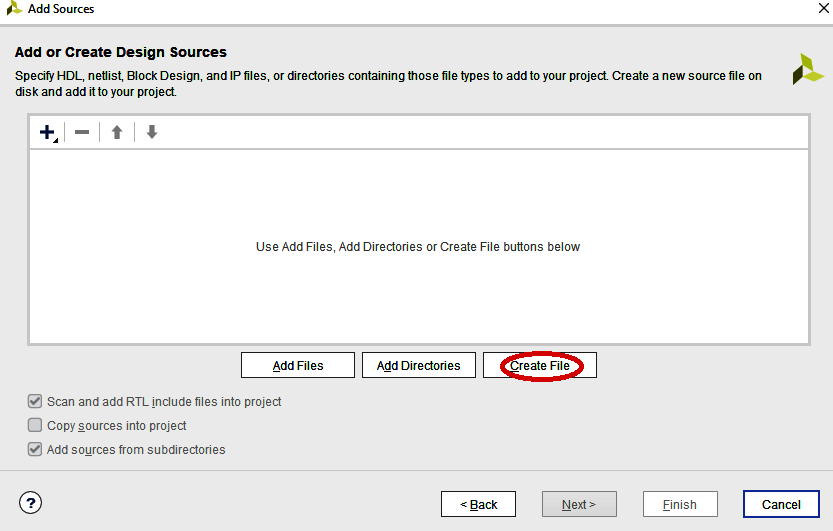

- Im Designquellen hinzufügen oder erstellen Klicken Sie im Dialogfeld auf Datei erstellen :

Abbildung 4.12 – Dialogfeld „Designquellen hinzufügen oder erstellen“

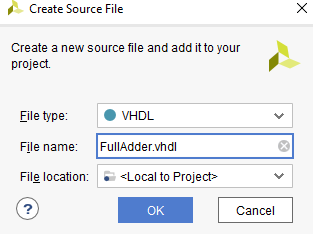

- Geben Sie den Dateinamen FullAdder.vhdl ein und klicken Sie auf OK :

Abbildung 4.13 – Dialogfeld „Quelldatei erstellen“

- Wiederholen Sie die beiden vorherigen Schritte, um eine weitere Datei namens Adder4.vhdl zu erstellen, und klicken Sie dann auf Fertig stellen im Designquellen hinzufügen oder erstellen Dialog.

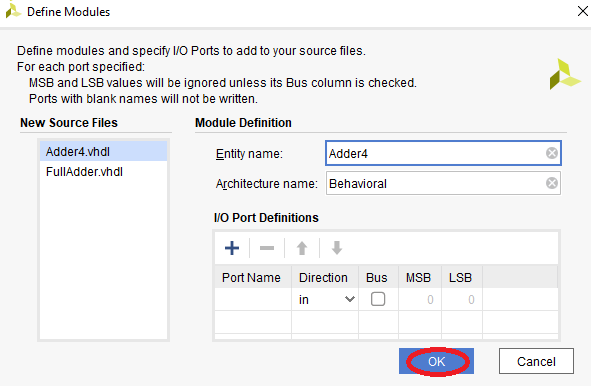

- Die Module definieren Dialog erscheint als nächstes. Wir werden hier nichts eingeben. Klicken Sie auf OK um dies zu schließen Sie werden gefragt, ob Sie diese Werte wirklich verwenden möchten. Klicken Sie auf Ja :

Abbildung 4.14 – Dialog Module definieren

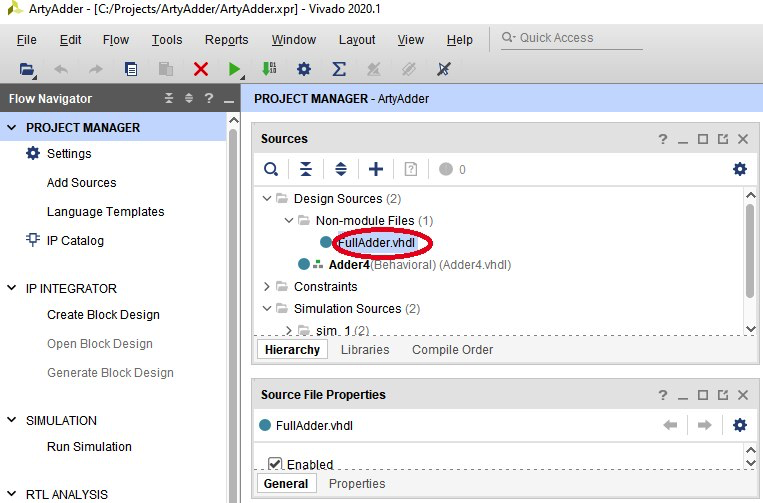

- Erweitern Sie die Nicht-Modul-Dateien unter Designquellen , und doppelklicken Sie dann auf FullAdder.vhdl. Es öffnet sich ein Editor-Fenster mit der leeren Datei FullAdder.vhdl:

Abbildung 4.15 – Neu erstellte Quelldatei

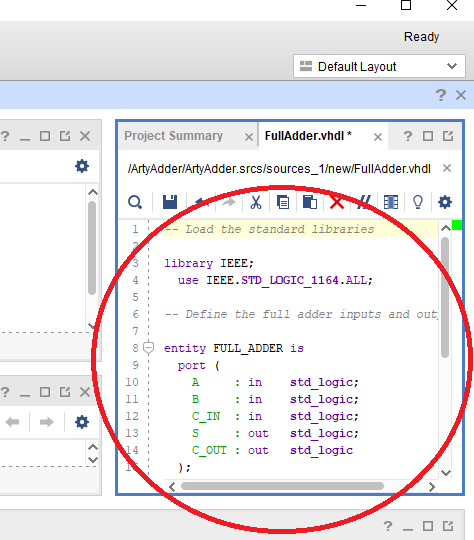

- Geben Sie den folgenden VHDL-Code in das FullAdder.vhdl-Editorfenster ein:

-- Laden Sie die Standardbibliothekenbibliothek IEEE; use IEEE.STD_LOGIC_1164.ALL;-- Definiere die vollständigen Addierer-Ein- und Ausgänge FULL_ADDER ist der Port ( A :in std_logic; B :in std_logic; C_IN :in std_logic; S :out std_logic; C_OUT :out std_logic );end Entity FULL_ADDER; -- Definiere das Verhalten der vollständigen Addiererarchitektur BEHAVIORAL von FULL_ADDER isbegin S <=(A XOR B) XOR C_IN; C_OUT <=(A UND B) ODER ((A XOR B) UND C_IN);Endarchitektur VERHALTEN;

Dies ist derselbe Single-Bit-Volladdierer-Code, den wir in den Hardware-Designsprachen untersucht haben Abschnitt von Kapitel 1, Architektur leistungsstarker eingebetteter Systeme . Abbildung 4.16 zeigt den Code im Vivado-Editorfenster:

Abbildung 4.16 – FullAdder.vhdl Quellcode

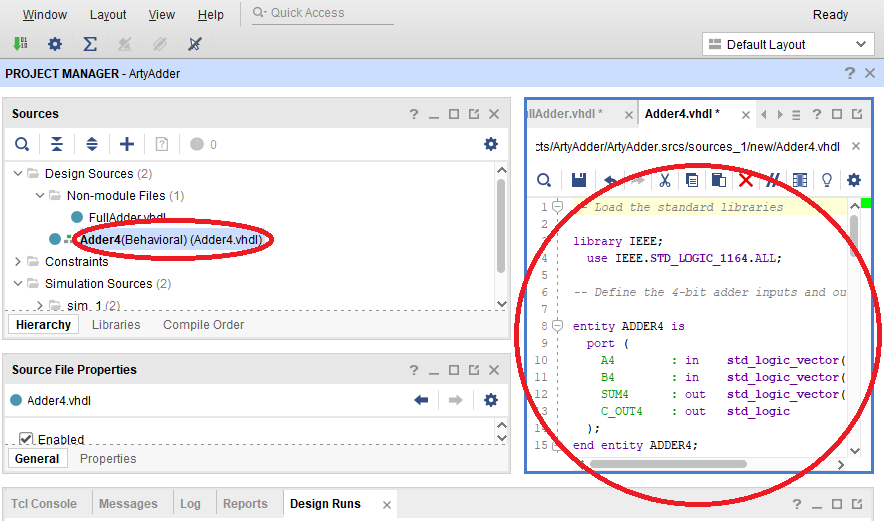

- Auf die gleiche Weise doppelklicken Sie auf Adder4(Verhalten) (Adder4.vhdl) unter Designquellen . Löschen Sie den automatisch ausgefüllten Inhalt der Adder4.vhdl Editor-Fenster und geben Sie den folgenden Code in die Adder4.vhdl ein Herausgeber:

-- Laden Sie die Standardbibliothekenbibliothek IEEE; use IEEE.STD_LOGIC_1164.ALL;-- Definiere die 4-Bit-Addierer-Ein- und Ausgänge ); C_OUT4 :out std_logic );Endeinheit ADDER4;-- Definieren Sie das Verhalten der 4-Bit-Adderarchitektur VERHALTEN von ADDER4 ist -- Verweisen Sie auf die vorherige Definition der Volladdiererkomponente FULL_ADDER is port ( A :in std_logic; B :in std_logic; C_IN:in std_logic; S:out std_logic; C_OUT:out std_logic); Endkomponente; -- Definieren Sie die intern verwendeten Signale im 4-Bit-Addierersignal c0, c1, c2 :std_logic;begin -- Der Übertragseingang zum ersten Addierer wird auf 0 gesetzt FULL_ADDER0 :FULL_ADDER Portmap ( A => A4(0), B => B4(0), C_IN => '0', S => SUM4(0), C_OUT => c0 ); FULL_ADDER1 :FULL_ADDER Portzuordnung ( A => A4(1), B => B4(1), C_IN => c0, S => SUM4(1), C_OUT => c1 ); FULL_ADDER2 :FULL_ADDER-Port-Map ( A => A4(2), B => B4(2), C_IN => c1, S => SUM4(2), C_OUT => c2 ); FULL_ADDER3 :FULL_ADDER Portmap ( A => A4(3), B => B4(3), C_IN => c2, S => SUM4(3), C_OUT => C_OUT4 );Endarchitektur BEHAVIORAL;

Dieser Code instanziiert vier Kopien des Einzelbit-Volladdierers. Der Übertrag in den niedrigstwertigen Addierer wird auf Null gesetzt und der Übertrag von jedem Addierer wellt sich zum nächsten höchstwertigen Addierer. Das Ergebnis der Addition zweier 4-Bit-Zahlen ist ein 4-Bit-Ergebnis und ein Einzel-Bit-Übertrag:

Abbildung 4.17 – Adder4.vhdl-Quellcode

Im nächsten Artikel erfahren Sie, wie Sie das Design testen und unser Design für das Arty-Board umsetzen.

Nachdruck mit Genehmigung von Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin ist CEO von Ledin Engineering, Inc. Jim ist ein Experte für Design, Entwicklung und Test von eingebetteter Software und Hardware. Er ist auch in der Cybersicherheitsbewertung von eingebetteten Systemen und in Penetrationstests versiert. Er hat einen B. S. Abschluss in Luft- und Raumfahrttechnik von der Iowa State University und einen M.S. Abschluss in Elektro- und Computertechnik vom Georgia Institute of Technology. Jim ist ein registrierter professioneller Elektroingenieur in Kalifornien, ein Certified Information System Security Professional (CISSP), ein Certified Ethical Hacker (CEH) und ein Certified Penetration Tester (CPT).

Jim Ledin ist CEO von Ledin Engineering, Inc. Jim ist ein Experte für Design, Entwicklung und Test von eingebetteter Software und Hardware. Er ist auch in der Cybersicherheitsbewertung von eingebetteten Systemen und in Penetrationstests versiert. Er hat einen B. S. Abschluss in Luft- und Raumfahrttechnik von der Iowa State University und einen M.S. Abschluss in Elektro- und Computertechnik vom Georgia Institute of Technology. Jim ist ein registrierter professioneller Elektroingenieur in Kalifornien, ein Certified Information System Security Professional (CISSP), ein Certified Ethical Hacker (CEH) und ein Certified Penetration Tester (CPT). Verwandte Inhalte:

- Embedded Design mit FPGAs:Hardwareressourcen

- Embedded Design mit FPGAs:Implementierungssprachen

- Embedded Design mit FPGAs:Entwicklungsprozess

- Open-Source-Tools vereinfachen die FPGA-Programmierung

- Implementierung von Gleitkomma-Algorithmen in FPGAs oder ASICs

- Einsatz von FPGAs für Deep Learning

- Softwaretools migrieren GPU-Code auf FPGAs für KI-Anwendungen

- FPGAs ersetzen ASICs in bildbasierten ADAS von Subaru Eyesight

Für mehr Embedded, abonnieren Sie den wöchentlichen E-Mail-Newsletter von Embedded.

Eingebettet

- Flüssige additive Fertigung:Erstellen von 3D-Objekten mit Flüssigkeit

- Was ist Embedded System Design:Schritte im Designprozess

- Umwandeln von Big Data in Smart Data mit eingebetteter KI

- Arrow Electronics startet europäischen FPGA-Entwicklerwettbewerb

- Design-Kit misst den Blutdruck mit optischem Sensor

- Defense FPGA-Debüts mit Early Access

- Roboter bauen mit Raspberry Pi und Python

- Einen Segway mit Raspberry Pi bauen

- GoPiGo v2 mit Windows IoT

- Alles drin mit Additiv