Grundlegende Gate-Funktion

Teile und Materialien

- 4011 Quad-NAND-Gatter (Radio Shack Katalog Nr. 276-2411)

- DIP-Schalter mit acht Positionen (Radio Shack Katalog # 275-1301)

- Zehn-Segment-Balkendiagramm-LED (Radio Shack Katalog # 276-081)

- Eine 6-Volt-Batterie

- Zwei 10 kΩ Widerstände

- Drei 470--Widerstände

Achtung! Der 4011 IC ist CMOS und daher empfindlich gegenüber statischer Elektrizität!

Weitere Lektüre

Lektionen in Stromkreisen , Band 4, Kapitel 3:„Logische Gatter“

Lernziele

- Zweck eines „Pulldown“-Widerstands

- So bestimmen Sie experimentell die Wahrheitstabelle eines Tors

- Wie man logische Gatter miteinander verbindet

- So erstellen Sie verschiedene logische Funktionen mithilfe von NAND-Gattern

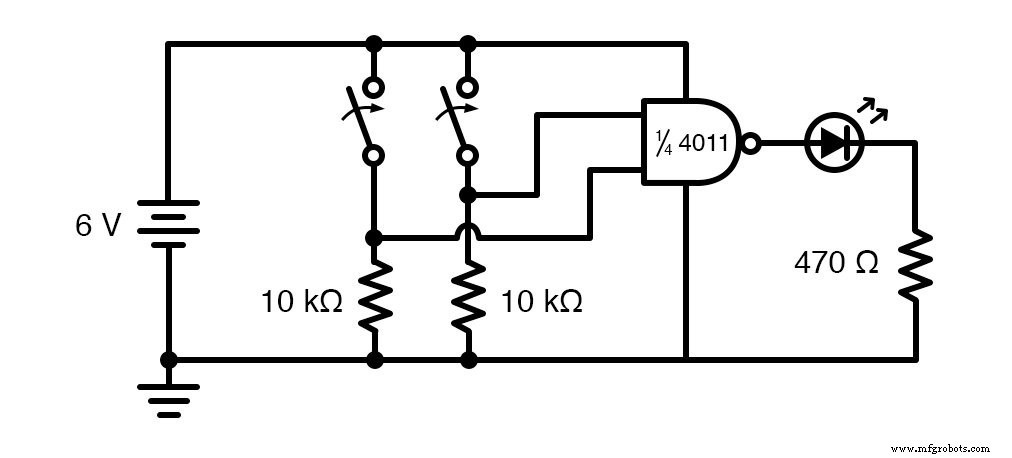

Schematische Darstellung der grundlegenden Gate-Funktion

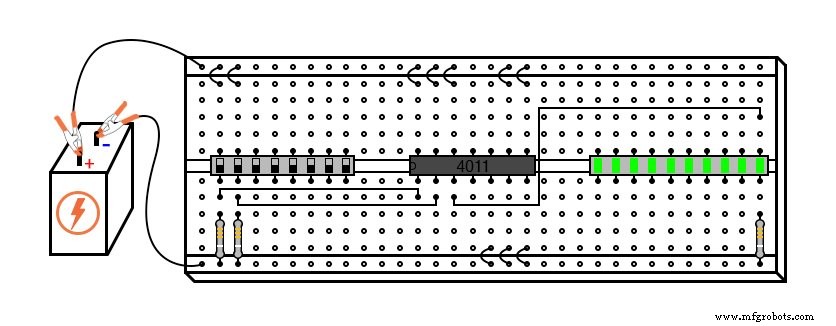

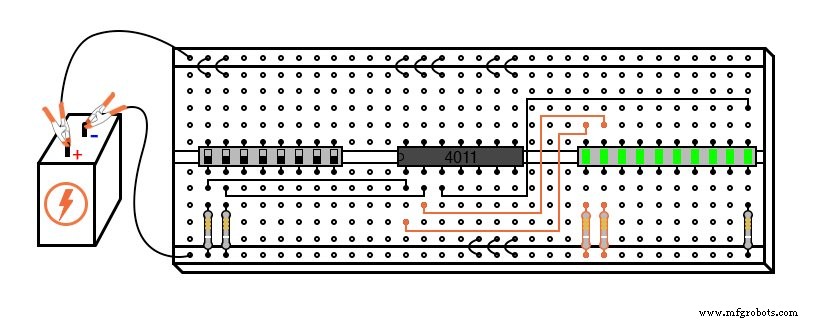

Illustration der grundlegenden Gate-Funktion

Experimentieranleitung

Verbinden Sie zunächst ein einzelnes NAND-Gatter mit zwei Eingangsschaltern und einer LED, wie gezeigt. Auf den ersten Blick mag die Verwendung eines 8-Positionen-Schalters und eines 10-Segment-LED-Balkendiagramms übertrieben erscheinen, da nur zwei Schalter und eine LED benötigt werden, um den Betrieb eines einzelnen NAND-Gatters anzuzeigen. Das Vorhandensein dieser zusätzlichen Schalter und LEDs macht es jedoch sehr bequem, die Schaltung zu erweitern und das Schaltungslayout sowohl sauber als auch kompakt zu gestalten.

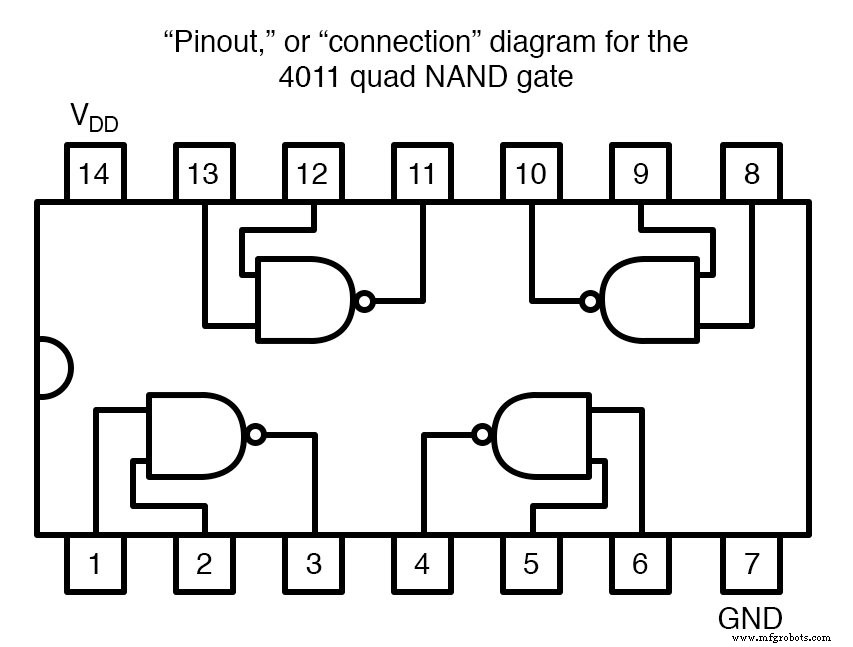

Es wird dringend empfohlen, ein Datenblatt für den 4011 zu haben Chip verfügbar, wenn Sie Ihre Schaltung bauen. Folgen Sie nicht nur der Abbildung oben! Es ist wichtig, dass Sie die Fähigkeit entwickeln, Datenblätter zu lesen, insbesondere „Pinbelegungsdiagramme“, wenn Sie IC-Anschlüsse mit anderen Schaltungselementen verbinden. Der Anschlussplan des Datenblatts ist eine wichtige Information. Hier gezeigt ist meine eigene Wiedergabe von 4011 Datenblatt zeigt:

In der Breadboard-Abbildung habe ich die Schaltung gezeigt, die mit dem unteren linken NAND-Gatter erstellt wurde:Pins 1 und 2 sind die Eingänge und Pin #3 ist der Ausgang. Die Pins 14 und 7 leiten Gleichstrom zu allen vier Gate-Schaltungen innerhalb des IC-Chips, „VDD ” steht für die positive Seite der Stromversorgung (+V) und „Gnd“ steht für die negative Seite der Stromversorgung (-V) oder Masse. Manchmal wird der negative Anschluss der Stromversorgung mit „VSS . beschriftet “ anstelle von „Gnd“ auf einem Datenblatt, aber es bedeutet dasselbe.

Digitale Logikschaltungen verwenden keine geteilten Stromversorgungen wie Operationsverstärker. Wie bei Operationsverstärkerschaltungen ist Masse jedoch immer noch der implizite Bezugspunkt für alle Spannungsmessungen. Wenn ich von einem „hohen“ Signal an einem bestimmten Pin des Chips sprechen würde, würde ich meinen, dass zwischen diesem Pin und der negativen Seite der Stromversorgung (Masse) die volle Spannung anliegt.

Beachten Sie, wie alle Eingänge der nicht verwendeten Gates innerhalb des 4011 Chip sind entweder mit VDD . verbunden oder Boden. Dies ist kein Fehler, sondern eine bewusste Absicht. Seit dem 4011 ist eine integrierte CMOS-Schaltung, und die Eingänge der CMOS-Schaltung bleiben unverbunden (floating ) kann jeden beliebigen Spannungspegel annehmen, lediglich durch das Abfangen einer statischen elektrischen Ladung von einem nahegelegenen Objekt. Die Eingänge schwebend zu lassen bedeutet, dass diese ungenutzten Gates beliebige Kombinationen von „High“- und „Low“-Signalen empfangen können.

Warum ist das unerwünscht, wenn wir diese Tore nicht benutzen? Wen interessiert es, welche Signale sie erhalten, wenn wir nichts mit ihren Ausgängen tun? Das Problem besteht darin, dass, wenn statische Spannungssignale an den Gate-Eingängen auftreten, die nicht vollständig „high“ oder vollständig „low“ sind, die internen Transistoren der Gates möglicherweise beginnen, sich so einzuschalten, dass sie übermäßigen Strom ziehen. Dies kann im schlimmsten Fall zu einer Beschädigung des Chips führen.

Im besten Fall bedeutet es übermäßigen Stromverbrauch. Es spielt keine Rolle, ob wir diese ungenutzten Gate-Eingänge „high“ (VDD ) oder „low“ (Masse), solange wir sie mit einem dieser beiden Orte verbinden. In der Breadboard-Abbildung zeige ich alle oberen Eingänge, die mit VDD . verbunden sind , und alle unteren Eingänge (der unbenutzten Gates) mit Masse verbunden. Dies geschah nur, weil die Löcher der Stromversorgungsschiene näher waren und keine langen Überbrückungsdrähte erforderlich waren!

Bitte beachten Sie, dass keiner der ungenutzten Gate-Ausgänge wurden mit VDD . verbunden oder Boden, und das aus gutem Grund! Wenn ich das tun würde, könnte ich ein Gate zwingen, den entgegengesetzten Ausgangszustand anzunehmen, den es erreichen möchte, was eine komplizierte Art ist, zu sagen, dass ich einen Kurzschluss verursacht hätte. Stellen Sie sich ein Gatter vor, das einen „hohen“ Logikpegel ausgeben soll (bei einem NAND-Gatter wäre dies der Fall, wenn einer seiner Eingänge „niedrig“ wäre).

Wenn der Ausgangsanschluss eines solchen Gates direkt mit Masse verbunden wäre, könnte es niemals einen "High"-Zustand erreichen (durch die Überbrückungsdrahtverbindung elektrisch mit Masse verbunden). Stattdessen würde sein oberer (P-Kanal-)Ausgangstransistor vergeblich eingeschaltet werden und den maximalen Strom an eine nicht vorhandene Last liefern. Dies würde sehr wahrscheinlich das Tor beschädigen! Gate-Ausgangsanschlüsse erzeugen von Natur aus ihre eigenen Logikpegel und „schweben“ nie auf die gleiche Weise wie CMOS-Gate-Eingänge.

Die beiden 10 kΩ-Widerstände sind in der Schaltung platziert, um schwebende Eingangsbedingungen am verwendeten Gate zu vermeiden. Bei geschlossenem Schalter wird der jeweilige Eingang direkt mit VDD . verbunden und deshalb „hoch“ sein. Bei geöffnetem Schalter werden die 10 kΩ „Pulldown ”-Widerstand stellt eine ohmsche Verbindung zur Masse her und gewährleistet einen sicheren „Low“-Zustand am Eingangsanschluss des Gates. Auf diese Weise ist der Eingang nicht anfällig für statische Streuspannungen.

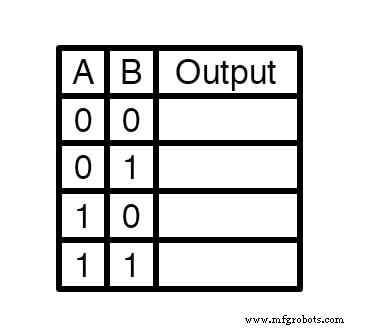

Wenn das NAND-Gatter wie abgebildet mit den beiden Schaltern und einer LED verbunden ist, können Sie eine „Wahrheitstabelle“ für das NAND-Gatter entwickeln. Auch wenn Sie bereits wissen, wie eine NAND-Gatter-Wahrheitstabelle aussieht, ist dies eine gute Experimentierübung:die Verhaltensprinzipien einer Schaltung durch Induktion zu entdecken. Zeichne eine Wahrheitstabelle wie folgt auf ein Blatt Papier:

Das „A“ und "B" Spalten repräsentieren jeweils die beiden Eingangsschalter. Wenn der Schalter eingeschaltet ist, ist sein Zustand „high“ oder 1. Wenn der Schalter ausgeschaltet ist, ist sein Zustand „low“ oder 0, wie durch seinen Pulldown-Widerstand sichergestellt. Der Ausgang des Gates wird natürlich durch die LED dargestellt:ob sie leuchtet (1) oder nicht leuchtet (0). Nachdem Sie die Schalter in jede mögliche Kombination von Zuständen gebracht und den Status der LEDs aufgezeichnet haben, vergleichen Sie die resultierende Wahrheitstabelle mit der Wahrheitstabelle eines NAND-Gates.

Wie Sie sich vorstellen können, ist diese Steckplatinenschaltung nicht auf das Testen von NAND-Gattern beschränkt. Jeder Gate-Typ kann mit zwei Schaltern, zwei Pulldown-Widerständen und einer LED zur Anzeige des Ausgangsstatus getestet werden. Überprüfen Sie einfach das „Pinout“-Diagramm des Chips, bevor Sie ihn Pin für Pin anstelle des 4011 ersetzen . Nicht alle „Quad“-Gate-Chips haben die gleiche Pinbelegung!

Zusätzliche Verbesserung

Eine Verbesserung, die Sie an dieser Schaltung vornehmen möchten, besteht darin, zusätzlich zu der einen LED, die den Ausgang anzeigt, einige LEDs zur Anzeige des Eingangsstatus zuzuweisen. Dies macht den Betrieb etwas interessanter zu beobachten und hat den weiteren Vorteil, anzuzeigen, wenn ein Schalter nicht geschlossen (oder geöffnet) wird, indem wahr angezeigt wird Eingangssignal an das Gate, anstatt Sie zu zwingen, den Eingangsstatus aus der Schalterposition abzuleiten:

VERWANDTES ARBEITSBLATT:

-

Grundlegendes Arbeitsblatt für Logikgatter

Industrietechnik