Einschaltphasendeterminismus:PLL-Synthesizer und Kalibrierung auf Systemebene

Im ersten Teil dieser Artikelserie haben wir untersucht, wie man eine bekannte (deterministische) Phase für alle Kanäle innerhalb von Chips erreicht, die mit mehreren digitalen Signalverarbeitungsblöcken (DSP), Breitband-Digital-Analog-Wandlern (DACs) und Breitband-Analog-Modulen integriert sind -zu-Digital-Wandler (ADCs). Wir begannen mit einem High-Level-Systemblockdiagramm unter Verwendung einer Subarray-Taktbaumstruktur und beschrieben ein Multichip-Synchronisationsverfahren. In diesem zweiten Teil werden wir die Phasenanpassungen des PLL-Synthesizers, die Skalierbarkeit auf mehrere Subarrays und Kalibrierungsalgorithmen auf Systemebene untersuchen.

PLL-Synthesizer-Phasenanpassungen

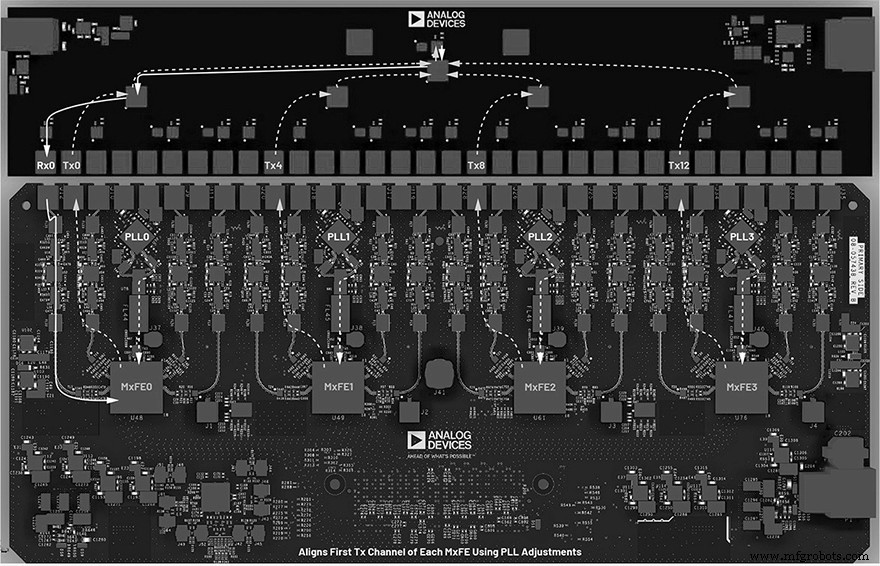

Die ausgewählten PLL-Synthesizer-ICs wurden ausgewählt, um relative Abtasttaktphaseneinstellungen zu ermöglichen, die in jeden Digitalisierer-IC eingespeist werden. Die thermische Drift und die daraus resultierende PLL-Phasendrift zwischen dem Abtasttakt und dem SYSREF jedes ICs wird kompensiert, indem ein Rückkopplungsmechanismus geschaffen wird, der sicherstellt, dass der erste Sendekanal jedes Digitizer-ICs phasenabgleich mit dem ersten Sendekanal des ersten Digitizer-ICs ausgerichtet ist. Um diese Rückkopplungsschleife zu erreichen, gibt der erste Sendekanal jedes ICs ein Signal aus, das sich von den anderen Sendekanälen unterscheidet, wie in Abbildung 1 gezeigt. Diese vier Signale werden kombiniert und an einen gemeinsamen Empfänger gesendet, der für dieses System mit Rx0 . bezeichnet ist .

Klicken für Bild in voller Größe

Abbildung 1. Eine PLL-Synthesizer-Phasenanpassungsfunktion ermöglicht die Ausrichtung des ersten Sendekanals jedes Digitizer-ICs über das Subarray. (Quelle:Analog Devices)

Gleichzeitige Empfangsdaten werden für alle Empfangskanäle erhalten, wodurch Benutzer Kreuzkorrelationstechniken anwenden und die komplexen Phasenverschiebungen zwischen diesen vier Sendekanälen bestimmen können, ΦTxOffset . Die PLL-Synthesizer-ICs enthalten einen spannungsgesteuerten Oszillator (VCO), der mit einer Frequenz ƒ . arbeitet VCO_PLL .

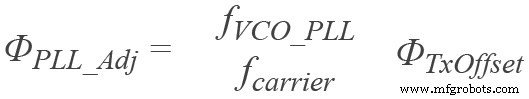

Die gemessenen Phasenverschiebungen ΦTxOffset beziehen sich dann auf die erforderliche PLL-Phasenanpassung ΦPLL_Adj und die HF-Frequenz ƒ Träger so dass:

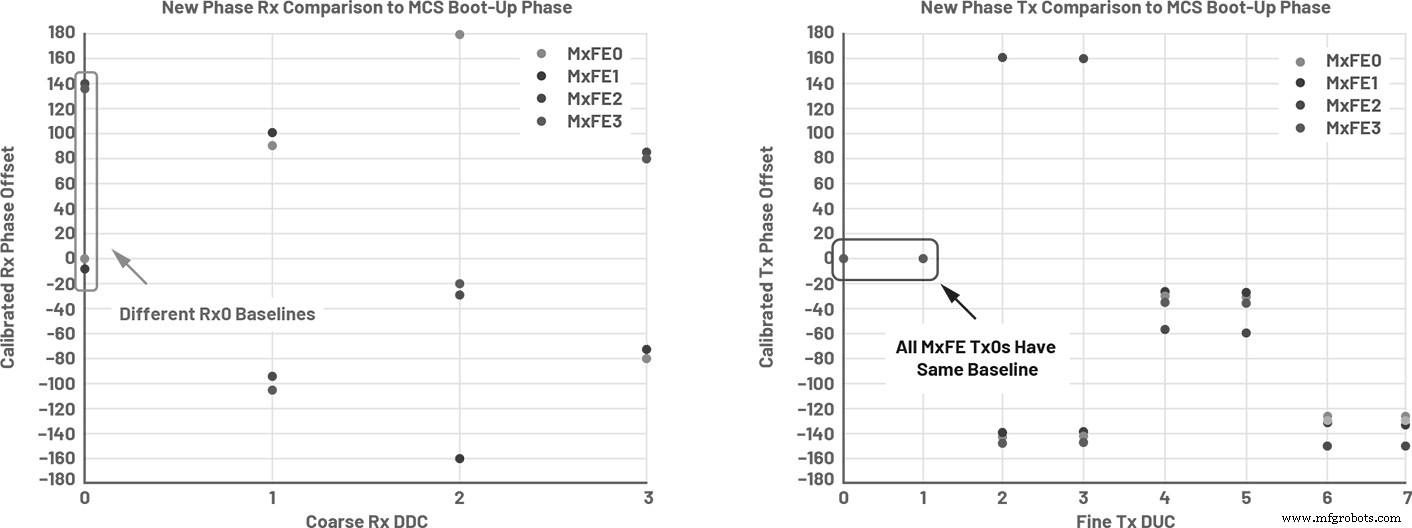

Mit dieser Formel können die PLL-Synthesizer-Phasen um einen neuen bekannten Betrag angepasst werden, um eine gemeinsame Sendebasislinie zwischen allen Digitizer-ICs für alle Leistungszyklen zu erstellen, wie in Abbildung 2 gezeigt. Die offenen Kreise für jeden Kanal in Abbildung 2 entsprechen den ersten Leistungszyklus, wohingegen alle anderen ausgefüllten Punkte nachfolgenden Leistungszyklen entsprechen. Wie aus dieser Figur ersichtlich ist, sind die kalibrierten Sendephasen-Offsets für den ersten (und zweiten) Kanalisierer aller Digitalisierer-ICs phasenausgerichtet. Der zweite Kanalisierer jedes Digitalisierer-ICs ist auch in diesem Fall ausgerichtet, da für jeden DAC im System zwei Kanalisierer verwendet werden.

Das Hinzufügen dieses Phasenanpassungsschritts des PLL-Synthesizers vor den im vorherigen Abschnitt besprochenen MCS-Routinen erzeugt dadurch eine deterministische Phase über alle induzierten thermischen Gradienten innerhalb des Systems, indem das System in die gleiche Sample-Takt-SYSREF-Phasenbeziehung gezwungen wird, die sich als eine Übertragung manifestiert Ausrichtungsbasislinie über alle Digitizer-ICs.

Klicken für Bild in voller Größe

Abbildung 2. Durch Einstellen der PLL-Phase kann der Benutzer den ersten Sendekanal aller Digitizer-ICs ausrichten. (Quelle:Analog Devices)

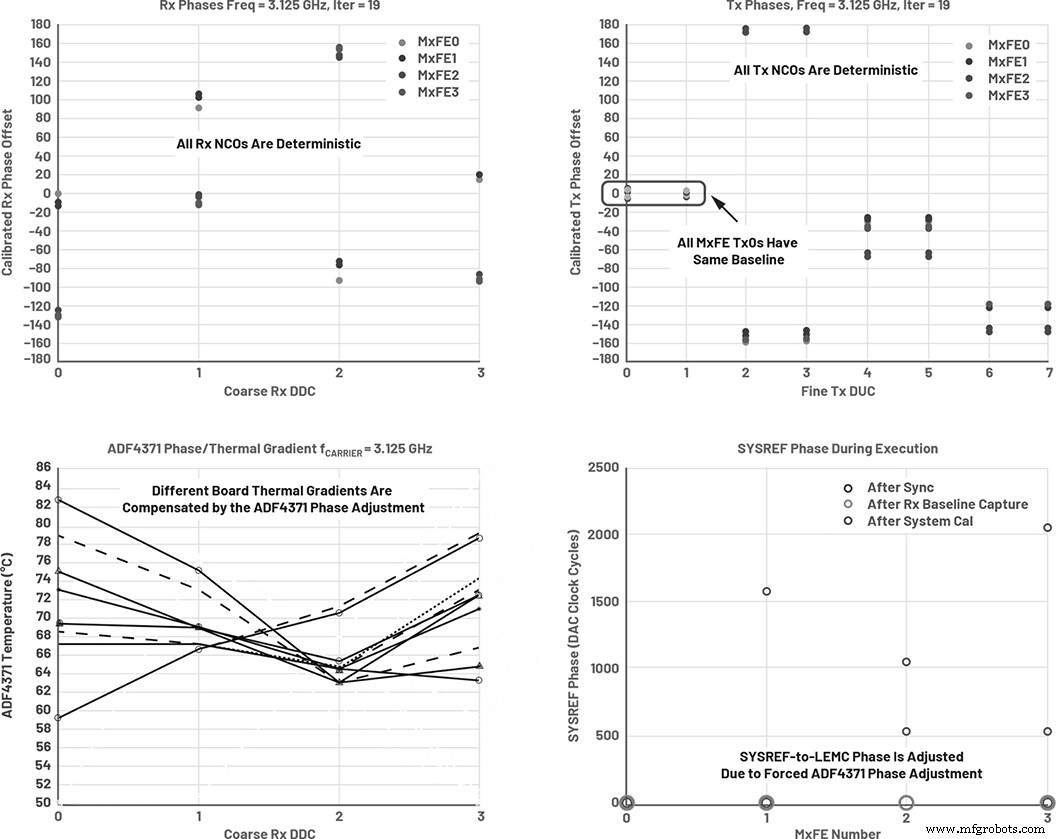

Abbildung 3 zeigt, dass über die Temperaturmesseinheit (TMU) auf jedem PLL-Synthesizer-Chip ein induzierter Temperaturgradient erfasst werden kann. Wie aus der blauen Kurve unten links in Abbildung 3 ersichtlich ist, wurden absichtlich stark unterschiedliche Temperaturen auf der Plattform durch die Anwendung unterschiedlicher Lüfterluftströme auf das System induziert. Die Verwendung der PLL-Phasenanpassung für jeden IC zeigt jedoch, dass unabhängig vom auf die Platine aufgebrachten Luftstrom die kalibrierten NCO-Phasenoffsets für jeden Empfangs- und Sendekanal deterministisch sind, wenn erzwingt, dass der erste Sendekanalisierer jedes Digitalisierer-ICs auf jeden abgestimmt wird andere. Dies wird durch die Beobachtung der dichten Ansammlung von Punkten derselben Farbe auf den oberen beiden Diagrammen in Abbildung 3 trotz der unterschiedlichen Wärmegradienten, die während verschiedener Einschaltzyklen auf die Platine angewendet werden, deutlich.

Klicken für Bild in voller Größe

Abbildung 3. Die in Verbindung mit der PLL-Phasenanpassungsfunktion verwendete MCS-Funktion demonstriert den Einschaltphasen-Determinismus für alle Empfangs- und Sendekanäle, unabhängig vom auf der Plattform induzierten Wärmegradienten. (Quelle:Analog Devices)

Unten rechts in Abbildung 3 sind die abgefragten Digitalisierer-IC-Register dargestellt, die die gemessene SYSREF-LEMC-Phasenbeziehung nach Anwendung des PLL-Synthesizer-Phasenoffsets zeigen. Beachten Sie anhand der orangefarbenen Spuren in der unteren linken Darstellung, dass die Phasenanpassungen des PLL-Synthesizers alle gemessenen SYSREF-Phasen ungleich Null, die aus einem anderen induzierten Temperaturgradienten resultieren, vollständig kompensieren.

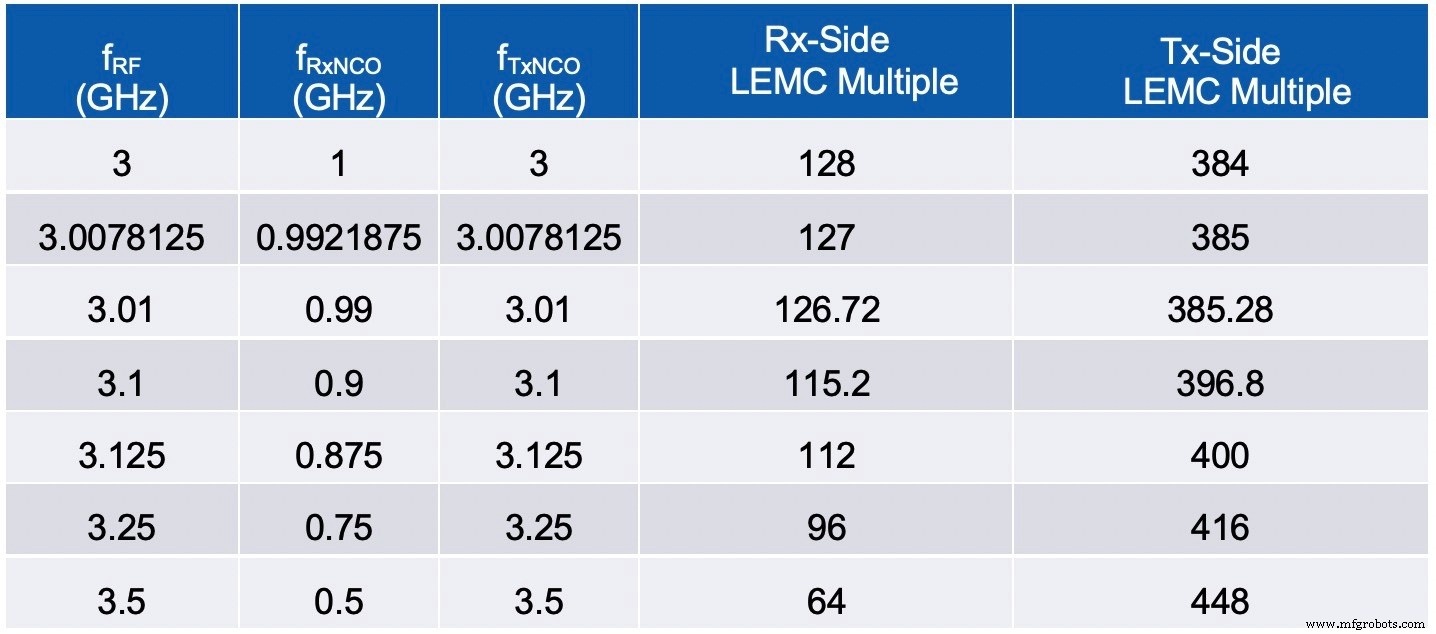

Es wurden viele Frequenzen gemessen, die alle eine deterministische Empfangs- und Sendephase zeigen. Die für diesen Artikel ausgewählten spezifischen Frequenzen sind in Abbildung 4 dargestellt und wurden so gewählt, dass MCS über viele induzierte thermische Gradienten demonstriert wird, wenn nicht ganzzahlige Vielfache des Referenztakts oder des LEMC verwendet werden.

Abbildung 4. Die in diesem Artikel verwendeten HF-Frequenzen wurden ausgewählt, um die MCS-Funktionen über einen weiten Bereich von Taktquellen zu demonstrieren, einschließlich nicht ganzzahliger Vielfacher des Referenztakts und des LEMC. (Quelle:Analog Devices)

Skalierbarkeit auf mehrere Subarrays

Die in diesem Artikel gezeigten Daten konzentrieren sich hauptsächlich auf die MCS-Leistung auf Subarray-Ebene, aber es muss auch sichergestellt werden, dass diese Synchronisierungsfunktionen auf der größeren Array-Ebene und über mehrere Subarrays hinweg realisierbar sind. Um dieses höhere Synchronisationsniveau zu erreichen, ist ein Taktbaum auf Array-Ebene erforderlich, um sicherzustellen, dass die SYSREF-Anforderungen an jedes in Abbildung 1 in Teil 1 gezeigte Subarray synchron am Taktpuffer-IC jedes Subarrays ankommen. Wenn dieses Kriterium gegeben ist, kann dann jedes Unterarray die erforderlichen SYSREFs und BBP-Takte ausgeben, wie zuvor beschrieben, so dass diese Signale an den Unterarray-Digitalisierer-ICs und BBP innerhalb des gleichen Abtasttaktzyklus über das größere Array ankommen. Dieser Taktbaum auf Array-Ebene erfordert, dass die Taktverteilung an jedes Unterarray die Verzögerungsanpassungsblöcke besitzt, die notwendig sind, um eine synchrone SYSREF-Anforderungsverteilung an jeden der untergeordneten Unterarray-Taktchip-ICs zu erreichen. Auf diese Weise werden mehrere BBPs, die mit mehreren Subarrays verbunden sind, letztendlich synchronisiert.

Kalibrierungsalgorithmus auf Systemebene

Während die in den vorherigen Abschnitten gezeigten MCS-Algorithmen eine deterministische Phase beim Einschalten für jeden Empfangs- und Sendekanal bereitstellen, sind diese Phasen aufgrund von Unterschieden in den HF-Front-End-Tracelängen zwischen den Kanälen nicht unbedingt über alle Kanäle innerhalb der HF-Domäne phasenausgerichtet . Obwohl die MCS-Algorithmen den Array-Kalibrierungsprozess tatsächlich vereinfachen, besteht daher immer noch die Notwendigkeit, sich einer Kalibrierungsroutine auf Systemebene zu unterziehen, um die Phasen jedes HF-Kanals innerhalb des Systems auszurichten.

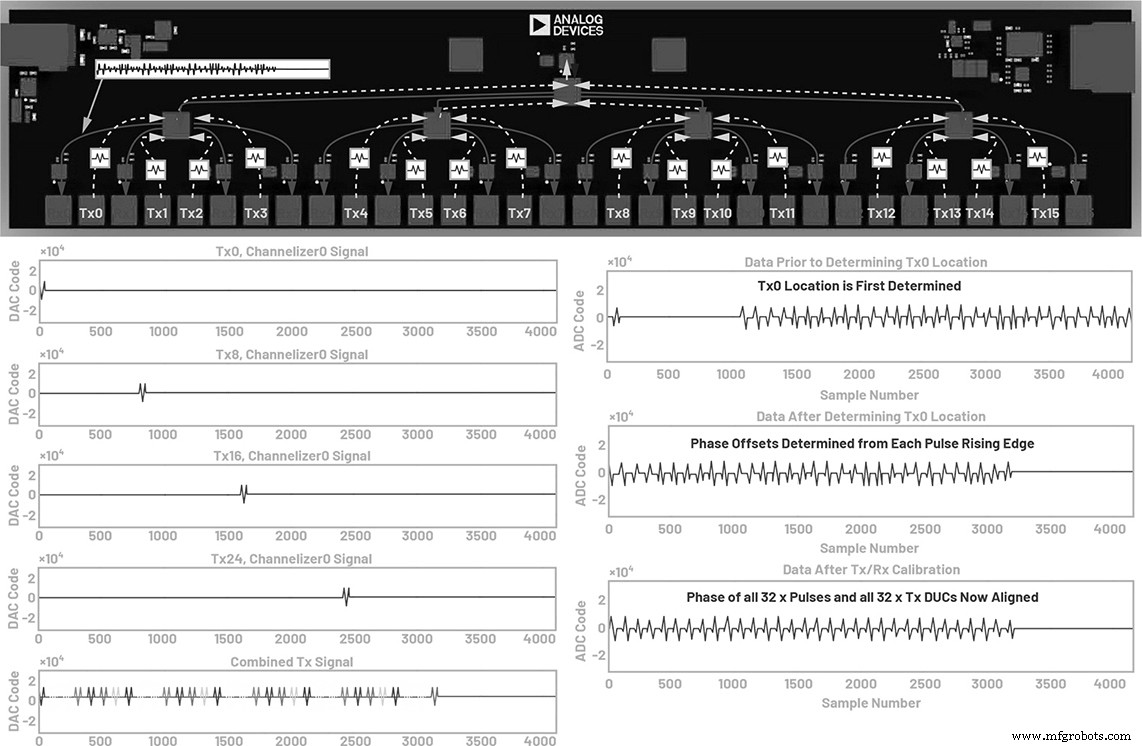

Es ist daher notwendig, zusätzlich zur Durchführung der MCS-Algorithmen einen effizienten Kalibrierungsalgorithmus auf Systemebene zu entwickeln. Die Kalibrierungsmethode auf Systemebene für diesen Artikel verwendet eine bestimmte Basisband-Wellenform und ist vollständig eigenständig, ohne dass externe Geräte erforderlich sind. Das in diesem Artikel beschriebene System ist in der Lage, in jeden Channelizer auf der Plattform separate Basisbandwellenformen einzuspeisen. Unter Ausnutzung dieser Fähigkeit wird eine Basisbandwellenform, die aus einem Impuls einer Periode für jeden Sendekanalisierer besteht, in das Subarray eingespeist, wie unten links in Abbildung 5 gezeigt. Jeder Sendekanalisierer gibt daher nur einen Impuls aus. Die Wellenformen sind jedoch über alle Sendekanalisierer gestaffelt, so dass im gesamten System jeweils nur ein Impuls einer Periode ausgegeben wird. Die Ausgabe aller Sendekanalisierer wird innerhalb der HF-Domäne kombiniert und dann aufgeteilt und in alle Empfangskanäle zurückgesendet, wie oben in Abbildung 5 gezeigt. Schließlich wird eine gleichzeitige Empfangsdatenerfassung für alle Empfangskanäle durchgeführt und die Daten werden gespeichert zu einer 4096×16-Matrix, wobei 4096 die Samplegröße ist, die für alle 16 Empfangskanäle gesammelt wurde.

Klicken für Bild in voller Größe

Abbildung 5. Ein Kalibrierungsalgorithmus auf Systemebene wird in Verbindung mit MCS verwendet, um eine schnelle Ausrichtung aller Empfangs- und Sendekanäle im System zu erreichen. (Quelle:Analog Devices)

Diese Daten werden dann vertikal entlang der ersten Spalte (entsprechend Rx0) analysiert, um den Tx0-Kanalisiererimpuls zu lokalisieren, wie im oberen Teildiagramm unten rechts in Abbildung 5 gezeigt. Nachdem der Tx0-Impuls identifiziert wurde, sind alle anderen Impulspositionen bekannt und die komplexe Phase der ansteigenden Flanke jedes Impulses wird berechnet und in einem 1 × 16-Vektor gespeichert, der den gemessenen Phasenverschiebungen entspricht, die an allen Sendekanälen im gesamten System vorhanden sind. Mit diesem Wissen und unter Verwendung von Tx0 als Basislinienreferenz werden die komplexen Phasen aller Sendekanäle dann basierend auf den gemessenen Offsets modifiziert.

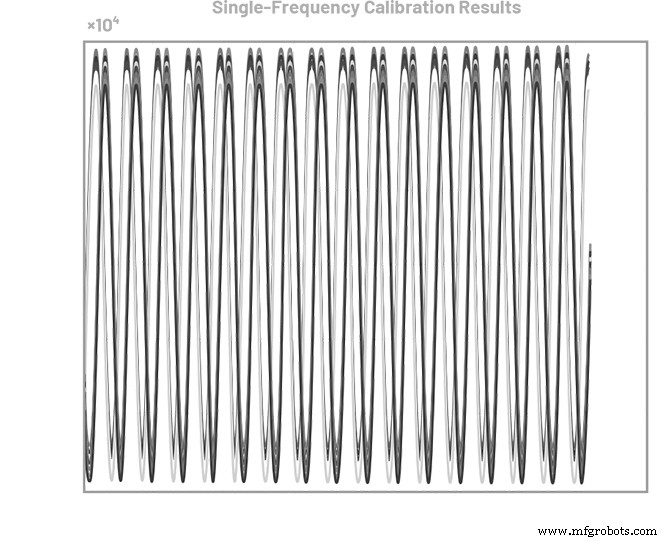

Da das gleiche kombinierte Signal an alle Empfangskanäle gesendet wird, werden die Daten in ähnlicher Weise horizontal entlang der Matrix analysiert (über alle Empfangskanäle hinweg). Die komplexen Phasen aller Empfangskanäle werden dann in Bezug auf Rx0 gemessen und in einem 1 × 16-Vektor gespeichert, der den im System vorhandenen gemessenen Empfangsphasen-Offsets entspricht. Die komplexen Empfangs-NCO-Phasen werden dann im gesamten Subarray angepasst, um alle Kanäle in Bezug auf Rx0 phasenauszurichten, wie durch die gleichphasigen (I) und quadraturphasigen (Q) ADC-Codes für alle 16 Empfangskanäle in Abbildung 6 gezeigt. Es ist anzumerken, dass, während das Diagramm in Fig. 6 alle Kanäle phasenabgleich ausrichtet, es nicht notwendigerweise alle Kanäle amplitudenabgleicht. Mit den Finite-Impulse-Response-(FIR-)Filtern auf dem Chip, die jetzt auf diesen Digitizer-ICs vorhanden sind, könnte man jedoch alternativ eine Amplituden- und Phasenausrichtung über die Kanäle hinweg erreichen, ohne leistungshungrige FPGA-Ressourcen zuweisen zu müssen, um das gleiche Ergebnis zu erzielen.

klicken Sie für das Bild in voller Größe

Abbildung 6. 16-Kanal-Empfangs-I&Q-Phasenabgleich wird mit Hilfe von MCS und einem eigenständigen Kalibrierungsalgorithmus auf Systemebene erreicht. (Quelle:Analog Devices)

Dieser Kalibrierungsalgorithmus auf Systemebene wird derzeit in MATLAB ® . erreicht und dauert ungefähr drei Sekunden. Bei Implementierung in Hardwarebeschreibungssprache (HDL) kann diese Kalibrierungszeit jedoch weiter reduziert werden, während ein vollständig eigenständiger Algorithmus beibehalten wird. Wenn die Systemfrequenz und -amplitude beim Hochfahren bekannt sind, können Benutzer außerdem Phasenverschiebungswerte aus einer Nachschlagetabelle laden, indem sie sich auf die MCS-Algorithmen verlassen, anstatt die in dieser Kalibrierungsmethode auf Systemebene beschriebenen Messungen durchführen zu müssen. In diesem Fall kann die Kalibrierungsmethode auf Systemebene verwendet werden, um die während einer Werkskalibrierung in einer Nachschlagetabelle gespeicherten Phasenverschiebungen aufzufüllen.

Schlussfolgerung

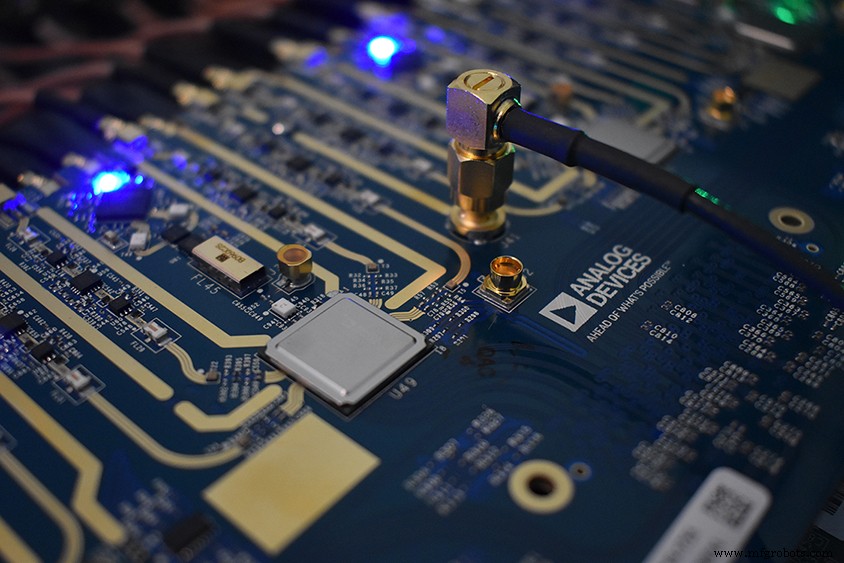

Ein erfolgreicher MCS-Prozess wurde mit vier AD9081 MxFETM-ICs von Analog Devices als Rückgrat des Subarrays demonstriert. Thermische Gradienten über die Plattform werden mit Hilfe von Phasenanpassungsblöcken innerhalb von vier ADF4371 PLL-Synthesizern kompensiert. Ein Takt-IC HMC7043 wird verwendet, um die für die JESD204C-Schnittstelle erforderlichen SYSREFs und BBP-Takte zu verteilen. MCS-Algorithmen im AD9081 ermöglichen vereinfachte Kalibrierungen auf Systemebene und bieten eine deterministische Einschaltphase für mehrere im System vorhandene Frequenzen und thermische Gradienten. Außerdem wird ein effizienter Kalibrierungsalgorithmus auf Systemebene vorgestellt, der verwendet wird, um LUTs während der Werkskalibrierung zu bestücken und daher die Systemstartzeit drastisch reduziert. Diese Plattform ist in Abbildung 7 dargestellt und wird als Quad-MxFE bezeichnet. Das System kann bei Analog Devices erworben werden. Diese Arbeit ist für jedes Mehrkanalsystem relevant, das in einem Phased-Array-Radar, elektronischer Kriegsführung, Instrumentierung oder 5G-Plattform vorhanden ist.

Abbildung 7. Die Quad-MxFE-Plattform ist bei Analog Devices erhältlich. (Quelle:Analog Devices)

Referenzen

1 Del Jones. „JESD204C Primer:Was ist neu und für Sie drin – Teil 1.“ Analoger Dialog , Bd. 53, Nr. 2, Juni 2019.

2 Del Jones. „JESD204C Primer:Was ist neu und für Sie drin – Teil 2.“ Analoger Dialog , Bd. 53, Nr. 3, Juli 2019.

Eingebettet

- 3 Gründe, warum DevOps und Cloud einander brauchen; DevCloudOps

- Vektoren und AC-Wellenformen

- Frequenz- und Phasenmessung

- Strukturen und Klassen in C++

- Postfächer:Einführung und grundlegende Dienste

- Semaphoren:Einführung und grundlegende Dienste

- Warteschlangen:Einführung und grundlegende Dienste

- Immersive Videos, KI und die nächste Phase der Technologiegestaltung des Einzelhandels

- Hartdrehen und Rundschleifen wurden füreinander geschaffen

- Häufige Arten von Fräsmaschinen und wann sie verwendet werden